Цифровое устройство для управления ведомым сетью преобразователем

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может быть использовано в статических преобразователях. Цель изобретения - улучшение динамических характеристик и повышение надежности. За счет введения в устройство для управления преобразователем фиксатора нулевого значения, регистров кодов фазового сдвига 21i-21, мультиплексора кодов фазового сдвига 17, регистра базового адреса 18, сумматора 19 и блоков задержки записи кода фазового сдвига 22:-22 обеспечивается надежная работа устройства в динамических режимах , когда фазовая задержка импульсов значительно изменяется в течение одного гериода частоты сети. 2 ил. S (Л 00 00 О5 а оо /

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1381668

А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPGKOMY СВИДЕТЕЛЬСТВУ

1у

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4036688/24-07 (22) 17.03.86 (46) 15.03.88. Бюл. № 10 (71) Уфимский авиационный институт им. Серго Орджоникидзе (72) О. Л. Рыжиков, А. В. Никитин, В. И. Шарабыров и В. Ю. Карнов (53) 621. 316. 727 (088. 8) (56) Авторское свидетельство СССР № 1184060, кл. Н 02 М 7/00, 1985.

Авторское свидетельство СССР № 1261071, кл. Н 02 М 7/00, 1986. др 4 Н 02 М 7 00 ф. Ц т)%-><" Я (54) ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ

УПРАВЛЕНИЯ ВЕДОМЫМ СЕТЪЮ ПРЕОБРАЗОВАТЕЛ ЕМ (57) Изобретение относится к электротехнике и может быть использовано в статических преобразователях. Цель изобретения — улучшение динамических характеристик и повышение надежности. 3а счет введения в устройство для управления преобразователем фиксатора нулевого значения, регистров кодов фазового сдвига 2li — 21„, мультиплексора кодов фазового сдвига 17, регистра базового адреса 18, сумматора 19 и блоков задержки записи кода фазового сдвига 22 — 22„обеспечивается надежная работа устройства в динамических режимах, когда фазовая задержка импульсов значительно изменяется в течение одного гериода частоты сети. 2 ил.

1381668

ИзобрсTcнис относится к электрот xt!HK«, а именно к системам управления тиристорными преобразоват«лями, и можст найти прим(и«!ис B hB÷åñãв«блока управлсния преобразов,!тслсй, ведомых сетью.

1(ечь изобретения улучшение динами ческих характеристик и повышени«надежности раб<) гы x «« рой«тва.

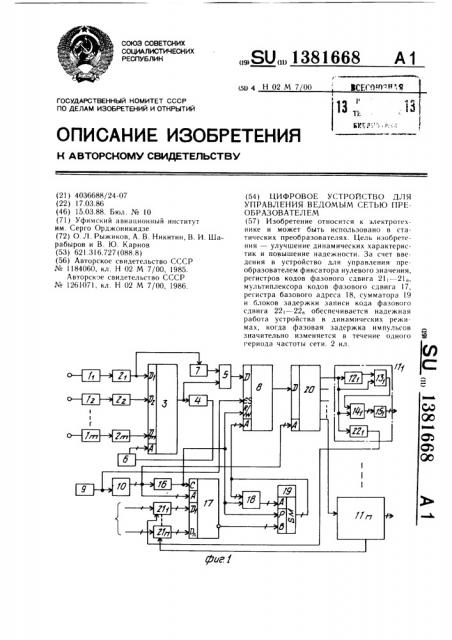

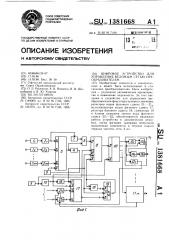

На фи!. 1 представлена структурная схема устройства: п,(фиг. 2 -- полс яч< K

0!le f)dTEtBtE0f >апомп ающегс) блока

У«трои«TBO c().tc рн ит llo числу фаз tiki (<3K)<» )и с«тit ф»Г!>гр!.! 1,1 I ш, входы которых

НР(, подклк)чены к входал< нуль-органов 2,1...2ш, выходами пс>дклк)ченных и информационным входам мульги .Нксора 3, к выходу кочоро(о подклн>ч«ны жду п(ии мул ьгивибра гор 4 Ei псрвый Вход э.ч< x«sir;3 И!И 5, выход ждуl l! e (0 )1 у л ь т >t E s Et t);); E т О р а 4 и Од к;! к) ч с и h В х О!1 л счстчика tsOM(р;1 фазы преобразовагс.чя 6, выход которого и<.lh,!К) си к адресно!1 и!и!3с мультиплексора 3, «двиговый ре(ис(р шиф рации 7, Вход KOI !>(>OI o полключсft к Вl,(хО лу ну.lh (if)(HH lу э.!«Мен Гlxnл h0 <; рого подклк>чеfi к !>Нформационнол(у >холу

Оперативпог(>:s sit()!It(«I 0 блока t(, гс пс р(х It )I It ) 11>((>B (), 1>Ы ход h! ) 1 n(>0(!, lrr)1h, itr)(iC EI i, (х (л Вь б< Iihп Опс (i ГEII!IH)l (!почин-<н>пс! I > б.!Окс (чик; ! Омс tid гit()lt((О!i!IOI (> lj)(r!C> f)<1 30(>с(!х l,!1,1), НО !пслу I п(ч (.<>рОВ <лы ((,Орл<»рО(;-HIHH ш lхо,iiiE>ix и ll .!I c()B 11, «Одс р.+.;!!ци« .,а/ксип «."t) ()В(,, Ii! I ll("1! Н! п. шифраци!(! 2, :л! 1; I! It>l !! 1 . (!«(Чик помер<> !»рп«т(°

1;i ! и (><)рм (р i E:;ь «двое н! !х ил>

<(уль«>В 1:, s!x «л!3!>! cil<010 ??(! ????????;3 ???? ??(?????????????? (>Ii I,li lf(li . BT!ntt

C(E«T(tE3h > fI(i!i(р;I i It!i>l! Гора 14 И ООр;) ("("i

BX0 l, уз,(» fi(i!i",Iit )Ot:;3(>И;! !El>IXOLEII>IX IIMII>,,!Ь сов I I, is 1>.х(,.! Its!I f <>ВО(с> рс гистр > деIIIH(1>рации 2, i,,(! EI(ll «11 рным !)лО (ом э.!ем< H Г(l И ) 3 lsl>l х(. l Ь()ч i(>ОГО со«ДИИ(il с Входс)м сбро«;I 1< I чпк;» мс р;3 гири тора 14, В(!хО(hnfrifi«(ппс и с вхо..сол", формирОВ;««. !н (>;(>(1(0!>(х .t tlt3 !ьсов f;). Устрои«(ьч> cnfí,",IHI(. .IE)tt!i <пабжено фиксðOM

II(1)ВО(О .31! (I(llин 6 м ) .Il>I HII (ексорОм колон фазоВОго (. (!3(!(,s 1, рс г!3«тром а.ц)с(и 18, уммат(>!i(. M 1<1, !«мул(,г 1!! Ic ê«ором 2)(). IIO чи— .,у при< t (i!K)! р(I и«г,»,ми кодов <()азО(30! < с Д (3 И Г;S t 11 !i,(< > < 1 Лl) .3 )K K It :sI « H h 0да 22, при «ш i .(I « IHHKB flnмсра Г>s

РИСТОРНО!О,!(>С ((:.> 3 3;31<„S!t СО«,С!3(! ii С В )0ДОМ фИК« а I Ор(! . !<. is! >I О,>н;1 i(HÈH 1<) It

f i <. (Н ы м и I I t E s I h ) s. i I, I C) л l х . I ) Т i I s I. I (K «О р ((2 (1 H лt X ., t,(3п<(< к«Ора фd.s) и>! О с ltsiil <1 1(. i!it(j)!>1) (aIIH0il ls,fÅ ВХОЛII .i!П<>(; > «<ЦЛИ!П НЫ « tstlX(> 1;IM!l р(Ги<"!;)<)!s КО;(ОВ sf(ts 30во! О (,1 .>и(:.1 2 (, !

)ХО(1!)! КО (ОРЬ!Х ll f)(. 1(1;> 3П)>ЧЕIII>l;I.li, II! > (>.Л (<)чс 110! и I!> !Никл кодОВ фа оногo с ätstfãst, fsi sХО,), фИКСатОРа НУ I(I!010 ЗНВЧЕНИЯ СОЕДИНЕН с входом блокировки мультиплексора кодов

$d:s0Bo«0 сдвига, с входом записи регистра адреса 18, входом разрешения записи оперативного запоминающего блока 8 и входом переноса сумматора !9, вход сложения которого соединен с Выходом мультиплексоpd кодов фазового сдвига 17, а вход — — с адре«ной шинОЙ оперативного запоминающе.<. блока 8 и с входной шиной регисгра адреса 18, выход Оперативного запоминан>!цего блока 8 соединен с информаци< иным входом !Icмультиплексора 20 и выхо.чов которого !Го чпс.(у тиристорных преобразователей соединены соответственно с

15 Входами узлов формирования выходных им. пу11)«ОВ 11, а Вход каждоГо узла QopfВО(0 < двига 22, выходы которых <>Отнетств«HHO по)(ь«>к)пены к управляюI!IIt i1 Входал< реги«! ров кодов фазового

«,>Ви; и — 21.

У«! ройство раб«ает следующим образом.

Напряжения фаз «. и Iloчаются на входны(фильтры (,1 и>, а затем на нуль-орI ан(! 2 1 2.ш, фик«ирук>щие положительными Мпульсами 11<1 (??,)hx ?????????????? ???????????? ????????. ??:?? ?????????? ???????? ???????????????????? ?? ??????????(>T(t Esу к)IL(и фа is(>. ETи им ll ул ьсы НОстvпают

В <>1!р«,<«ленной НО«лс.(Онат. ILHo(ти на инфо(:1;1>сио!(Ные Вх< li)l л<У I.THII.!«КСОРа 3, à HB

-0 упр;>)«3.tslK>ill! «< () Вхо (ч нс>«тупает «ны

С Чс ч (:3(>. 3 Н()M(Ei;l ф:«Ы !) КОД, ()С><)СП(iHIs,3 1< ) s! I,lt li I!0,th)t К) I! ill!C >, l HOI (> Нз и нформаl l (i i >! i 111 ; В Х О, () )13 ((i ((В ) 1 Х О Ч Л< )< Л ЬТ и I I Ë (К . л>р s,, h ж,ч, щ(м i мультивибратof у 4 <.

В f)()il«II< Nt За.f(«1 ..»+. KIS т 3. И %I II>!ЛЬ«(Bt>IXO!td

i+,<> ill() I О лl >(. I h н,>И s f ), ГОр <1 - 1 пс р(. Е. 1ЮЧ ИТ ЧР !

)< з Вр(мя tg !«ч(3к 6, ll f)H этом л<ульгпп. I "к. Ор 8 llc. рек Iln÷èòñя на ожидание имl: 3«Ч i.! Si <"0 «. lC., tS K>III()! 0 !10 !!ОрЯДКу НЛ, l I>-Op(ап,>, il!i .ц г«10 llf)(>ll! «с !Н>вторяется.

4с>

I,!Ким образом, на Однол; из BxoiloB элсмен(;1 ИЛИ 5 фс)рмируетс>! с>дноканальная

ll0c. le,10(<а 1(. . 1ьносч 1 «Hiixрони >ирующих импулы ОВ. Импульс с Выхода первого нуль0()I;slt;s 2 задержи!>а(т«я сдвиговым регист45 ()OM 7 па олин такт и нос гупает ttd Второй

Вхоч )«!«м< >гга ИЛИ i, >!ри этом на его выходе

В О,!Ноканальной по(л«довательности им((уль< OB первый из группы является сдвоеннеобходиM() в ла

<н!рсделения, к какой из фаз принадлежит

50 ка к «>iH импулы.

Р()бочии цикл ус(ройства cîñòîèò из п+1

Г;>кгпв !енераторз (актовых импульсов 9, Опр< делHþùèx со«(ояни«выхода счетчика !

f0!st«f)d THpHcT0j)II0t 0 пр«образоватсля 10, з,(ес ь и -- число управляемых тиристоров преобразователей. 1(ðè нулевом состоянии фПК(Пру«МЫй фПК«<1 ГорОМ НУЛЕВОГО ЗНИЧЕНИя

I6 оп(ратипный заli<)минdþùèé блок 8 вклю (а(1СЯ В Р«жИМ 3НПН«И И ОДНОВРс МЕННО блокировкой мультиплексора 17 по входу ( устанавливается нулевое состояние шины В сумматора 19, в результате чего код с выхода регистра адреса 18 увеличивается на 1, поскольку на вход переноса Р сумматора

19 поступает положительный импульс. В этом же также в случае появления на информационном входе D оперативного запоминающего блока 8 сигнала синхронизации он будет записан в виде «1» в ячейку с адресом А (фиг. 2а), в противном случае в нее записывается О. По окончании нулевого такта в регистре адреса 18 спадом сигнала нулевого состояния фиксируется новое значение базового адреса (фиг. 2a).

В течение следуюших тактов коды фазового сдвига у правляюших импульсов соответствующих тири< торных преобразователей поочередно подключаются через мультиплексор 17 к шине В сумматора 19, при этом на выходе сумматора формируется адрес ячейки, из которой считывается информация

А« = (А,— T.) mod 2, (1) где T — код фазового сдвига (задержки); — разрядность ОЗБ и сумматора;

К вЂ” номер обслуживаемого в данном такте тиристорного преобразователя (К =- 1, 2,...n).

Выходной сигнал переноса сумматора игнорируется, т.е. операция сложения выполняется по mort 2 (поскольку выходная ши/ на мультиплексора 17 содержит инверсньп сигналы, фактически выполняется операция вычитания кода фазового сдвига из кода базовог.) адреса).

Таким образом, в течение следук)гцих тактов цикла оперативный запоминающий бл<)к

8 переключается в режим считывания, ri на шину В сумматора 19 поочередно поступают инвертированные коды фазового сдвига, а на его выходе формируется относительный адрес А.. Базовый адрес, перемешаясь в поле ячеек ОЗБ 8. производи г активизацию одной из них в моменз прихода задерживаемого имп,льса, а считачная информация из нее будет через то время, на которое импульс в данном канале задерживается (фиг. 2а).

Импульсы с выхода оперативногс) запоминанццего блока 8 поступаю- на информационный вход демультиплексора 20, соответствующий номеру канала, определя) мого в данном такте, поскольку на адресный вход демультиплексора подается тот же код, что и на адресный вход мультип»etre<>pa 17.

Во избежание нарушения работы устройства ввиду конечного числа ячеек оперативного запоминающего блока 8 необходимо выбрать соответствующую разрядность счетчика 10 и ОЗБ 8 таким образом, чтобы обновление информации в данной ячейке могло произойти только после считывания предыдушей информации, т.е. чтобы выполнялось условие

2 m a x(T -). (2) В этом случае ситуация, возникшая в резул ьтате суммирования по модулю 2 (т.е. без переноса из старшего разряда сумматора), не приведет к сбою, поскольку ячейка с базовым адресом Ав вновь опрашивается через заданное время, так как после ячейки 2 --1 выбирается ячейка 0 (фиг. 2б).

Разрядность ОЗБ 8 и сумматора 19 зависит от длительности фазового сдвига т, точности его установки ео и определяется соотношением

l = ent (log — -) + l.

15

Частота генератора тактовых импульсов определяется из условия

f= â€”вЂ”

eo (4) 20 где ъ = log)rn

Соответственно разрядность счетчика 10 — I+ v.

Поступление нового задерживаемого импульса до считывания предыдушего оче25 видно не нарушает работы устройства, поскольку он просто записывается в соотвстствуюшую ячейку и будет считан с такой же задержкой, как и предыду ий.

Установка счетчика 14 осуществляется по дачей на его вход сброса потенциала в момент прихода сдвоенного импульса, которым зашифрован управляющий импульс тиристора в первой фазе преобразователя.

Каждый прпходягций на вход счетчика

1з импульс задерживается на такт сдвигов,))м регистром дешифрации 12 и поступает

) а вход элемента И 13ь поэзому по приходу

r,д военного импульса на выходе элемента

И 13i формируется положительный потенциал, подаваемый на вход сброса счетчиг a 14ь осушествляя таким образом дешиф40

После сдвоения имульсов, формируемых на выходе счетчика 14, в формирователе ! )i они подаются на управляющие вход) I первого тиристорного преобразователя.

Блок задержки записи кода фазового

45 сдвига 22i, на вход которого также подаются импульсы управления с соответствующего выхода демультиплексора 20, формирует импульс, инициирующий запись в eоответствующий регистр 21, задержанный на интервал времени, который определяется ди50 намикой работы тиристорных преобразователей. Это позволяет избежать повторное считывание информации в том случае, сс in на входе регистра 21) код фазового сдвига увеличивается сразу после появления управляюшего импульса, что может привести к неправильному распределению управляк)щих импульсов по каналам.

В следук)щих тактах цикла аналогичная последовательность операций повторяет1381668

Формула азобретения еняа& ение яенещення авдее афеса

Z -l

Фи 2

Б 111111! 111 Заказ Мо7, 55 Тираж 665 11 о д и е ное

11роиаводетвенно-ноаиграфичееное предприятие, г. Ужгород, së. 1! роектная, 4 ся по отношеник> к импульсам управления остальных тиристорных преобразователей.

Таким образом, применение в данном устройстве по сравнению с известными новых элементов, а именно фиксатора нулевого значения, регистров кодов фазового сдвига

21 21„, мультиплексора кодов фазового сдвига 17, регистра базового адреса 18, сумматора 19 и блоков задержки записи кода фазового сдвига 22 - 22„, позволяет повысить надежность работы цифрового устройства в динамических режимах, когда фазовая задержка импульсов значительно изменяется н течение одного периода частоты сети.

Цифровое устройство для управления ведомым сетью преобразователем, содержащее по числу фаз питающей сети фильтры, входы которых предназначены для подключения к фазам сетевого напряжения, выходы пофазпо подключены к входам нульорганов, выходами подключенных к информационным входам мультиплексора, к выхо ду которого подкл научены ждущий мультивибратор и первый вход элемента ИЛИ, выход ждущего мультивибратора подключен к входу счетчика номера фазы преобразователя, выход которого подключен к адресной шине мультиплексора, сдвиговый регистр шифрации, нход которого подключен к выходу нуль-о1п ана первой фазы, выход — к ВТо рому входу элемента ИЛИ, выход которого подключен к информационному входу г перативного запоминающего блока, генера1.р тактовых импульсон, выход которого подключен к входу выборки оперативного запоминающего блока и к входу счетчика номера тиристорного преобразователя по числу THpHcToptthtx преобразователей, узлы формирования выходных импульсов, каждый из которых содержит сднигоный регистр дешифрации, э..емент И, счетчик номера тиристора и формирователь сдвоенных импульсов, вход

40 сдвигового регистра дешифрации объединен с вторым входом элемента И и счетным входом счетчика номера тиристора и образует вход узла формирования выходных импульсов, выход сдвигового регистра дешиф рации соединен с первым входом элемента И, выход которого соединен с входом сброса счетчика номера тиристора, выход которого соединен с входом формирователя сдвоенных импульсов, отличающееся тем, что, с целью улучшения надежности работы, оно снабжено фиксатором нулевого значения, мультиплексором кодов фазового сдвига, регистром адреса, сумматором, демультиплексором, по числу тиристорных преобразователей регистрами кодов фазового сдвига и блоками задержки записи кода, причем выход счетчика номера тиристорного преобразователя соединен с входом фиксатора нулевого значения и адресными шинами демультиплексора и мультиплексора фазо ного сдвига, информационные входы которого соединены с выходами регистров кодов фазового сдвига, входы которых предназначены для подключения к источнику кодов фазового сдвига, выход фиксатора первого значения соединен с входом блокировки мультиплексора кодов фазового сдвига, с входом записи регистра адреса, с входом разрешения записи оперативного запоминак1щего блока и с входом переноса сумматора,. вход сложения которого соединен с выходом мультиплексора кодов фазового сдвига, а выход с адресной шиной оперативного запоминающего блока и с входной шиной регистра адреса, выход оперативного запоминающего блока соединен с информационным входом демультиплексора, п выходов которого по числу тиристорных преобразователей соединены соответственно с входами узлов формирования входных импульсов, а вход каждого узла формирования выходных импульсов объединен с входом соответствующего блока задержки записи кода фазового сдвига, выходы которых соответственно подключены к управляющим входам регистров кодов фазового сдвига.