Двухтактный усилитель мощности

Иллюстрации

Показать всеРеферат

Изобретение относится к электронной технике и обеспечивает повышение нагрузочной способности.У-ль содержит входные транзисторы (Т) 1 и 2, выходные Т 3 и 4, управляемые г-ры 5 и 6 тока, управляющие Т 7 и 8. Вновь введены дополнительные Т 9 и 10, г-ры 11 и 12 стабильного тока. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСГ1УБ ЛИК

„„SU„„1 81

А1 (5В 4 Н 03 F 3/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

И

13 .

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) .4008687/24-09 (22) 14.01.86 (46) 15.03.88. Вюл. 11» 1О .(71) Пензенский филиал Всесоюзного научно-исследовательского технологического института приборостроения (72) Л.В.Каменев, В.Ф.Рыжов, А.А.Чумаков и С.В.Яварев (53) 621.375.026(088.8) (56) Авторское свидетельство СССР

М 1224966, кл. Н 03 F 3/26, 1985. (54) ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ (57) Изобретение относится к электронной технике и обеспечивает повышение нагрузочной способности.У-ль содержит входные транзисторы (Т)

1 и 2, выходные Т 3 и 4, управляемые г-ры 5 и 6 тока, управляющие

Т 7 и 8. Вновь введены дополнительные Т 9 и 10, г-ры 11 и 12 стабильного тока. 1 ил.! 381685

Изобретение относится к электронной технике « может использоваться в электроизмерительной и звуковоспроизводящей аппаратуре, в частности, в качестве выходных каскадов интегральных операционных усилителей.

Цель изобретения — повышение нагрузочной способности.

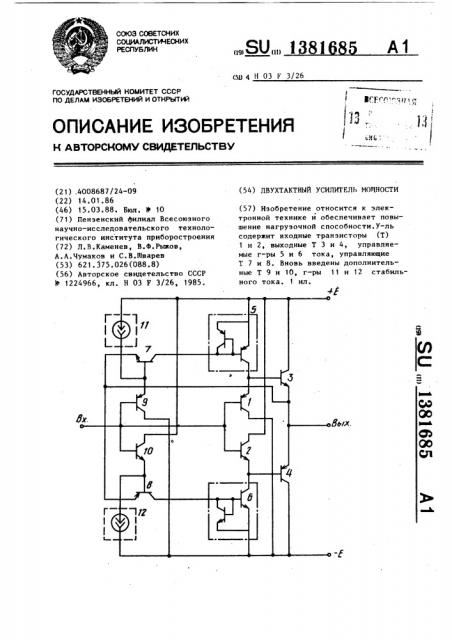

На чертеже представлена пр««пипи- 10 альная электрическая схема двухтактного усилителя мощности.

Двухтактны« усилитель мощности содержит входные транзисторы 1, 2, выходные транзисторы 3,4, управляе- 15 мые генераторы тока 5, 6, управляющие трапа«сторы 7,8, дополнительные транзисторы 9,10, .генераторы стабильного тока (ГСТ) 11, 12.

Двухтакт«ый усилитель мощности 20 работает следующим образом.

При отсутстн«« сопрот«влсн«я Р„ нагрузки коллекторные токи входного, выходного, управляющего, дололн«тельного тра«э«сторов 1(2), 3(4), 7(8), 9(10) обоих плеч попарно равны и практически не зависят от значения входного «апряже««я Пц„, поэтому падения на«ряжения Цбэ1 у ЦБэ2

БЭЗ БЭ4 БЭЭ ЬЭВ к БЭ9 ЬЭ10

30 на их эмиттерных переходах также попарно равны « не зависят от значения входного напряжения Uä„ . Разность

h,о между выходным и входным напряжениями U, „ и U

25

) U69 3 )

- Lv„,l—

О.

При полож«тельной (отрицательной) 40 полярности входного напряжения подключение сопротивления P„ нагрузки вызывает увеличение коллекторного тока выходного транзистора

3(4). При этом возникает разность 45

hU. Согласно уравнению Эберса-Молла (LP 1n ), кз 1к4 (, 1п

6 U69ç

В случае равенства площадей эмиттевных переходов S, и S (S и S ), Ян и Sr (S12 и SБ) вхОднОГО и выходного, дополнительного и управлякт/q

К

16UI ) Ueb

I v„,I = I v„,) — ) v„,)

БЭ9 t l БЭБ) ) БЭ<О (! ((Бэ4) Цт 1п о )1 (1 ЦБЭ 4 ) — приращение падения напряжения;

25,3 мВ (при

20 С); заряд электрона; постоянная Больцмана;

Т вЂ” абсолютная температура в Кельвинах; ъ(1 <4) кОллектОрныи тОк ВыхОднО ного транзистора 3(4);

Т„ (1 „4 ) — коллекторный ток выходного транзистора 3(4) при отсутствии входного напряжения.

Приложенная к эмиттерному переходу управляющего транзистора 7(8) разность вЦ вызывает увеличение его коллекторного тока Т „ (y « )

4 1/ в е раэ. Изменением падения напряжения на эмиттерных переходах дополнительных транзисторов 9,10 можно пренебречь ввиду относительной стабильности их коллекторных токов, обусловленной малостью базовых токов управляющих транзисторов 7,8.Увеличение коллекторного тока 1 „ (1„Б) вызывает прямо пропорциональное увеличение тока управляемого источника тока 5(6) и коллекторного тока входного транзистора 1(2), при этом падение напряжения ЦБэ (ЦБЭ2 эмиттерном переходе входного транзистора 1(2) получает приращение

ЬЦБэ, (6ЦБэ2). Пренебрегая базовым током выходного транзистора 3(4)

)дП„,) = )ri V», g, () ОЦ„,) = о ° къ

Увеличение коллектор«ого тока выход«ого транзистора 3(4) в — — (. ) раз вызывает уменьшение

1кэ 1k4

1k3 к4 коллекторных токов входного, выходного, управляющего транзисторов 2(1), 4(3), 8(7) и тока управляемого источника тока 6(5) во столько же раз, при этом падения напряжения на эмиттерных переходах входного, выходногои управляющего транзисторов 2(1), 4(3) и 8(7) умейьшается на (1 (! Бэ4 ) ) 692 ) 1п о к4

1381685

ГИ о еьи, = 1 1 з Ткв

TlI вых о

1 8 I

m м

ВЫХ I ВЫХ м вых ° где („, (4 и коэффициенты передачи тока выходных

15 и управляющих транзисторов

3,4, и 7,8 соответст20

Формула изобретения

Составитель И.Водяхина

Редактор О.Спесивых Техред, .М.Ходанич

Корректор В.Бутяга

Заказ 1193/54 Тираж 928

ВНИИПИ Государственного „комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ющего транзисторов 1 и 3 (2 и 4), 9 и 7 (10 и 8) первого (второго) плеча максимальный выходной ток Is„, lll вы> (I »»»Ä, )

5 венно.

При работе двухтактного усилителя мощности на емкостную нагрузку при значительном отставании U „от 11

25 емкость нагрузки будет заряжаться

m токОм I в„х .

Двухтактный усилитель мощности, 30 содержащий в каждом плече последовательно соединенные входной и выходной транзисторы, включенные по схеме с общим коллектором, управляемый генератор тока, включенный между шиной источника питания и эмиттером входного транзистора, управляющий транзистор, коллектор которого соединен с управляющим входом управляемого генератора тока, а эмиттер— с эмиттером одноименного транзистора другого плеча, при этом структура управляющего н выходного транзисторов одного плеча соответствует структуре входного транзистора другого плеча, отличающийся тем, что, с целью повышения нагрузочной способности,в каждое плечо введены генератор стабильного тока и дополнительный транзистор, включенный по схеме с общим коллектором и структура которого соответствует структуре входного транзистора, база дополнительного транзистора соединена с базой входного транзистора, эмиттер— с базой управляющего транзистора и через генератор стабильного тока ". с шиной источника питания, при этом обьеднненные эмиттеры управляющих транзисторов подключены к эмиттерам выходных транзисторов.