Устройство для цифро-частотного умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике , измерительной и вычислительной технике и может быть использовано для умножения частоты импульсов на код в устройствах преобразования информации, в частности в цифровых функциональных преобразователях одной или нескольких переменных. Цель изобретения - повыше1ше точности умножения частоты. Устройство содержит умножитель 2 частоты на код /УЧ/, узел 4 вычитания импульсных последовательностей /УВ/, коммутатор 8, делитель 13 частоты на два, ключ 16,узел 19 суммирования импульсных последовательностей /УС/, первый вход которого подключен к выходу ключа 16, информационный вход которого подключен к выходу УЧ 2, первому информационному входу коммутатора 8 и первому входу УВ 4, второй вход которого подключен к входу устройства, выход УВ 4 - к второму информационному входу коммутатора 8, управляющий вход которого подключен к второму входу ключа 16 и п-му разрядному входу 3 и усгановки коэффициента умножения, выход коммутатора 8 подключен к входу делителя 13 частоты на два, выход которого подключен к второму входу УС 19, выход которого является выходом устройства, управляюс1ие входы УЧ 2 подключены к соответствующим с первого по (п-1)-й разрядным входом 3. 4 ил. (Л О5 00 со со СХ)

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5D 4 G 06 F 7/68

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2!) 4134895/24-24 (22) 11 ° 10.86 (46) 23.03.88. Бюл. 9 11 (71) Львовский политехнический институт им. Ленинского комсомола (72) В.Б.Будыкевич, Ю.В.Опотяк, В.И.Отенко, Л.Т.Пархуць (SV) и Олива

Вильяр Пастор (CV) (53) 621.3 (088.8) (56) Патент США И 2910237, кл. 235-.

150.3, опублик. 1959.

Гутников В.С. Интегральная электроника в измерительных устройствах.

Л.: Энергия, 1980, с. 238-240. (54) УСТРОЙСТВО ДЛЯ ЦИФРОЧАСТОТНОГО

УМНОЖЕНИЯ (57) Изобретение относится к автоматике, измерительной и вычислительной технике и может быть использовано для умножения частоты импульсов на код в устройствах преобразования информа- ции, в частности в цифровых функциональных преобразователях одной или нескольких переменных. Цель изобретения - повышение точности умножения

Зд Зуу 1 Eg Яр

„„Я0„„1383348 A 1 частоты. Устройство содержит умножитель 2 частоты на код /УЧ/, узел 4 вычитания импульсных последовательностей /УВ/, коммутатор 8, делитель 13 частоты на два, ключ 16,узел

19 суммирования импульсных последовательностей /УС/, первый вход которого подключен к выходу ключа 16, информационный вход которого подключен к выходу УЧ 2, первому информационному входу коммутатора 8 и первому входу УВ 4, второй вход которого подключен к входу устройства, выход

УВ 4 — к второму информационному входу коммутатора 8, управляющий вход которого подключен к второму входу кгпсча 16 и и-му разрядному входу 3 и установки коэффициента умножения, выход коммутатора 8 подключен к входу делителя 13 частоты на два, выход которого подключен к второму входу УС

19, выход которого является выходом устройства, управляющие входы УЧ 2 подключены к соответствующим с первого по (и-1)-й разрядным входом 3 .

4 ил.

1383348

Изобретение относится к автоматике„ измерительной и вычислительной технике и может быть использовано для умножения частоты импульсов на код в устройствах преобразования информации, в частности в цифровых функциональных преобразователях одной или нескольких переменных.

Целью изобретения является повы шение точности умножения частоты.

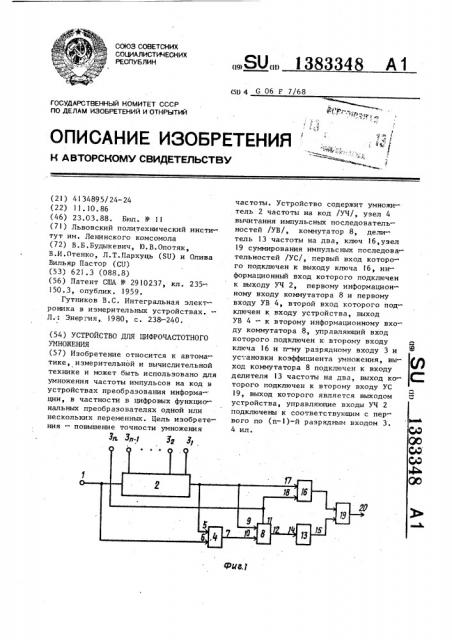

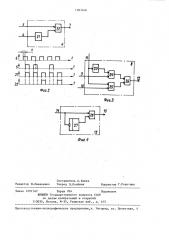

На фиг.1 представлена структурная схема устройства для цифрочастотного умножения; на фиг.2 — узел вычитания импульсных последовательностей 15 (вариант выполнения) и временные диаграммы, поясняющие его работу; на фиг.3 и 4 — коммутатор и делитель частоты на два соответственно, ва,рианты выполнения. 20

Устройство содержит частотный вход 1, умножитель 2 частоты на код, разрядные входы 3,,..., 3„ установки коэффициента умножения, узел 4 вычитания импульсных последовательностей с входами 5 и 6 и выходом 7,коммутатор 8 с информационными 9 и 10 и управляющими 11 входами и выходом

l2, делитель 13 частоты на два с входом 14 и .выходом 15, ключ 16 с инфор- 30 мационным 17 и управляющим 18 входами, узел 19 суммирования импульсных последовательностей, выход 20.

Узел 4 вычитания импульсных последовательностей (фиг.2) содержит элемент 21 задержки, элемент И 22.

Коммутатор 8 (фиг.3) содержит элемент НЕ 23, элементы И 24 и 25, эле-мент ИЛИ 26.

Делитель 13 частоты на два (фиг.4) 40 содержит счетный триггер 27, элемент И 28.

В устройстве (фиг.1) управляющие входы умнох<ителя 2 частоты на код подключены к разрядным входам 3, 45

3,...., 3 „, установки коэффициента умножения, частотный вход умножителя 2 частоты на код подключен к входу 1, первый вход узла 19 суммирова.ния импульсных последовательностей подключен к выходу ключа 16, информа. ционный вход 17 которого подключен.к выходу умножителя 2 частоты на код, инфсрмационному входу 9 коммутатора

8 и входу 5 узла 4 вычитания импульс-5 ных последовательностей, вход 6 которого подключен к входу 1, выход 7 узла 4 вычитания иипусльных последовательностей подключен к информационному входу 10 коммутатора 8, управляющий вход 11 которого подключен к входу 18 ключа 16 и разрядному входу 3 установки коэффициента умножения,вы ход 12 коммутатора 8 подключен к.входу 14 делителя 13 частоты на два, выход 15 которого подключен к второму входу узла 19 суммирования импульсных последовательностей, выход которого является выходом 20 цифрочастотного умножителя.

В узле 4 .вычитания импульсных последовательностей (фиг.2) инверсный вход элемента И 22 и вход элемента 21 задержки являются соответственно входами 5 и 6, выход элемента И 22 является выходом 7, прямой вход элемента И 22 подключен к выходу элемента

21 задержки.

В коммутаторе 8 (фиг.2) информамационный вход 9 подключен к первому входу элемента И 24, второй вход которого подключен к выходу элемента

НЕ 23, вход которого подключен к управляющему входу 11 и первому входу элемента И 25, вход которого подключен к информационному входу 10, выход элемента И 25 подключен к первому входу элемента ИЛИ 26, второй вход которого подключен к выходу элемента И 24, выход элемента ИЛИ 26 является выходом 12.

В делителе 13 частоты на два (фиг.4) тактовый вход счетного триггера 27 подключен к входу 14 и-первому входу элемента И 28, второй вход которого подключен к выходу счетного триггера 27, выход элемента И 28 является выходом 15.

Устройство работает следующим образом.

Пусть на входы 3,,..., 3„ подан и-разрядный двоичный код коэффициента умножения К

tl

К= а; 2, (1) e$ где а; - значащая цифра i-го разряда двоичного кода коэффициента умножения К, (а; = 0; 1),а в качестве умножителя 2 частоты на код использован двоичный умножитель частоты К 155 ИЕ8 в виде интегральной микросхемы.

Тогда количество N ö„ импульсов на его выходе определяется выражением и

"sx а; 2 (2) вич

1383348 где N » — количество импульсов, подаваемых на вход 1 цифрочастотного умножителя 2.

Работа узла 4 вычитания импульс5 ных последовательностей поясняется диаграммами на фиг.2, где обозначены номерами выводы, на которых они сняты; в — временная задержка импульсов элементом 21 задержки, равная времен- ip ной задержке импульсов, вызываемой умножителем 2 частоты на код.

На выходе узла 4 N, количество импульсов равно (3) i5 св . Вх эуЧ х причем импульсы на выходе узла 4 вычитания импульсных последовательностей и на выходе умножителя 2 частоты на код не совпадают во времени. 20

Количество импульсов 1!1! на выходе ключа 16 равно. (4) а в 1!1вуч х где а „ -. значение и-го разряда двоич- 25 ного кода коэффициента умножения К.

Количество М„.импульсов на выходе коммутатора 8, работа которого ясна на фиг.3 (при подаче на управляющий 30 вход 11 потенциала логического нуля или единицы коммутатор 8.пропускает на выход 12 импульсы с информационного входа 9 или с информационного входа 1О соответственно), определяется выражением

Я = а„Нс + а„1!1 ..., (5) где а„ - инверсное значение а„,.(а„

a„) ° 40

11 вв!х N Né

В этом случае количество N импульсов на выходе делителя 13 частоты на два, представляющего собой делитель частоты на два со стробированием выходных импульсов входными (фиг,.4), равно

a,Nce + (1 — а!!)Нрм

N (6)

1 2

Так как не совпадают во времени 50 импульсы на выходах умножителя 2 частоты на код и узла 4 вычитания импульсных последовательностей, то не совпадают во времени и .импульсы на выходах ключа 16 и делителя 13 часто- 55 ты на два. Поэтому количество Нв„, импульсов на выходе 20 равно или а 11 + св (ал) ВРУ! а N +(1ВЫх в ыУЧ а в качестве узла 19 может быть применен элемент ИЛИ.

Проведя в (8) упрощения с учетом (3), получаем а„1!1вх + И ух

З» (9) вых 2 или с учетом (2) а!! 1 1вх +

2л (10)

Ьых

Окончательна!! !M а; 2

° f

N вых 2 !! или

N!!x K 1 вв!х ° (12)

Формула изобретения

Устройство для цифрочастотного умножения, содержащее умножитель частоты на код, управляющие входы которого подключены к соответствующим с первого по (n-1)-й разрядным входам установки коэффициента умножения устройства, частотный вход умножителя частоты на код является частотным входом устройства. о т л и ч а ю— щ е е с я тем, что, с целью повышения точности умножения частоты, оно дог!олнительно содержит узел вычитания импульсных последовательностей, коммутатор, делитель частоты на два, ключ, узел суммирования импульсных последовательностей, первый вход которого подключен к выходу ключа, информационный вход которого подключен к выходу-умножителя частоты на код, первому информационному входу коммутатора и первому входу узла вычитания импульсных последовательностей, второй вход которого подключен к частотному входу устройства, выход узла вычитания импульсных последовательностей подключен к второму информационному входу коммутатора, управляющий вход которого подключен к управляющему входу ключа и и-му разрядному входу установки коэффициента умножения устройства, выход коммутатора подключен к входу делителя частоты на два, выход которого подключен к второму входу узла суммирования импульсных последовательностей, выход которого является выходом устройства.

13ВЗЗ4Я

Составитель A.Êëâåâ

Редактор Н.Лазаренко Техред Л.Олийнык

Корректор Г.Решетник

Заказ 1297/47 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,г. Ужгород, ул. Проектная, 4