Устройство для контроля микропроцессорных цифровых блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике, может использоваться для автоматизированного контроля блоков ЦВМ и позволяет повысить достоверность контроля цифровых блоков, содержащих микропроцессоры и микропроцессорные БИС. Устройство содержит блок 1 управления , 2 формирователей 2 остатка (где t - разрядности двунаправленной шины данных контролируемого цифрового блока), сумма

СО|ОЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (58 4 G 06 F 11 08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

4 .г .

Адрес иольцеоеого сддогор

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4033206/24-24 (22) 06.03.86 (46) 23.03.88. Бюл. № 11 (71) Кишиневский политехнический институт им. С. Лазо (72) В. И. Борщевич, В. Д. Жданов, Е. В. Морщинин, И. А. Мардаре, В. Ф. Гушан и В. В. Сидоренко (53) 681.3(088.8) (56) Авторское свидетельство СССР № 1078430, кл. G 06 F 11/08.

Авторское свидетельство СССР № 1037257, кл. G 06 F 11/08, 1982.

„„SU„„1383364 А 1 (54) УСТРО|"|СТВО ДЛЯ КОНТРОЛЯ МИКРОПРОЦЕССОРН ЦИФРОВЫХ БЛОКОВ (57) Изобретение относится к цифровой вычислительной технике, может использоваться для автоматизированного контроля блоков ЦВМ и позволяет повысить достоверность контроля цифровых блоков, содержащих микропроцессоры и микропроцессорные

ЪИС. Устройство содержит блок 1 управления, 2Е формирователей 2 остатка (где f.— разрядности двунаправленной шины данных контролируемого цифрового блока), f,ñóììà1383364 торов 3 по модулю два, К кольцевых сдвиговых регистра 4 (где К вЂ” разрядности командной шины контролируемого цифрового блока), дешифратор 5, регистр 6, элемент 7 задержки, (повторителей 8 с тремя состояниями, блок 9 индикации и подключено к контролируемому цифровому блоку 10.

Формирователи 2 остатка группы 1 предназначены для генерации m-последовательИзобретение относится к цифровой вычислительной технике и может использоваться для автоматизированного контроля блоков ЦВМ, содержащих микропроцессорные БИС.

Цель изобретения — повышение достоверности контроля.

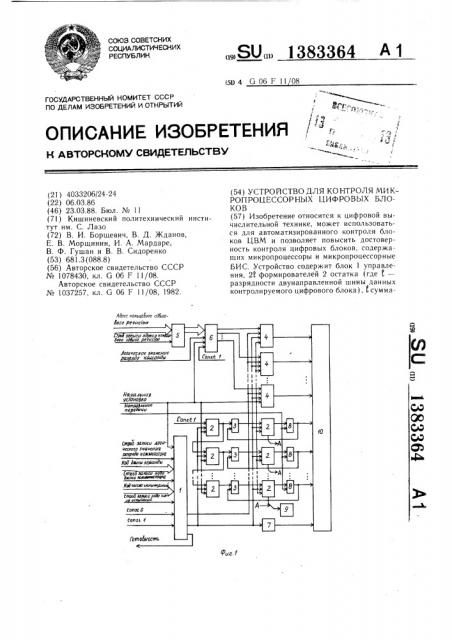

На фиг. 1 представлена структурная схема устройства; на фиг. 2 — схема блока управления; на фиг. 3 — схема формирователя остатка; на фиг. 4 — схема кольцевого сдвигового регистра; на фиг. 5 — схема входного регистра; на фиг. 6 и 7 — временные диаграммы работы блока управления; на фиг. 8— временная диаграмма поступления входных сигналов.

Устройство (фиг. 1) содержит блок 1 упавления, 2(формирователей 2 остатка, сумматоров 3 по модулю два, К кольцевых сдвиговых регистров 4, дешифратор 5, регистр 6, элемент 7 задержки, (повторителей 8 с тремя состояниями, блок 9 индикации и подключено к контролируемому цифровому блоку 10.

Блок 1 управления (фиг. 2) содержит первый буферный регистр 11, элемент 12 задержки, первый элемент HE 13, второй буферный регистр 14, первый элемент И 15, первый 16 и второй 17 счетчики, первый 18 и второй 19 дешифраторы, второй 20 и третий 21 элементы НЕ, элемент ИЛИ вЂ” HE 22, первый 23 и второй 24 триггеры, генератор 25 тактов, второй элемент И 26, первый формирователь 27 импульсов, третий триггер 28, второй формирователь 29 импульсов, третий элемент И 30, элемент ИЛИ 3!.

Формирователь 2 остатка (фиг. 3) содержит первый сумматор 32 по модулю два, регистр 33 сдвига, второй сумматор 34 по модулю два.

Кольцевой сдвиговый регистр 4 (фиг. 4) содержит элемент 2И вЂ” ИЛИ 35, регистр 36 сдвига. Регистр 6 (фиг. 5) содержит К триггеров 37. В качестве формирователя 2 остатка первой и второй групп (где первая (1) группа состоит с первого по (-й формировате5

40 ности 1 формирователей 2 остатка группы 2 предназначены для генерации m-последовательности и формирования сигнатур. Сформированные сигнатуры индицируются блоком

9 индикации. К кольцевых сдвиговых регистра 4 предназначены для записи, хранения и многократной подачи на командную шину контролируемого цифрового блока 10 тестовых программ. 8 ил. лей 2 остатка, а вторая (2) — с ((+I)-го по 2(-й формирователей остатка) используется устройство на основе генератора m-последовательности, выполняющее деление входной двоичной последовательности на полином вида: g(x)=x"+х +1. Количество разрядов регистра 33 сдвига остатка группы 2 определяет достоверность сигнатурного анализа и при необходимости может быть увеличено с соответствующими изменениями обратной связи для сохранения выполнения условий генерации последовательности максимальной длины.

Формирователи 2 остатка группы 1 функционируют только как генераторы m-последовательности, формирователи 2 остатка группы 2 функционируют как генераторы m-последовательности и как формирователи сигнатур. К К-разрядной командной шине контролируемого цифрового блока 10 подключается

К-разрядных кольцевых сдвиговых регистра, служащих для записи, хранения и многократной подачи (т. е. мультиплицирования)

К-разрядных тестовых команд (такие кольцевые сдвиговые регистры будем называть мультипликаторами), образующих функционально законченную ТП. За один такт работы мультипликаторов ТП будет подаваться на контролируемый цифровой блок 10 и займет в мультипликаторах исходное положение. Число тактов работы мультипликаторов определяет число мультипликаций сформированных ТП. Длина кольцевого сдвигового регистра g, выбирается из следующего соотношения: ! ..„((о..., где L,„= максимальной длине ТП, длине кольцевого сдвигового регистра, определяемой исходя из аппаратных затрат. Под длиной кольцевого сдвигового регистра понимается число его разрядов, а под длиной ТП вЂ” число содержащихся в ней команд.

Регистр 36 сдвига представляет собой восьмиразрядный регистр сдвига, например интегральная микросхема К155ИР13. Причем управляющий вход Vl и вход последо1383364

3 вательного занесения при сдвиге влево

D — соединен с шиной нулевого потенциала, которая представляет собой провод, соединенный с нулевым полюсом источника питания. Управляющий вход V2 соединен с шиной единичного потенциала, которая представляет собой вывод резистора, другой вывод которого соединен с положительным полюсом источника питания. Для увеличения длины кольцевого сдвигового регистра восьмиразрядные регистры сдвига следует соединить последовательно: выход старшего разряда первого регистра сдвига следует соединить с входом последовательного занесения при сдвиге вправо D+ второго регистра сдвига, входы Vl, V2, С и D- второго регистра сдвига следует соединить с аналогичными входами первого регистра сдвига.

Триггеры 37 представляют собой D-триггеры, например интегральная микросхема

К155ТМ2.

Триггеры 23, 24 и 28 представляют собой 1-К-триггеры, например интегральная . микросхема К155ТВ1. Входы 1 каждого из триггеров 23, 24 и 28 должны быть объединены. Входы К также должны быть объединены. Входы установок в «О» триггеров 23, 24 и 28 должны быть соединены с шиной единичного потенциала.

В качестве сумматороа 3, 32 и 34 по модулю два могут быть использованы двухвходовые элементы ИСКЛЮЧАЮШЕЕ ИЛИ например интегральная микросхема

К155Л П5.

В качестве буферных регистров 11 и 14 может быть использован, например, четырехразрядный регистр, выполненный на базе четырех D-триггеров, входящих в интегральную микросхему К155ТМ8. Для увеличения числа испытаний необходимо использовать несколько буферных регистров 14. В этом случае входы синхронизации буферных регистров следует объединить, входы установки в «О» также надо объединить. Информационные входы следует поразрядно соединить с дополнительными входами «Код числа испытаний».

В качестве счетчиков 16 и 17 может быть использован, например счетчик двоичный

4-разрядный К155ИЕ7. Входы сложения счет чиков 16 и 17 должны быть соединены с шиной единичного потенциала. Для увеличения числа испытаний может быть использовано несколько счетчиков 17. В этом случае информационные входы параллельной записи должны быть соединены с выходами дополнительных буферных регистров 14, а выход переноса каждого предыдущего счетчика должен быть соединен с входом вычитания последующего счетчика. Причем необходимо будет увеличить и число входов дешифратора 19.

В качестве дешифраторов 18 и 19 могут быть использованы, например, логические

4 элементы ИЛИ вЂ” НЕ, входящие в состав интегральной микросхемы К155ЛЕЗ.

В качестве повторителя 8 с тремя состояниями может быть использован, например, «Повторитель с тремя состояниями», входящий в состав интегральной микросхем ы К155Л П8.

Величина времени задержки элемента 7 задержки синхроимпульсов определяется временем, необходимым на передачу информации с кольцевых сдвиговых регистров 4 и формирователей 2 остатка группы 2 на командную шину и шину данных (через повторители 8 с тремя состояниями) соответственно. Величина времени задержки элемента 12 задержки определяется временем записи информации в буферный регистр 11.

Каждый i-й формирователь 2 остатка группы 2 используется в качестве генератора тестовых воздействий, если i-й вывод контролируемого цифрового блока 10 является входом.

Каждй i-й формирователь 2 остатка группы 2 используется в качестве формирователя сигнатуры, если i-й вывод контролируемого цифрового блока 10 является выходом.

Каждый i-й формирователь 2 остатка группы 2 используется одновременно и как генератор тестовых воздействий, и как формирователь сигнатуры, если i-й вывод контролируемого цифрового блока 10 является одной из линий двунаправленной шины данных. Причем в те такты процесса контроля, когда шина данных включена в режим приема информации, формирователь 2 остатка группы 2 используется в качестве генератора тестовых воздействий, когда же шина данных включена в режим выдачи информации с контролируемого цифрового блока

10, формирователь 2 остатка группы 2 используется как формирователь сигнатуры. (формирователей 2 остатка группы 1 служат для обеспечения работы t,формирователей 2 остатка группы 2 в качестве генераторов m-последовательности.

Регистр 6 служит для записи новой тестовой команды, которая входит в состав ТП.

Устройство работает следующим о6разом.

При включении питания состояние триггеров, счетчиков, регистров сдвига, буферных регистров может быть произвольным.

По сигналу «Начальная установка», который представляет собой импульс с низким активным уровнем и поступает на первый вход блока 1 управления, на первый вход каждого формирователя 2 остатка группы 1 и группы 2, на первый вход каждого кольцевого сдвигового регистра 4 и на первый вход регистра 6, происходит сброс триггеров 37 регистра 6, регистров 33 сдвига формирователей 2 остатка группы 1 и группы 2, регистров 36 сдвига кольцевых сдви1383364 гов регистров 4, буферных регистров 11 и 14 блока 1 управления; кроме этого, происходит сброс счетчиков 16 и 17 импульсом с высоким активным уровнем, проинвертированным элементом НЕ 13 блока 1 управления. На выходах дешифраторов 18 и 19 находятся логические единицы, на выходе элемента НЕ 20 и на выходе элемента НЕ 21 находятся логические нули. На входе синхронизации С, на входе установки в «1», на входах и К триггера 23 находится уровень логического «О», на выходе триггера 23, который является первым выходом блока 1 управления, находится уровень логической «1», который «сообщает» генератору тестовых последовательностей команд о том, что устройство готово принимать логические значения разрядов тестовых команд. На инверсных выходах триггеров 24 и 28 находится уровень логического «0»,чем обеспечивается запрет прохождению импульсов с генератора 25 тактов, через элемент И 30, на вторые входы формирователей 2 остатка группы 1 и группы 2, на четвертые входы кольцевых сдвиговых регистров 4 и на вход элемента 7 задержки синхроимпульсов, Информация с шины «Код длины команды» поступает на вторую группу входов блока 1 управления и по стробирующему сигналу, который поступает с шины «Строб записи кода длины команды» на третий вход блока 1 управления в виде импульса с высоким активным уровнем, записывается в буферный,регистр I I, а затем появляется на информационных входах параллельной записи счетчика 16.

Импульс с третьего входа блока 1 управления через элемент 12 задержки в виде импульса с низким активным уровнем поступает на первый вход элемента И 15. На втором входе элемента И 15 находится уровень логической «1», благодаря чему на выходе этого элемента появляется импульс с низким активным уровнем, который записывает информацию с буферного регистра 11 в счетчик 16.

Информация с шины «Код числа испытаний» поступает на пятую группу входов блока 1 управления и по стробирующему сигналу, который поступает с шины «Строб записи кода числа испытаний» на шестой вход блока 1 управления в виде импульса с высоким активным уровнем, записывается в буферный регистр 14, а затем появляется на информационных входах параллелвной за п и си счетч и ка 17.

При записи информации в счетчик 16 на выходе дешифратора 18 происходит изменение состояния логической «1» в состояние логического «О». Тогда на выходе элемента НЕ 20 происходит изменение состояния логического «О» в состояние логической «1».

Вследствие этого на выходе элемента ИЛИ—

НЕ 22 происходит изменение состояния логической «1» в состояние логического «О», Информация с шины «Логическое значение разряда команды» поступает на третий вход регистра 6. Стробирующий сигнал поступает с шины «Строб записи логического значения разряда команды» на четвертый вход блока 1 управления в виде импульса с высоким активным уровнем и подается на вход вычитания счетчика 16, происходит уменьшение содержимого счетчика на единицу. Ин1О формация с шины «Адрес кольцевого сдвигового регистра» поступает на первую группу входов дешифратора 5. При появлении на шине «Строб записи адреса кольцевого сдвигового регистра» импульса с низким активным уровнем, который поступает на второй вход дешифратора 5 адреса кольцевого сдвигового регистра, на выходе дешифратора 5, который соответствует коду адреса кольцевого сдвигового регистра 4, появляется импульс с низким активным уровнем, по перепаду которого из состояния логического «О» в состояние логической «1» происходит запись логического значения разряда команды в соответствующий триггер 37 регистра 6.

При записи логических значений всех разрядов тестовой команды или h разрядов тестовой команды (h=1, ..., К) в триггеры 37 регистра 6 в зависимости от кода длины команды, записанный в буферный регистр 11, счетчик 16 обнуляется. В результате этого на выходе элемента НЕ 20 происходит изменение уровня логической «1» в уровень логического «О». Состояние триггера 23 остается неизменным, так как на его входе установки в «1» находится уровень логического

«О». На выходе элемента ИЛИ вЂ” HE 22 происходит изменение уровня логического «О» в уровень логической «1». На третий вход всех кольцевых сдвиговых регистров 4 подается логическая «1», чем обеспечивается

«обрыв» обратной связи между "старшим разрядом регистра 36 сдвига и его входом последовательного занесения при сдвиге впра40 во D j через элемент И вЂ” ИЛИ 35. Логическое значение h-го разряда тестовой команды с h-ro триггера 37 подается на второй вход кольцевого сдвигового регистра 4. Кроме этого, по перепаду уровня из состояния ло45 гического «О» в состояние логической «1» на выходе элемента ИЛИ вЂ” НЕ 22 формирователь 27 импульса вырабатывает импульс с высоким активным уровнем, который через элемент ИЛИ 31 подается на четвертые входы всех кольцевых сдвиговых регистров 4.

В результате этого происходит запись тестовой команды в первые разряды регистров 36 сдвига. Импульс с выхода формирователя 27 импульса через элемент ИЛИ 31 подается на вторые входы всех формирователей 2 остатка группы 1 и группы 2, таким у образом, происходит загрузка генераторов

m-последовательности. Кроме этого, импульс с выхода формирователя 27 импульса подается на вход формирователя 29 импуль1383364

55 са, который по перепаду из состояния логического «О» в состояние логической «1» формирует импульс с низким активным уровнем. Этот импульс подается на вход параллельной записи счетчика 17. Код числа испытаний, который находится на информационных входах параллельной записи счетчика 17, записывается в счетчик. В результате этого на выходе дешифратора 19 появляется уровень логического «О», а на выходе элемента НЕ 21 появляется уровень логической «1», который подается на входы 1 и К и на вход установки в «1» триггера 23, а также на входы установки в «1» триггеров 24 и 28. Импульс с высоким активным уровнем, с выхода формирователя 29 импульса, также поступает на вход параллельной записи счетчика !6, в который переписывается информация с группы выходов буферного регистра 11. На выходе дешифратора

l8 будет перепад уровня состояния логической «1» в состояние логического «О», а на выходе элемента HE 20 происходит изменение уровня из состояния логического «О» в состояние логической «1». В результате этого на выходе элемента ИЛИ вЂ” НЕ 22 появляется перепад уровня из состояния логической «1» в состояние логического «О», чем обеспечивается восстановление обратной связи в кольцевых сдвиговых регистрах 4, так как на третьи входы всех кольцевых сдвиговых регистров 4 подается уровень логического «О». Импульс с высоким активным уровнем с выхода формирователя 27 импульса поступает на вход синхронизации С триггера 24, в результате этого на инверсном выходе триггера 24 появляется уровень логической «1», который подается на первый вход элемента И 26 и разрешает прохождение импульсов с генератора 25 тактов на вход синхронизации С триггера 28.

Первый импульс, поступивший на вход синхронизации С триггера 28, устанавливает на его инверсном выходе уровень логической

«1», обеспечив этим прохождение импульсов с выхода генератора 25 тактов через элемент И 30. Импульсы с выхода элемента И 30 через элемент ИЛИ 31 поступают на вторые входы формирователей 2 остатка группы 1 и группы 2, обеспечивая этим начальную загрузку регистров 33 сдвига. В течении первых г d тактов работы (r = количеству импульсов сдвига, 4 = количеству разрядов регистра 33 сдвига формирователей 2 остатка группы 1 и группы 2) происходит последовательное заполнение регистров 33 сдвига группы 2 фрагментами m-последовательности с одновременным формированием сигнатур и подачей на шину данных контролируемого цифрового блока 10 тестовых наборов, содержащих большое количество логических нулей. Последовательное соединение выхода каждого i-го формирователя 2 остатка группы 1 с третьим входом (i+I)-го формирователя 2 остатка группы 1 и парал5

40 лельное соединение выхода каждого i-го формирователя 2 остатка группы 1 с третьим входом i-го формирователя 2 остатка группы 2 через сумматор 3 по модулю два обеспечивает заполнение каждого i-го регистра

33 сдвига фрагментами m-последовательности, что исключает какую бы то ни было корреляцию тестовых сигналов между выводами контролируемого цифрового блока 10, являющимися либо входами, либо выходами.

Эргодические свойства первого формирователя 2 остатка группы 1 обеспечиваются соединением его третьего входа с шиной

«CONST!», которая представляет собой вывод резистора, другой вывод которого соединен с положительным полюсом источника питания, гарантируя ненулевое состояние регистра 33 сдвига уже после первого тактового импульса. Через r d тактов работы устройства обеспечивается дальнейшая подача тестовых воздействий с вероятностью логических единиц в последовательности

Р = 0,5. Функционирование каждого формирователя 2 остатка группы 1 и группы 2 как генератора m-последовательности обеспечивается последовательным соединением выхода каждого i-го формирователя 2 остатка группы I с третьим входом (!+ I)-го формирователя 2 остатка группы 1 и параллельным соединением выхода каждого i-го формирователя 2 остатка группы 1 с третьим входом i-формирователя 2 остатка группы 2 через сумматор 3 по модулю два. Подключение в обратную связь регистра 33 сдвига формирователя 2 остатка группы 2 сигнала через сумматор 3 по модулю два с выхода контролируемого цифрового блока 10 не приводит к нарушению вероятностных свойств m-последовательности, генерируемым данным формирователем 2 остатка за счет суммирования по модулю два выходного сигнала контролируемого цифрового блока 10 с m-последовательностью, вырабатываемой формирователями 2 остатка группы 1.

Тактовые импульсы с выхода элемента ИЛИ 31 также поступают на четвертые входы кольцевых сдвиговых регистров 4, обеспечивая этим мультипликацию тестовых команд. Время мультипликации T..==m T. (m = числу рабочих тактов (испытаний) ) (т = времени длительности одного такта) .

Во время контроля на командную шину цифрового логического блока 10 с кольцевых сдвиговых регистров 4 подается одна и та же тестовая команда или ТП для различных наборов данных, поступающих с формирователей 2 остатка группы 2 в течение времени Т . Причем, чем больше будет время Т., тем больше для одной ТП поступает наборов данных на шину данных контролируемого цифрового блока 10, следовательно, тем больше значение вероятности обнаружения неисправности. Время формирования новой тестовой команды: Т- =

1383364

h !об (!об = времени обращения к памяти, считывания одного логического значения тестовой команды из памяти и заполнения одного триггера 37 регистра 6). Присоединение новой тестовой команды к концу ТП происходит при завершении рабочего такта.

Для повышения эффективности динамического контроля необходимо выполнение следующего условия: Т".(Т(Т+Лт (Лт == времени завершения первого рабочего такта после формирования новой тестовой команды). Первое неравенство указывает на то, что в процессе контроля не происходит прекращение работы кольцевых сдвиговых регистров 4, связанного с ожиданием конца формирования кода новой тестовой команды. При равенстве Т-«и Т, новая тестовая команда записывается в кольцевые сдвиговые регистры 4 сразу же после завершения ее формирования в регистре 6.

Тактовые импульсы с выхода элемента И 30 также подаются на вход вычитания счетчика 17, в который записан код числа испытаний (количество мультипликаций).

Одновременно происходит формирование новой тестовой команды во входном регистре 6. Количество записанных логических значений разрядов тестовой команды во входной регистр 6 вычитается из счетчика 16 поступлением на его вход вычитания стробирующих импульсов с высоким активным уровнем с четвертого входа блока 1 управления, который соединен с шиной «Строб записи логического значения разряда команды».

Рассмотрим два случая функционирования устройства.

Случай I. Содержимое счетчика 17, в который был записан код числа испытаний, стало равным нулю и после этого завершено формирование кода новой команды во входном регистре 6. В этом случае, при обнулении счетчика 17 на выходе дешифратора 19 появляется уровень логической «1», а на выходе элемента 21 НЕ появляется уровень логического «О». В результате этого на выходе триггера 23 подтверждается значение уровня логической «1», а на инверсном выходе триггера 24 и на инверсном выходе триггера 28 устанавливаются уровни логического

«О», следовательно, происходит запрещение прохождения тактовых импульсов с генератора 25 тактов через элемент И 30 на вторые входы формирователей 2 остатка группы 1 и группы 2, на четвертые входы кольцевых сдвиговых регистров 4 и на вход элемента 7 задержки синхроимпульсов. Кроме этого, на втором входе элемента ИЛИ 22 появляется уровень логического «О». После завершения формирования кода новой команды во входном регистре 6 обнуляется счетчик 16, а на выходе дешифратора 18 появляется уровень логической «1», тогда на выходе

55 элемента НЕ 20 устанавливается уровень логического «О». В результате этого на выходе элемента ИЛИ вЂ 22 появляется перепад уровня из значения логического «0» в значение логической «1». Происходит запись кода новой команды в кольцевые сдвиговые регистры 4, и процесс мультиплицирования повторяется (фиг. 6).

Случай 2, Содержимое счетчика 17, в который был записан код числа испытаний, не стало равным «нулю», а код новой тестовой команды уже сформировался во входном регистре 6. При незавершении процесса мультиплицирования ТП на выходе элемента НЕ 21 находится уровень логической «I».

При завершении формирования кода новой тестовой команды во входном регистре 6 обнуляется счетчик 16, на выходе дешифратора 18 появляется перепад уровня из состояния логического «О» в состояние логической

«1», на выходе элемента НЕ 20 появляется перепад уровня из состояния логической «1» в состояние логического «О». На выходе элемента ИЛИ в НЕ 22 сохраняется уровень логического «О», так как на его втором входе находится уровень логической «1». На вход синхронизации С триггера 23 с элемента

НЕ 20 поступает импульс с высоким активным уровнем, который устанавливает на выходе триггера 23 уровень логического «0», так как на входы 1 и К триггера 23 подан уровень логической «1» с выхода элемента

НЕ 21. Уровень логического «О», поданный с выхода триггера 23 на первый выход блока 1 управления, который соединен с шиной

«Готовность», означает, что генератор тестовых последовательностей команд должен прекратить подачу логических значений разрядов тестовой команды во входной регистр 6. При завершении процесса мультиплицирования обнуляется счетчик 17, на выходе дешифратора 19 появляется уровень логической «1», на выходе элемента НЕ 21 появляется уровень логического «О». Прекращается подача тактовых импульсов через элемент И 30 на вторые входы формирователя 2 остатка группы 1 и группы 2, на четвертые входы кольцевых сдвиговых регистров 4 и на вход элемента 7 задержки синхроимпульсов, так как на инверсных выходах триггеров 24 и 28 появляются уровни логического «О». На выходе элемента

ИЛИ вЂ” НЕ 22 появляется перепад уровня из состояния логического «О» в состояние логической «1», так как на первом входе этого элемента находится уровень логического

«О». В результате этого происходит запись кода новой тестовой команды в кольцевые сдвиговые регистры 4. Перепад уровня из состояния логической «1» в состояние логического «О» на выходе элемента НЕ 21 устанавливает на выходе триггера 23 уровень логической «1». Этим будет обеспечено разрешение подачи логических значений разрядов

1383364

12 новой тестовой команды во входной регистр 6

После записи новой тестовой команды в кольцевые сдвиговые регистры 4 по перепаду уровня из состояния логического «О» в состояние логической «1» на выходе элемента ИЛИ вЂ” НЕ 22 процесс мультиплицирования происходит с новой тестовой командой (ТП) (фиг. 7).

Код числа испытаний, который записывается в буферный регистр 14, должен быть кратен количеству разрядов регистра 36 сдви га, чтобы при обнулении счетчика 17 ТП заняла свое исходное состояние в кольцевых сдвиговых регистрах 4.

В процессе работы устройства можно изменить код длины команды и код числа испытаний. Это можно сделать записав в буферный регистр 11 и в буферный регистр !4 соответственно новый код длины команды и новый код числа испытаний в момент времени, когда на шине «Готовность» находится уровень логического «О».

Для обеспечения достоверности процесса контроля повторители 8 с тремя состояниями управляются по шине «Направление передачи», которая соединена с вторыми входами повторителей 8 с тремя состояниями.

В те такты процесса контроля, когда двунаправленная шина данных контролируемого цифрового блока 1О работает в режиме приема информации в контролируемый цифровой блок 10 на шине « Направление передачи» устанавливается уровень логического

«О», когда двунаправленная шина данных контролируемого цифрового блока 10 работает в режиме выдачи- информации из контролируемого цифрового блока 10 на шине

«Направление передачи» устанавливается уровень логической «1».

Вычисленные сигнатуры индицируются блоком 9 индикации и сравниваются с сигнатурами, полученными в результате проверки исправного цифрового блока или математического моделирования. Контролируемый цифровой блок считается исправным, если указанные сигнатуры совпадают.

Таким образом, использование предлагаемого устройства позволяет эффективно контролировать цифровые блоки, содержащие микропроцессоры и микропроцессорные БИС на их рабочей частоте с высокой достоверностью за счет мультиплицирования ТП с различными наборами данных. При этом предлагаемое устройство для контроля цифровых блоков не требует разделения режимов начальной загрузки формирователей 2 остатка группы 1 и группы 2 и непосредственного режима контроля.

Формула изобретения

Устройство для контроля микропроцессорных цифровых блоков, содержащее 2f формирователей остатка, где t, — разрядность двунаправленной шины данных контролируемого блока, блок индикации, блок управления, причем входы синхронизации с первого по 2(-й формирователей остатка соединены с первым выходом блока управления, выходы с первого по (t — )-й формирователей остатка соединены с информационными входами соответственно с второго по

1-й формирователей остатка, информационный вход первого формирователя остатка подключен к входу единичного потенциала устройства, отличающееся тем, что, с целью повышения достоверности контроля, оно содержит К кольцевых сдвиговых регистров, где К вЂ” разрядность командной шины

15 контролируемого блока, дешифратор, 1 сумматоров по модулю два, f повторителей с тремя состояниями, регистр и элемент задержки, причем первый выход блока управления соединен с входами синхронизации с первого по К-й кольцевых сдвиговых регистров и через элемент задержки с выходом устройства для подключения к синхровходу контролируемого блока, второй выход блока управления соединен с входами записи с первого по К-й кольцевых сдвиговых регистров, вход начальной установки устройства подключен к входам сброса с первого по К-й кольцевых сдвиговых регистров, с первого по 2(-й формирователей остатка, к входу сброса регистра и к входу начальной установки блока управления, вход кода

30 номера кольцевого регистра устройства подключен к информационному входу дешифратора, группа выходов которого соединена с группой разрядных входов синхронизации регистра, информационный вход которого является информационным входом устрой35 ства, выходы разрядов регистра соединены с информационными входами с первого по .

К-й кольцевых сдвиговых регистров, выходы которых образуют выход устройства для подключения к входу команд контролируемого

40 блока, выходы с первого по l-й формирователей остатка соединены с первыми входами соответственно с первого по 1-й сумматоров по модулю два, выходы с первого по t-й сумматоров по модулю два соединены с информационными входами соответственно с

45 (1+1) -го по 21-й формирователей остатка, первый и второй входы логических условий блока управления являются соответственно входами кода длины команды и кода числа испытаний устройства, первый, второй и третий входы синхронизации блока управления

50 являются соответственно первым, вторым и третьим синхровходами устройства, третий выход блока управления является выходом готовности устройства, группа входов-выходов устройства для подключения к входамвыходам данных контролируемого блока подключена к выходам соответственно с первого по !й повторителей с тремя состояниями и к вторым входам соответственно с первого по 1-й сумматоров по модулю два, выходы

1383364

15

Ни уС

Стр логи раор о о оо спгс ссо ис

Фиг.2

13 с ((+1)-го по 2t-й формирователей остатка соединены с информационными входами соответственно с первого по f-й повторителей с тремя состояниями, входы направления передачи которых подключены к входу направления передачи устройства, группы выходов с (1+1)-го по 2f-й формирователей остатка соединены с группой входов блока индикации, вход синхронизации дешифратора подключен к входу записи, первый и второй входы константы блока управления подключены к входам соответственно нулевого и единичного потенциалов устройства, причем блок управления содержит два буферных регистра, два счетчика, два дешифратора, два формирователя импульсов, три триггера, элемент задержки, три элемента НЕ, три элемента И, элемент

ИЛИ вЂ” НЕ, элемент ИЛИ и генератор тактов, причем вход начальной установки блока управления подключен к входам сброса первого и второго буферных регистров и к входу первого элемента НЕ, выход которого соединен с входами сброса первого и второго счетчиков, первый вход синхронизации блока управления подключен к счетному входу первого счетчика информационный вход которого соединен с выходом первого буферного регистра, информационный вход которого является первым входом логических условий блока управления, второй вход синхронизации блока управления подключен к синхровходу первого буферного регистра и через элемент задержки к первому входу первого элемента И, выход которого соединен с входом записи первого счетчика, выход которого соединен с информационным входом первого дешифратора, выход которого через второй элемент НЕ соединен с синхровходом первого триггера и первым входом элемента ИЛИ в НЕ, выход которого соединен с входом первого формирователя импульсов и является вторым выходом блока управления, информационный вход второго буферного регистра является вторым входом логических условий блока управления, третий вход синхронизации блока управления подключен к синхровходу второго буферного регистра, выход которого соединен с информационным входом второго счетчика, выход которого соединен с информационным входом второго дешифратора, выход которого через третий элемент НЕ соединен с вторым входом элемента ИЛИ вЂ” НЕ, с I, К и S-входами первого триггера и с 5-входами второго и третьего триггеров, выход генератора тактов соединен с первыми входами второго и третьего элементов И, выход первого формирователя импульсов соединен с входом второго формирователя импульсов, с первым входом элемента ИЛИ и синхровходом второго триггера, инверсный выход которого соединен с вторым входом второго элемента И, выход которого соединен с синхровходом третьего триггера, инверсный выход которого соединен с вторым входом 5 третьего элемента И, выход которого соединен со счетным входом второго счетчика и с вторым входом элемента ИЛИ, выход которого является первым выходом блока управления, выход второго формирователя импульсов соединен с входом записи второго

30 счетчика и с вторым входом первого элемента И, выход первого триггера является третьим выходом блока управления, 1-вход третьего триггера подключен к первому входу константы блока управления, второй вход константы блока управления подключен к

35 1 и К-входам второго триггера и к К-входу третьего триггера.!

383364

&77 1

НЙЧЮЯб НОЯ

ycmaw/ка гр.Ю) 8а 10

На Ф йпХ

На 4.

Рт3 (Рю гр7) 0m 5 (lA)F zt z) От1

ИаЧаПЬНай усманидю

° I ° °

Жг1а5 (Фя гр.I)

Ую/ (Фю гр.E) 1383364

Вых 20

Вых 22

Вых 27 дик гд

Ьм 22 д. «22 дн» 51

Внк гд дн, гг дн» гЬ днк 2д дэи 28

Вы Ze

Внк JO

Вык ВО ди«гд

Вык 2В амид 6

Уиг. 7

Ha vansea 27 усл7ано Ука

omo8 носим

/!оо олины ккомянОБ/ проо заяиси адРВса юльце&га с36игобого егиспра

Фиг. В

Составитель Д. Ванюхин

Редактор Р. Гербер Техред И. Верес Корректор Л. Патай

Заказ 9!4/48 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, кК вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Сгпроо >anuses коРа Рлины кок7а.нды

Кор числа.

ucnbimuauu.

Строд2 записи коФа числа ис2дытаний

Логическое значение раяряРа команд

Ипроо заки и логического значения раэряРа

КОЛдаНгйх

Андрес кольцедого сИигооога региащю

Вых В/

Вых 2В

Вых 2/

Вых 24

Вык 26