Устройство для определения прогнозных оценок случайного процесса

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения - повышение достоверности прогноза . Устройство Содержит умножитель 1, блок 2 выработки экспоненциальной функции, сумматор 3, блок деления 4, блок памяти 5, первую 6 и вторую 7 группы элементов И, вторую 8 и первую 9 группы элементов ИЛИ, элементы задержки 10-13, вход установки нуля 14, входы 15-19 управления записью исходных параметров, пгану 20 задания исходных параметров, вход 21 запуска и выход 22. Устройство реализует вычисление прогноза по формуле, являющегося одним из решений уравнения Бернулли. I ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (50 4 G 06 G 7/30

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ / " .

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

Я ts

{2l) 4137254/24-24 (22) 21.10.86 (46) 23.03.88. Бюл. 11 11 ° (72) В.Д. Боев, А.Е. Филюстин и В.А. Волков (53) 681.3(088.8) (56) Авторское свидетельство СССР

У 333571, кл. G 06 G 7/52, 1970.

Авторское свидетельство СССР

В 1003108, кл. G 06 G 7/30, 1983. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

ПРОГНОЗНЫХ ОЦЕНОК СЛУЧАЙНОГО ПРОЦЕССА (57) Изобретение относится к вычислительной технике. Цель изобрете„„SU„„1383406 А 1 ния — повышение достоверности прогноза. Устройство содержит умножитель 1, блок 2 выработки экспоненциальной функции, сумматор 3, блок деления 4, блок памяти 5, первую 6 и вторую 7 группы элементов И, вторую 8 и первую 9 группы элементов ИЛИ, элементы задержки 10-13, вход установки нуля 14, входы 15-19 управления записью исходных параметров, шину 20 задания исходных параметров, вход 21 запуска и выход 22. Устройство реализует вычисление прогноза по формуле, являющегося одним иэ решений уравнения Бернулли. 1 ил.

1383406

Изобретение относится к вычислительной технике, Цель изобретения — повышение достоверности прогноза.

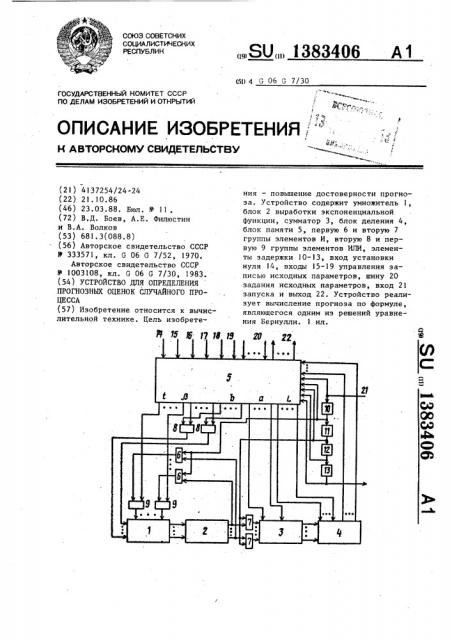

На чертеже показано предлагаемое устройство.

Устройство содержит умножитель 1, блок 2 выработки экспоненциальной функции, сумматор 3, блок 4 деления, блок 5 памяти, выполненный на регистрах, первую 6 и вторую 7 группы элементов И, вторую 8 и первую 9 группы элементов ИЛИ, элементы 10-13 задержки с первого по четвертый, вход 14 установки нуля, входы 15-19 управления записью исходных параметров, шину 20 задания исхсдных параметров, вход 21 запуска и выход 22.

Устройство работает следующим образом.

Устройство реализует одно из решений управления Бернулли. Последнее часто используется для получения прогнозных оценок сложных событий веро.25 ятностного типа. Решение уравнения имеет вид —

a+exp(be " )

30 оно более гибко аппроксимирует статистические данные„ чем используемые более простые решения (уравнения

Перла или Гомпертца).

В начале работы регистры блока 5 памяти обнуляются сигналом с вхоца

14. Затем в соответствующие регистры блока памяти заносятся последовательно исходные параметры р,b,à,L с шины

20, поступление которых синхронизиро- 40 вано сигналами с входов 15-19. После этого на вход 21 поступает сигнал запуска, по которому очищается регистр результата блока 5 памяти, параметры

С и р поступают на умножитель 1, а 4 результат умножения — на блок 2 выработки экспоненциальной функции.. По окончании работы блока 2 на выходе элемента задержки появляется сигнал, перемножаются параметр в и получен50 ная ранее .экспонента, Результат второго перемножения снова подвергается экспоненциальному преобразованию в блоке 2 и по сигналу с элемента I .1 задержки поступает в сумматор 3, где складываются с параметром а, считываемым иэ блока памяти.. После деления параметра L на полученную сумму результат заносится в регистр блока памяти и поступает на выходную шину устройства. Сигнал на выходе элемента 13 свидетельствует об окончании вычислений.

Ф о р м у л а и з о б р е т ения

Устройство для определения прогнозных оценок случайного процесса, содержащее блок памяти, сумматор, умножитель, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности прогноза, оно содержит блок деления, блок выработки экспоненциальной функции, две группы элементов ИЛИ, две группы элементов И и четыре элемента задержки, соединенные последовательно, причем вход первого из них соединен с входом запуска устройства и входом управления считыванием первого и второго исход- . ных параметров блока памяти, выход первого элемента задержки соединен с входом управления считыванием третьего исходного параметра блока памяти и первыми входами элементов И первой группы, выход второго элемента задержки соединен с входом управления считыванием четвертого исходного па раметра блока памяти и первыми входами элементов И второй группы, выход третьего элемента задержки соединен с входом управления считыванием пятого исходного параметра блока памяти, S а выход четвертого элемента задержки — с входом записи результата вычислений блока памяти, первый информационный вход блока памяти соединен с шиной задания исходных параметров, а управляющие входы обнуления и записй соответствующих исходных параметров блока памяти соединены с соответствующими управляющими входами устройства, кодовый выход первого исходного параметра соединен с первыми входами элементов И первой группы, вторые входы которых соединены с входами элементов И первой группы, выходы элементов ИЛИ первой группы соединены с первым кодовым входом умножителя, кодовые выходы второго и третьего исходных параметров блока памяти через вторую группу элементов ИЛИ соединеиы с вторым кодовым входом умножителя, выход которого соединен с входом блока выработки экспоненциальной функции, кодовый выход которого соединен с вторыми входами элементов И первой и второй групп, BbIxo1383406

Составитель Р. Осипов

Редактор Н. Рогулич . Техред М.Дидык корректор Л. Патай,Заказ 1298/50 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ды элементов И.второй группы соединены с первым кодовым входом сумматора, второй кодовый вход которого соединен с кодовым выходом четвертого исходного параметра блока памяти, кодовый выход сумматора соединен с входом делителя блока деления, вход делимо-.

ro которого соединен с кодовым выходом пятого исходного параметра блока памяти, а.выход блока деления,соединен с вторым информационным входом блока памяти, информационный выход результата которого является выходом устройства.