Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах обработки информации. Цель изобретения - повышение быстродействия устройства. Устройство содержит блоки памяти 1, дешифратор 2, элементы ИЛИ 3, элементы И 10, 11. Поставленная цель достигается за счет одновременной записи информации во все блоки памяти. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 G 11 С 11 00 (,(" ." i s;, " - 9

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (ОПИСАНИЕ ИЗОБРЕТЕНИЯ .. .,—

М А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4106092/24-24 (22) 20.05.86 (46) 23.03.88. Бюл. № 1 (72) А. А. Кузнецов и В. П. Онышко (53) 327.681.6 (088.8) (56) Авторское свидетельство СССР № 1095233, кл. G 11 С ll/00, 1983.

Майоров С. А., Новиков Г. И. Принципы организации цифровых машин.— Л.: Машиностроение, 1974, с. 380 — 381, рис. 1,0.12..80 1383441 А 1 (54) ОПЕРАТИВ НОЕ ЗАПОМИ НА1ОШЕЕ

УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах обработки информации. Цель изобретения— повышение быстродействия устройства. Устройство содержит блоки памяти 1, дешифратор 2, элементы ИЛИ 3, элементы И 10, 11.

Поставленная цель достигается за счет одновременной записи информации во все блоки памяти. 1 ил.

1383441

Формула изобретения

Составитель С. Шустенко

Редактор H. Рогулич Техред И. Верес Корректор О. Кравцова

Заказ 919/52 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах обработки информации.

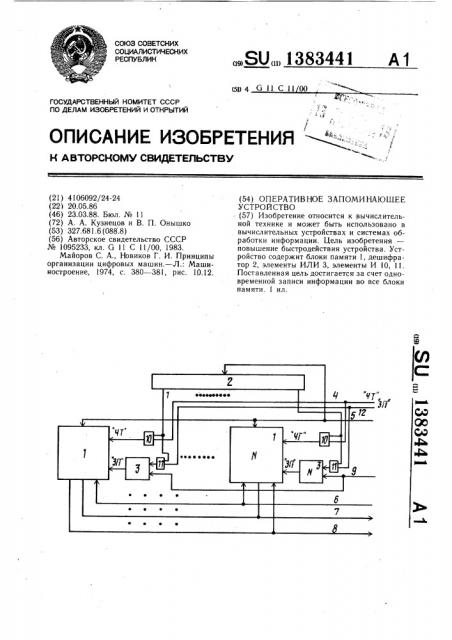

Цель изобретения — повышение быстродействия устройства, На чертеже приведена структурная схема устройства.

Устройство содержит блоки 1 памяти, дешифратор 2, элементы ИЛИ 3, вход 4 чте ния, адресные входы 5, вход 6 записи, информационные выходы 7, выход 8 идентификации, вход 9 группового чтения, элементы И 10 и 11 и вход 12 записи.

Устройство работает следующим образом.

При обращении к устройству на вход 5 15 адреса поступает т-разрядный адрес, старшие К разрядов которого поступают на дешифратор 2 и являются адресом N блоков памяти, младшие т-К разрядов которого поступают на адресные входы N блоков памяти.

На одном из выходов дешифратора 2 вырабатывается сигнал разрешения выборки, блока памяти, который поступает на входы соответствующих элементов И 10 и 11 и разрешает прохождение сигналов «Запись» («ЗП») и «Чтение» («ЧТ») на соответствующий блок памяти.

При выполнении процедуры записи на входе 9 сигнал отсутствует, на входы 6 подаются записываемые данные, которые за, писываются в блок памяти, номер которого определяет дешифратор 2. При выполнении 30 процедуры чтения на входе 9 сигнал также отсутствует. Блок памяти, номер которого определяет дешифратор 2, выставляет на вы, ходах 7 считываемые данные.

Выход 8 идентификации отмечает период занятости соответствующего блока памяти, При обнулении N блоков памяти или заполнении их однородной информацией во время тестирования младшие т-К разрядов адреса шины 5 адреса поступают на адресные входы N блоков памяти. На входы 6 подаются записываемые данные. На вход 9 подается сигнал, являющийся обобщенным сигналом записи, поступающий через элементы ИЛИ на входы записи блоков памяти.

По этому сигналу информация с входов 6 записывается сразу во все блоки памяти.

Оперативное запоминающее устройство, содержащее блоки памяти, адресные входы которых являются адресными входами первой группы устройства, дешифратор, входы которого являются адресными входами второй группы устройства, информационные входы и выходы блоков памяти являются соответственно информационными входами и выходами устройства, элементы И первой группы, элементы И второй группы, выходы дешифратора подключены к первым входам соответствующих элементов И первой и второй групп, выходы элементов И первой группы подключены к входам чтения соответствующих блоков памяти, вторые входы элементов И первой группы объединены и являются входом чтения устройства, вторые входы элементов И второй группы объединены и являются входом записи устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит элементы ИЛИ, выходы которых подключены к входам записи соответствующих блоков памяти, первые входы элементов

ИЛИ подключены к выходам соответствующих элементов И второй группы, вторые входы элементов ИЛИ объединены и являются входом групповой записи устройства.