Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для диагностического контроля блоков памяти. Целью изобретения является расширение диагностических возможностей за счет подсчета количества ячеек, :хранящих постоянный ноль или единицу, либо количества закороченных ячеек. Устройство содержит блок управления, счетчик адреса, блок сравнения , первый, второй и третий счетчики ошибок , ключи, элементы И, ИСКЛЮЧАЮЩЕЕ ИЛИ и НЕ, триггер. В устройстве по каждому адресу Л, осуш,ествляются запись информации и чтение информации, затем производится чтение информации по адресу Ai+. Контроль проводится для прямых и инверсных кодов информации. В случае обнаружения ошибок происходит инкрементирование соответствующего счетчика ошибок. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5D 4

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

3(;

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ В3 р,„;, (21) 4100189/24-24 (22) 04.08.86 (46) 23.03.88. Бюл. № 11 (72) В. В. Дмитриев, А. Г. Солошенко, С. Д. Малахов, С. А. Косарев и А. Н. Дебальчук (53) 621.327.6 (088.8) (56) Авторское свидетельство СССР № 926725, кл. G ll С 29/00, 1980.

Авторское свидетельство СССР № 1051586, кл. G 11 С 29/00, 1982. (54) УСТРОЙСТВО ДЛЯ КО НТРОЛЯ

БЛОКОВ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для диагностического контроля блоков памяти.

„„SU„„1383449 А1

Целью изобретения является расширение диагностических возможностей за счет подсчета количества ячеек, хранящих постоянный ноль или единицу, либо количества закороченных ячеек. Устройство содержит блок управления, счетчик адреса, блок сравнения, первый, второй и третий счетчики ошибок, ключи, элементы И, ИСКЛЮЧАЮШЕЕ

ИЛИ и НЕ, триггер. В устройстве по каждому адресу Л; осуществляются запись информаций и чтение информации, затем производится чтение информации по адресу А;+ .

Контроль проводится для прямых и инверсных кодов информации. В случае обнаружения ошибок происходит инкрементирование соответствующего счетчика ошибок. 2 ил.

1383449

Изобретение относится к вычислительной технике и может быть использовано для диаг ностического контроля блоков памяти.

Цель изобретения — расширение диагностических возможностей за счет подсчета количества ячеек, хранящих постоянный ноль или единицу, либо количества закороченных ячеек.

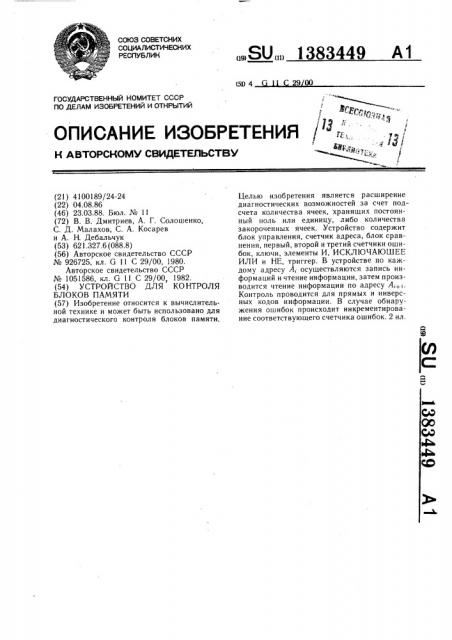

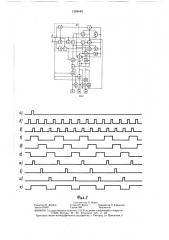

На фиг. 1 приведена схема устройства для контроля блоков памяти; на фиг. 2 временные диаграммы, поясняющие принцип работы устройства.

Устройство содержит ключ 1, элемент 2 задержки, вход 3 синхронизации, ключ 4-, ! триггер 5, делитель 6, дешифратор 7, счет чик 8 адреса, элементы И 9 — 11, контролируемый блок 12, элемент И 13, элемент !

ИСКЛЮЧАЮШЕЕ ИЛИ 14, блок 15 сравне.:ния, триггер !6, дешифратор 17, элемент HE 18, ключи 19 — 21, счетчики 22 — 24 ошибки, ;блоки 25 — 27 памяти, индикаторы 28 — 30 и . вход 31 начальной установки. Элементы 1, 2, 4 — 7 и 11 представляют собой блок 32

;управления.

Устройство работает следующим образом.

В исходном состоянии на выходе триг тера 5 присутствует низкий потенциал, поступающий на управляющие входы ключей 1 и 4 и запрещающий прохождение синхроимпульсов, поступающих на шину 3 синхронизации, на вход делителя 6 и входы элементов И 9 — 11 и 13. При поступлении на шину 31 управления импульса установки (фиг. 2а) обнуляются делитель 6, счетчики

8 и 22 — 24, триггер 16 и устанавливается высокий потенциал на выходе триггера 5.

Ключи 1 и 4 при этом открываются. На синхронизирующий вход делителя 6 начинают поступать синхроимпульсы (фиг. 2б) .

Делитель 6 осуществляет деление частоты синхроимпульсов с коэффициентом деления, равным 3. При этом на выходах дешифратора 7 формируются импульсные последовательности (фиг. 2г, д и е), которые поступают на первые входы соответственно элементов И 11, 9 и 10, 13. На вторые входы этих элементов поступают через ключ 1 задержанные (например, на половину периода) элементом 2 задержки синхроимпульсы (фиг. 2в). В результат» на выходах элементов И 1 и 10 формируются первая и вторая стробирующие импульсные последовательности (фиг. 2ж и з соответственно).

На выходах элементов И 9 и 13 сохраняются низкие потенциалы, так как их третьи входы соединены с выходом триггера 16. На выходе последнего после прихода импульса установки присутствует низкий потенциал, так как на информационный вход контролируемого блока 12 с выхода триггера 16 поступает низкий потенциал, то первым после импульса установки импульсом первой стробирующей последовате.пьности (фиг.

2ж) происходит запись «О» в ячейку блока памяти с номером I.

1О

В промежутке между первым и вторым импульсами первой стробирующей последовательности контролируемый блок 12 памяти воспроизводит информацию из ячейки памяти с номером 1 и ячейки с номером 2, так как отрицательным фронтом импульсной последовательности, поступающей с выхода дешифратора 7 на синхронизирующий вход счетчика 8 адреса, происходит переключение адресов ячеек контролируемого блока 12.

Затем производится запись «О» в ячейку памяти с номером 2 и воспроизведение информации из ячеек с номером 2 и 3. Одновременно воспроизводимая информация с выхода контролируемого блока 12 поступает на первый вход схемы 15 сравнения, второй вход которой соединен с выходом элемента ИСКЛЮЧАЮШЕЕ ИЛИ 14, на первый вход которого поступает низкий уровень с выхода триггера 16, а на второй вход — импульсная последовательность с третьего выхода дешифратора 7 (фиг. 2е).

Полученные в результате сравнения импульсы ошибки поступают на информационные входы ключей 19 — 21, управляющие входы которых соединены с выходами элементов И 9, 10 и 13 соответственно. Ключи 19 и 21 закрыты низким потенциалом с выходов элемента И 9 и 13. На управляющий вход ключа 29 поступает вторая стробирующая последовательность (фиг. 2з), выделяющая ошибки только в моменты воспроизведения информации из ранее записанной ячейки памяти контролируемого блока 12, что позволяет выявлять неисправные ячейки памяти, на выходах которых постоянно присутствует высокий потенциал. Запись, воспроизведение «О» и сравнение производятся до полного заполнения всех ячеек контролируемого блока 12 нулевыми символами.

Отрицательным фронтом старшего разряда счетчика 8 адреса, выход которого соединен с входом триггера 16, последний переключается и íà его выходе устанавливается высокий потенциал, поступающий на информационный вход контролируемого блока

12 и разрешающий прохождение второй и третьей стробирующих последовательностей (фиг. 2з, и) с выходов элементов И 9 и 13 на управляющие входы ключей 18 и 21 соответственно. На выходе элемента И 10 устанавливается низкий потенциал, так как на его третий вход поступает низкий потенциал с выхода элемента HE 18. Первым после переключения триггера 16 импульсом первой стробирующей последовательности в ячейку контролируемого блока 12 с номером 1 производится запись «1» символа.

Затем производится воспроизведение содержимого из ячейки памяти с номерами 1 и 2.

Далее производится запись «1» символа в ячейку с номером 2 и воспроизведение информации из ячейки с номерами 2 и 3.

Воспроизводимая информация сравнивается на схеме 15 сравнения с последо1383449

4, 30

Формула изобретения

I вательностью, поступающей с выхода элемента ИСКЛЮЧАЮШЕЕ ИЛИ 14 (фиг. 2к).

Полученные в результате сравнения импульсы ошибки поступают на входы ключей

19 и 21, где стробируется второй и третьей стробирующими импульсными последовательностями (фиг. 2з, и) соответственно.

Таким образом, при заполнении ячеек памяти контролируемого блока 12 единичными символами на выходе ключа 19 выделяются ошибки, соответствующие ячейкам памяти, а на выходе коммутатора 21 ошибки, соответствующие закороченным между собой ячейкам. Запись «1» символа, считывание и сравнение записанной и считанной информации производится до заполнения всех ячеек памяти контролируемого блока 12 «1» символами. Дешифратор 17 выделяет импульс последнего адреса контролируемого блока, отрицательным фронтом которого переключается триггер 5, а нулевой потенциал на его выходе запирает ключи 1 и 4. Импульсы ошибок с выходов ключей 19 — 21 поступают на синхро-. низирующие входы счетчиков 22 — 24 соответственно, где они подсчитываются и их число отображается на индикаторах 28 — 30.

При этом, импульсами ошибки с выходов ключей 19 — 21, соответствующими виду ошибок, осуществляется запись адресов неисправных ячеек блока 12 памяти, задаваемых счетчиком 8 адреса, в блоки 25 — 27 памяти. Номера ячеек блоков 25 — 27 памяти, в которые записываются адреса неисправных ячеек контролируемого блока 12, задаются счетчиками 22 — 24.

Устройство для контроля блоков памяти, содержащее блок управления, первый синхровыход которого соединен с одноименным входом счетчика, разрядные выходы которого являются адресными выходами устройства, а выход переполнения подключен к установочному входу триггера, дешифратор, выход которого соединен с входом призна5

25 ка окончания контроля блока управления, выход записи-считывания которого является одноименным выходом устройства, блок сравнения, первый вход которого является информационным входом устройства, элемент НЕ, отличающееся тем, что, с целью расширения диагностических возможностей за счет подсчета чисел ячеек, хранящих постоянный ноль или единицу, либо числа закороченных ячеек, в устройство введены элемент ИСКЛЮЧАЮШЕЕ ИЛИ, первый, второй и третий элементы И, первый, второй и третий ключи, первый, второй и третий счетчики ошибок, причем первый и второй синхровыходы блока управления соединены соответственно с первыми входами первого и второго элементов И и с вторыми входами первого, второго и третьего элементов И, третий синхровыход блока управления подключен к первым входам третьего элемента И и элемента ИСКЛЮЧАЮШЕЕ ИЛИ, выход которого соединен с вторым входом блока сравнения, а второй вход подключен к выходу триггера, входу элемента НЕ, третьим входам первого и третьего элементов И, к одному входу дешифратора и является информационным выходом устройства, другие входы дешифратора соединены с выходами счетчика адреса, выход блока сравнения подключен к управляющим входам первого, второго и третьего ключей, импульсные входы которых соединены соответственно с выходами первого, второго и третьего элементов И, выходы первого, второго и третьего ключей являются выходами признаков ошибок устройства и подключены к синхровходам соответствующих счетчиков ошибок, выходы которых являются диагностическими выходами устройства, а входы начальной установки являются одноименным входом устройства и соединены с одноименными входами счетчика адреса, триггерами блока управления, вход синхронизации которого является одноименным входом устройства, выход элемента НЕ подключен к третьему входу второго элемента И.

1383449

Фиг/ а)

4 Л Л Л JLJLJL ) и п.ллл г)

el ж) Л з и) 1

"l Риг.2

Составитель О. Исаев

Редактор И. Дербак Техред И. Верес Корректор О. Кравцова

Заказ 919/52 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4