Преобразователь позиционного кода в вычет по модулю

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля по модулю и сопряжения. Целью изобретения является расширение области применения за счет возможности работы по произвольному основанию позиционной системы счисления. Поставленная цель достигается тем, что преобразователь позиционного кода в вычет по модулю, содержащий регистр 1 сдвига, группу элементов И 3, регистр. 4, блок 5 умножения по модулю, накапливающий сумматор 7 по модулю, содержит дешифратор 2 и блок 6 умножения по модулю с соответствующими связями. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСГ1УБЛИН (51)4 Н 03 M 7/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ / .r? ,?;. Ъ

-с4 j

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4140296/24-24 (22) 20.06.86 (46) 23 ° 03.88. Бюл. №- 11 (72) H.И.Червяков, Н.И.Швецов, А.П.Болтков и А.В..Шахов (53) 681. 3 (088. 8) (56) Авторское свидетельство СССР № 374596, кл. Н 03 М 7/18, 1970.

Авторское свидетельство СССР

¹ 983701, кл, Н 03 М 7/18, 1982 ° (54) ПРКОБРАЗОВАТКЛЬ ПОЗИЦИОННОГО

КОДА- В ВЫЧКТ 110 МОДУЛЮ (57) Изобретение относится к вычислительной технике и может быть исполь° Я0 РЫВИН А 1 зовано в устройствах контроля по модулю и сопряжения. Целью изобретения является расширение области применения за счет возможности работы по произвольному основанию позиционной системы счисления. Поставленная цель достигается тем, что преобразователь позиционного кода в вычет по модулю, содержащий регистр 1 сдвига, группу элементов И 3, регистр 4, блок 5 умножения по модулю, накапливающий сумматор 7 по модулю, содержит дешифратор 2 и блок 6 умножения по модулю с соответствующими связями. 2 ил.

138 >5()6

Изобретение относится к вычислительиой технике и может .быть испольг эовано для получения вычетов системы остаточных классон от чисел с q-м основанием в устройствах контроля по модулю и сопряжения.

Целью изобретения является расширение области применения эа счет возможности работы по произвольному основанию позиционной системы счисления.

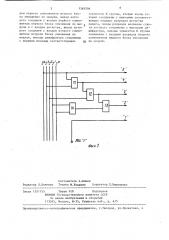

На фиг. 1 представлена схема преоб: разователя позиционного кода в вычет по модулю; на фиг. 2 — схема дешифра тора. 15

Преобразователь (фиг, 1) содержит регистр 1 сдвига, дешифратор 2, .группу элементов И 3, регистр 4„ блоки 5

6 умножения по модулю, накапливающий сумматор 7 по модулю, выход 8 пре-2О образователя, вход 9 основания позиционной системы счисления преобразователя, информационный вход 10 преобразователя.

Дешифратор (фиг, .2) содержит эле- 25 менты ИЛИ 11 — 13 и:элемент И 14 (для случая пятиразрядного основания позиционной системы).

Регистр 1 сдвига выполняет сдвиг в сторону младших разрядов на К раз- 3Q рядов

K--) 1o821 (+1 где ).(— ближайшее целое„ меньшее лиI бо равное.

Дешифратор 2 преоораэует код величины ц 0 нования пОзициОннОй системы счисления в код количества разрядов, необходимых для ее представления.

Вычисление вычета Ы; системы Ос- щ таточных классов по мсдулк Р от позиционного числа А происходит в преоб.разователе согласно следующей формулеа

Ф ь ., = — (W (А (P;, q; )modP)modP,

< о

У

А; — разрядная цифра числа А,"

m — разрядность числа А;

5О

Р-.q;; (, =P q;

Преобразователь работает следующим образом.

В исходном состоянии в регистр 1 записано преобра"=óåìîå число А, в регистр 4 — Обратная мультипликативная ае>-.,è÷èíà 1/<1 гюс1Р, накапливающий сумматор 7 по модулю обнулен,, на вход 9 подан код основания q;. ДешиФратор 2 c:âoèìè выходами в соотве-.— ствии с кодом и» его входе открь<вает соответствующие элементы Л 3, и на одном входе блока 5 умножения по модулю прис.утствует код младшей цифры

А, числа А, а на другом входе — код числа "1" с выхода блока 6 умножения по модулю, На выходе блока 5 умножения по модулю присутствует значение младшей группы А<. На первом этапе преобразования накапливающий сумматор 7 по модулю защелкивает значение

А„ а в регистре 1 происходит сдвиг информации на соответствующее количество разрядов. В регистр 4 записывается значение 1modP с выхода блока 6. При этом содержимое регистра 4 умножается по модулю Р на <1 в блоf ке 6 и подается, с одной стороны, на вход регистра 4 и, с.другой стороны, на один вход блока " умножения по модулю, на другом входе которого присутствует код значения А, произведение этих величин (А,q.)modP присутствует на выходе блока 5 умножения по модулю.

На втором этапе в накапливающий сумматор 7 по модулю записывается код величины ((А <1 ) modP+A„.)modP, в регистре 1 происходит очередной сдвиг информации. В дальнейшем процесс преобраэования продолжается аналогичным образом. формула и з О б р е т е н и я

Преобразователь позиционного кода в вычет по модулю, содержащий регистр сдвигаz первые блок умножения по модулю, накапливающий сумматор по модулю, регистр и группу элементов И, причем информационкьгй вход преобразователя соединен с входами разрядов регистра сдвига, ьыход первого блока,умножения по модул«< соединен с входом накапливающего сумматора по модулю, выход которого является выходом преобразсвателя. о тл и ч а ю шийся тем, что, с це-лью расширения области приме=.ения эа счет возможности работы пс произвольному основанию позиционной системы счисления„ он содсржит второй блок умножения по модулю и деши<рратор, причем. вход Основания позиционной системы счиспения преобразователя соединен с входом дешифргтора и с вхо1383506

ZeZ3ZzZ lZ g

Составитель А.Клюев

Редактор Л,Лангазо Техред M.Õoäàíè÷ Корректор Л.Пилипенко

Заказ 1351/55 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г,ужгород, ул.Проектная, 4 дом первого сомножителя второго блока умножения по модулю, выход которого соединен с входом первого сомножителя первого блока умножения по мо5 дулю и с входом регистра, выход которого соединен с входом второго сомножителя второго блока умножения по модулю, выходы дешифратора соединены с первыми входами соответствующих 1g элементов И группы, вторые входы которых соединены с выходами соответствующих младших разрядов регистра сдвига, входы разрядов величины сдвига которого соединены с выходами дешифратора, выходы элементов И группы соединены с входами разрядов второго сомножителя первого блока умножения по модулю.