Устройство для сопряжения каналов связи с эвм

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ÄÄSUÄÄ 1385129 А1 g 4 G 06 F 13/24

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2I) 3995602/24-24 (22) 21.11.85 (46) 30.03.88. Бюл. № 12 (72) В. И. Носков, В. В. Камшилин и А. И. Шилов (53) 681.325(088.8) (56) Авторское свидетельство СССР № 454555, кл. G 06 F 15/00, 1973.

Авторское свидетельство СССР № 562812, кл. G 06 F 13/00, 1977. (54) (57) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ КА НАЛОВ СВЯЗИ С ЭВМ, содержащее дешифратор, первый счетчик, регистр, четыре триггера, генератор импульсов, три элемента НЕ, два элемента ИЛИ, пять элементов И, группу элементов И, причем первый вход первого элемента И соединен с входом первого элемента НЕ и является информационным входом устройства для подключения к информационному выходу канала связи, единичный и нулевой входы первого триггера являются входами запрета и запуска устройства для подключения к выходам запрета и запуска ЭВМ соответственно, при этом выход первого элемента НЕ соединен с первым входом второго элемента И, второй вход которого соединен с нулевым выходом первого триггера, единичный выход которого соединен с вторым входом первого элемента И, выходы первого и второго элементов И соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен с входом второго элемента НЕ, выход которого соединен с входом третьего элемента НЕ, выход которого соединен с первыми входами элементов И группы, с первыми входами третьего и четвертого элементов И, с единичным входом второго триггера, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом генератора импульсов, выход пятого элемента И соединен со счетным входом первого счетчика, установочный вход которого соединен с нулевым входом второго триггера и с выходом второго элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И, второй вход которого соединен с первым выходом дешифратора, группа выходов которого соединена с вторыми входами элементов И группы, старший разряд группы выходов дешифратора соединен с единичным входом третьего триггера и с нулевым входом четвертого триггера, единичный вход которого соединен с выходом четвертого элемента И, второй вход которого соединен с вторым входом второго элемента ИЛИ, нулевым входом третьего триггера и вторым выходом дешифратора, группе информационных входов которого соединена с группой выходов первого счетчика, выходы элементов И группы соединены с группой информационных входов регистра, отличающееся тем, что, с целью увеличения быстродействия, в него введены два счетчика, два буферных регистра, мультиплексор, блок управления, причем выход мультиплексора является информационным выходом устройства для подключения к информационному входу ЭВМ, первый выход блока управления является выходом прерывания устройства для подключения к входу прерывания ЭВМ, первый вход запуска блока управления является входом чтения устройства для подключения к выходу чтения ЭВМ, при этом выходы регистра, третьего и четвертого триггеров соединены с информационными входами первого и второго буферных регистров, выходы которых соединены с первым и вторым информационными входами мультиплексора соответственно, первый и второй управляющие входы которого соединены с выходами второго и третьего счетчиков и с первым и вторым входами разрешения чтения блока управления соответственно, второй и третий выходы которого соединены со счетными входами второго и третьего счетчиков и синхровходами первого и второго буферных регистров соответственно, причем блок уп1385129 равления содержит триггер, элемент задержки, три элемента ИЛИ, два элемента НЕ, шесть элементов И, первый вход первого элемента И соединен с первым входом второго элемента И и являетс первым входом запуска блока управлень„. вход элемента задержки является вторь м входом запуска блока управления, выход первого элемента ИЛИ соединен со счетным входом триггера и является первым выходом блока управления, выходы второго и третьего элементов ИЛИ являются вторым и третьим выходами блока управления соответственно, второй вход первого элемента И соединен с входом первого элемента НЕ, с первым входом первого элемента ИЛИ и является первым входом разрешения чтения блока управления, второй вход второго элемента И соединен с входом второго

Изобретение относится к вычислительной технике и предназначено для организации ввода в электронно-вычислительную машину (ЭВМ) информации, поступающей из канала связи.

Целью изобретения является увеличениебыстродействия.

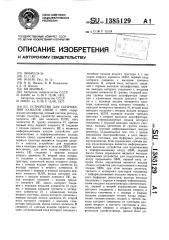

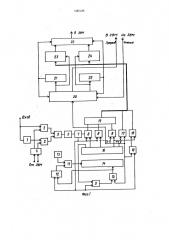

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — схема блока управления.

Устройство содержит (фиг. 1) первый элемент НЕ 1, второй элемент И 2, первый элемент И 3, первый триггер 4, первый элемент ИЛИ 5, второй элемент НЕ 6, третий элемент HE 7, группу элементов

И 8, третий элемент И 9, четвертый элемент И 10, пятый элемент И 11, второй триггер 12, генератор 13 импульсов, первый счетчик 14, второй элемент ИЛИ 15, дешифратор 16, третий триггер 17, четвертый триггер 18, регистр 19, блок 20 управления, второй счетчик 21, третий счетчик 22, первый буферный регистр 23, второй буферный регистр 24, мультиплексор 25.

Блок 20 управления содержит элемент 26 задержки, первый элемент ИЛИ 27, триггер

28, первый элемент HE 29, пятый элемент И 30, шестой элемент И 31, второй элемент НЕ 32, третий элемент И 33, первый элемент И 34, четвертый элемент И 35 второй элемент И 36, второй элемент ИЛИ

37, третий элемент ИЛИ 38.

Устройство работает следующим образом.

При рабочем состоянии канала триггер 4 находится в состоянии «О». Поступающий на вход устройства маркер начала (низкий уровень), проходя через элементы НЕ 1, И 2, 5

30 элемента НЕ, с вторым входом первого элемента ИЛИ и является вторым входом разрешения чтения блока управления, при этом в блоке управления выходы первого и второго элементов И соединены с первыми входами второго и третьего элементов ИЛИ соответственно, вторые входы которых соединены с выходами третьего и четвертого элементов И соответственно, первые входы которых соединены с выходами пятого и шестого элементов И соот-ветственно, первые входы которых соединены с выходами первого и второго элементов HE соответственно, вторые входы пятого и шестого элементов И соединены с единичным и нулевым выходами триггера соответственно, выход элемента задержки соединен с вторыми входами третьего и четвертого элементов И.

ИЛИ 5, НЕ 6, устанавливает через элемент HE 7- триггер 12 в состояние «1».

Единичное состояние триггера 12 дает разрешающий уровень на элемент И 11, разрешая прохождение сигналов от генератора

13 импульсов на счетчик 14. После того, как на вход счетчика поступает определенное число импульсов, появляется сигнал на первом выходе дешифратора 16, который с помощью элемента И 9 проверяет наличие маркера начала на входе устройства. Если к этому моменту маркер начала отсутствует, то приходящий на вход устройства сигнал расценивается как помеха и устройство переводится в исходное состояние сигналом с выхода элемента ИЛИ 15. Если же маркер начала подтверждается, то сигналы с генератора 13 импульсов продолжают поступать в счетчик 14. Через определенные интервалы времени на группе выходов дешифратора 16 появляются сигналы, которые через элементы И 8 осуществляют запись информационных битов в соответствующие ячейки регистра 19. Одновременно сигнал со старшего разряда группы выходов дешифратора 16 устанавливает в состояние «1» триггер 17, что свидетельствует о наборе в регистре 19 полного слова. Одновременно он устанавливает в исходное состояние в «О» триггер 18, который мог быть установлен в состояние «1» в предыдущем цикле формирования слова, Сигнал с второго выхода дешифратора 16 проверяет наличие маркера конца. При его отсутствии триггер 18 через элемент И 10 устанавливается в состояние «1», а задним фронтом этого сиг13851

3 нала через элемент ИЛИ 15 устанавливает- ся счетчик 14 в исходное состояние. Сигнал с второго выхода дешифратора 16 поступает также на второй вход запуска блока 20 управления и на элемент 26 задержки, осуществляя запись слова, сформированного в регистре 19 и триггерах 17 и .18, в один из буферных регистров 23 или 24, представляющих собою циклические регистры на восемь слов каждый.

Назначение блока 20 управления заклю- Io чается в управлении с помощы6 счетчиков

2l и 22 процессами записи-чтения из двух буферных регистров 23 и 24, каждый из которых работает либо в режиме записи слов с регистра 19, либо в режиме чтения ЭВМ накопленных слов.

Процессы записи-чтения после начальной установки устройства осуществляются следующим образом.

Сформированное на регистре 19 и триггерах 17 и 18 слово поступает на входы регистров 23 и 24. Сигнал со второго выхода дешифратора 16 (фиг. 2) поступает на второй вход запуска блока 20 управления и далее через элемент 26 задержки на вторые входы элементов И ЗЗ и 35.

Первые входы этих элементов являются выходами элементов И 30 и 31 соответственно. На первые входы этих элементов через элементы НЕ 29 и 32 соответственно поступают потенциалы с выходов четырехразрядных счетчиков 21 и 22, а вторые входы являются выходами 1 и 0 триггера 28. В исходном положении на первом и втором входах элемента И 30 присутствуют положительные потенциалы, и сигналы с второго выхода дешифратора 16 через элемент И ЗЗ поступают на вход счетчика 21 и на вход буферного регистра 23, осуществляя тем самым запись и продвижение информационных слов в регистре.

После записи восьми слов сигнал с выхода четырехразрядного счетчика 21 поступает на

29

4 вход элемента ИЛИ 27 и да.чее в канал

ЭВМ, выставляя тем самым требовани» прерывания. Одновременно этот сигнал, пос тупая на счетный вход триггера 28, производит его переключение, при этом открывается элемент И 35 и сигнал с второго выхода дешифратора 16 через элементы

И 35 и ИЛИ 38 поступает на вход счетчика 22 и на синхровход второго буферного регистра 24, осуществляя тем самым запись информации в этот регистр.

ЭВМ, обработав прерывание, производит считывание информации из первого буферного регистра 23 путем формирования сигнала «Чтение», который поступает на элемент И 34 и далее через элемент ИЛИ

37 — на вход счетчика 21 и на синхровход первого буферного регистра 23, осуществляя тем самым выдачу информационных слов с его выхода на информационный вход мультиплексора 25 с одновременным продвижением информации внутри этого регистра. Разрешающий потенциал с выхода счетчика 21 поступает на первый управляющий вход мультиплексора 25, разрешая тем самым выдачу информации из регистра 23 в канал ЭВМ. После поступления восьми слов «Чтение» из ЭВМ счетчик 21 возвращается в исходное состояние, закрывая тем самым первый управляющий вход мультиплексора 25.

Объем буферного регистра выбирается таким образом, что считывание информации из него происходит значительно быстрее нежели запись в него.

После записи восьми слов во второй буферный регистр 24 сигнал с выхода счетчика 22 производит переключение триггера 28, формирование сигнала требования прерывания с ЭВМ, осуществляя тем самым переключение записи слов в первый буферный регистр 23 с одновременным чтением из второго буферного регистра 24 и т. д!

385129

1385I29

На сч22 Сасч22

Со сч.21 Ни сч.21

С (/!/ г)8ыхода дешисрратора 10

В ЯВИ

Фиг. 2

Составнтель С. Пест мал

Редактор Л. Повхан Техред И. Верес Корректор Л. Повхан

Заказ 122/46 Тираж 704 Подписное

ВНИИПИ Государственного комнтета СССР по делам изобретений и открытий

1 l 3035, Москва, Ж вЂ” 35, Рву шская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4