Умножитель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и связи. Цель изобретения - повьгаение быстродействия.Устр-во содержит ЦАП 1, управляемый г-р 5,делитель 13 частоты,счетчики 14 и 15. Введены сумматоры (С) 2-4, регистры 6-9 памяти, эл-ть1 10 и 11 задержки, опорный г-р 12, формирователи 16 и 17 импульсов, инвер тор 18. ЦАП 1 пре- ;Образует двоичный код, поступающий с С 2, в напряжение, к-рое подается на управляющий вход г-ра 5, Периоды сигнала г-ра 5 F и входного сигнала 7 у, изменяются с помощью соответственно счетчиков 14 и 15,причем на счетный вход счетчика 14 поступают импульсы с частотой г-ра 12, а на вход счетчика 15 - с частотой В К раз меньше, где К - коэф. деления делителя 13. Результаты измерения (РИ) периодов F sx переписываются соответственно в регистры 6 и 7 по импульсам с выходов Ф 17 и 16. Эл-ты 10 и 11 осуществляют задержку импульсов с Ф 16 и 17 на время, необходимое для записи в регистр 6 и 7. После записи РИ F ,,,, оЫл в регистр 6 осуществляется установка в ноль счетчика 14 и процесс измерения повторяется в Установка ноль счетчика 15 осуществляется после записи РИ F ex в регистр 7 и возобновляется процесс измерения. РИ Fg в виде двоичного кода поступает на 1-е входы С 2 и 3, а результат измерения Fg, инвертируется в инверторе 18 и поступает на С 3. Код разности РИ F вх и F , с С 3 подается на вход С 4, к-рый с помощью регистров 8 и 9 осуществляет накопление кода разности после каждой корректировки , вызванной изменением частот Fj и/или F g,. На выходе .Q 2 образуется скорректированный код входной частоты. Козф, умножения определяется значением коэф. деления делителя 13. Частота циклов корректировки соответствует F что обеспечивает высокое быстродействие . 1 ил. iS (Л оо СХ5 ел to 1С 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (б1) 4 Н 03 В 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

K А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4091290/24-09 (22) 07.07.86 (46) 30.03.88, Бюл. 9 12 (72) И.С.Калинин, А.В.Лапиров, M.Â.ØHK и А.И.Андреев (53) 621.374.4(088;8) (56) Авторское свидетельство СССР

У 1095345, кл. H 03 В 19/00,03.06.82, Авторское свидетельство СССР

У 552665, кл. H 03 В 19/00,23.07.75, (54) УМНОЖИТЕЛЪ ЧАСТОТЫ (57) Изобретение относится к радиотехнике и связи. Цель изобретения— повышение быстродействия,Устр-во содержит ЦАП 1, управляемый г-р 5,делитель 13 частоты, счетчики 14 и 15.

Введены сумматоры (С) 2-4, регистры

6-9 памяти, эл-ты 10 и 11 задержки, опорный г-р 12, формирователи 16 и

17 импульсов, инвертор 18. ЦАП 1 пре образует двоичный код, поступающий с С 2, в напряжение, к-рое подается на управляющий вход г-ра 5. Периоды сигнала r-ра 5 Г „„ и входного сигнала F „ изменяются с помощью соответственно счетчиков 14 и 15,причем на счетный вход счетчика 14 поступают импульсы с частотой г-ра 12, а на вход счетчика 15 — с частотой в К раз меньше, где К вЂ” коэф. деления делителя 13. Результаты измерения (РИ) периодов F g„„v F ax переписываются соответственно в регистры

6 и 7 по импульсам с выходов Ф 17 и

16. Эл-ты 10 и 11 осуществляют задержку импульсов с Ф 16 и 17 на время, необходимое для записи в регистр б и 7. После записи РИ F ц„ в регистр 6 осуществляется установка в "ноль" счетчика 14 и процесс измерения повторяется, Установка в "ноль" счетчика 15 осуществляется после записи РИ Г „ в регистр 7 и возобновляется процесс измерения.

РИ Г „ в виде двоичного кода поступает йа t-e входы С 2 и 3, а результат измерения Гцц„ инвертируется в инверторе 18 и поступает на С 3. Код разности РИ F qx u F „„ с С 3 подается на вход С 4, к-рый с помощью регистров 8 и 9 осуществляет накопление кода разности после каждой корректировки, вызванной изменением частот Г,„ и/или Г,ц„, На выходе .С 2 образуется скорректированный код вхоцной частоты. Коэф. умножения определяется значением коэф. деления делителя 13. Частота циклов корректировки соответствует F s ix что обеспечивает высокое быстродействие. 1 ил.

1385228

/

35

Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике в уст ройствах преобразования. частоты.

Цель изобретения — повышение быстродействия.

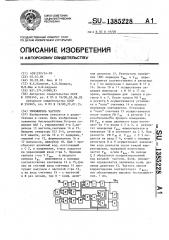

На чертеже представлена структурная электрическая схема умножителя частоты.

Умножитель частоты содержит цифроаналоговой1, преобразователь 1, первый, второй и третий -сумматоры 2

4, управляемый генератор 5, первый, второй, третий и четвертый регистры

6 — 9 памяти, первый и второй элемент 10 и 11 задержки, опорный генератор 12, делитель 13 частоты, первый и второй счетчики 14 и 15, первый и второй формирователи 16 и 17 импульсов и инвертор 18.

Умножитель частоты работает следующим образом.

Цифроаналоговой преобразователь

1 преобразует двоичный код, поступающий с выхода первого сумматора 2, в напряжение, которое подается на управляющий вход управляемого генератора 5. Периоды сигнала управляемого генератора 5 F ых и входного сигнала Р изменяются с помощью вx соответственно первого и второго счет1 чиков 14 и 15, причем на счетный вход первого счетчика 14 поступают импульсы с частотой опорного генератора 12, а на счетный вход второго счетчика 15 поступают импульсы с частотой в К раз меньше, где К вЂ” коэффициент деления делителя 13. Результаты периодов Р ы и Р вх перепивых сываются соответственно в первый и второй регистры 6,7 по импульсам с выходов соответственно второго и первого формирователей 17 и 16.Элементы 10 и 11 осущесувляют задержку импульсов с выходов первого и второго формирователей 16 и 17 на время, необходимое для записи информации в первый и второй регистры 6,7;После записи результатов измерения периода F ы„ в первый регистр 6 осуществляется установка в "ноль" первого счетчика 14 и процесс измерения периода F повторяется. Установка в "ноль" второго счетчика 15 осуществляется после записи результатов измерения периода Р „ во второй регистр 7 и возобновляется процесс измерения периода Р „, Результат измерения периода F „ в виде двоичного кода поступает на первые входы первого и второго сумматоров 2,3, а результат измерения периода F вы„ инвертируется на ннверторе 18 и поступает на второй вход второго сумматора 3. Код разности результатов измерения Р „ и Рвых с выхода второго сумматора 3 подается на первый вход третьего сумматора 4, который с помощью третьего и четвертого регистров 8,9 осуществляет накопление кода разности после каждой корректировки, вызванной изменением частот

Fax H H Fв„,х . Полученный результат поступает с выхода третьего регистра 8 на второй вход первого сумматора 2. Таким образом на выходе первого сумматора 2 образуется скорректированный код входной частоты.

Коэффициент умножения определяется значением коэффициента деления делителя 13.Частота циклов корректировки соответствует F Ä,„, что обеспечивает высокое быстродействие. Цифровое управление, основанное на принципе статического сравнения параллельных кодов частот, защищает умножитель частоты от перерегулировок при рез- . ких изменениях частоты входного сиг» нала.

Формула изобретения !

Умножитель частоты, содержащий последовательно соединенные цифроаналоговый преобразователь и управляемый генератор, делитель частоты и первый счетчик, о т л и ч а ю щ и йс я. тем,что,с целью повышения быстродействия,введены второй счетчик, первый, второй, третий и четвертый регистры памяти, первый, второй и третий сумматоры, первый и второй элементы задержки, первый и второй фор мирователи импульсов, инвертор и опорный генератор, выход которого соединен с входом делителя частоты и счетным выходом первого счетчика, выход делителя частоты соединен со счетным входом второго счетчика,установочный вход которого соединен с выходом первого элемента, выходы первого и второго счетчиков соединены с информационными входами соответственно первого и второго регистров памяти, первые входы первого и второго сумматоров объединены

1385228

Составитель Ю.Максимов

Редактор И.Сегляник Техред N.Õoäàíè÷ Корректор О. Кравцова

Заказ 1419/51 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород,ул.Проектная,4 и соединены с выходом второго регистра памяти, вход записи которого объединен с.входом первого элемента задержки и соединен с выходом пер5 ного формирователя импульсов, второй вход второго сумматора соединен с выходом инвертора,вход инвертора соединен с выходом первого регистра памяти, вход записи которого объединен с входом записи третьего регистра памяти, с входом второго элемента задержки и соединен с выходом второго формирователя импульсов, выход второго сумматора соединен с 15 первым входом третьего сумматора, выход которого соединен с информационным входом третьего регистра памяти, выход третьего регистра памяти ! соединен с вторым входом первого сумматора и с информационным входом четвертого регистра памяти, выход которого соединен с вторым входом третьего сумматора, вход записи четвертого регистра памяти объединен с установочным входом первого счетчика и соединен с выходом второго элемента задержки, выход первого сумматора соединен с входом цифроаналогового преобразователя, выход управляемого генератора соединен с входом второго формирователя импуль-сов.