Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и обеспечивает повьшение коэф.подавления синфазного входного тока. Дифференциальйый усилитель содержит семь транзисторов Т I-7, три источника тока (ИТ) 8-10. Равные токи ИТ 8,9 усиливаются Т 1,2,. проходят через Т 7 и отпирают Т 5, 6, при этом суммарный ток Т 1,2 равен току ИТ 10. Разность токов, поступающих на входы дифференциального усилителя, равна разности токов Т 3, 4 и равна разности базовых токов Т 1,2. Т. обр., разность входных токов усиливается дифференциальным каскадом на Т 1,2. Дифференциальный усилитель имеет небольшое входное сопротивление и потенциальное смещение входов, что позволяет использовать его в качестве усилителя тока. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

llO ДЕЛАМ ИЗОБРЕТЕНИЙ.И ОТНРЫТИЙ (21) 4090937/24-09 (22) 18.07.86 (46) 30.03.88. Бюл. У 12 (72) В.Н.Иванов, В.В.Иванов и В.А.Стрик (53) 621.375.026 (088.8) (56) Патент Франции NI 2275067, кл. Н 03 Р 3/347, опублик.13.2.76, фиг.5. (54) ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ (57) Изобретение относится к радио-. технике и обеспечивает повышение коэф.подавления синфазного входного тока. Дифференциальйый усилитель содержит семь транзисторов Т 1-7, .

„.,зи„„днища я1 (50 4 Н 03 F 3/45 три источника тока (ИТ) 8-10. Равные токи ИТ 8,9 усиливаются Т 1,2,. проходят через Т 7 и отпирают Т 5, 6, при этом суммарный ток Т 1,2 равен току ИТ 10. Разность токов, пос тупающих на входы дифференциального усилителя, равна разности токов Т 3, 4 и равна разности базовых токов

Т 1,2. Т. обр., разность входных токов усиливается дифференциальным каскадом на Т 1,2. Дифференциальный усилитель имеет небольшое входное сопротивление и потенциальное смещение входов, что позволяет использовать его в качестве усилителя тока. 1 ил.

1385256

Изобретение относится к радиотех- нике и может быть использовано в интегральных полупроводниковых устройствах. 5

Цель изобретения — повышение коэффициента подавления синфазного входного тока.

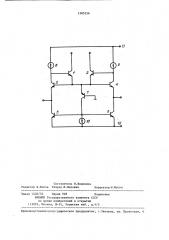

На чертеже изображена принципиальная электрическая схема диффеРенци- 10 ального усилителя.

Дифференциальный усилитель содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5, шестой 6 и седьмой 7 транзисторы, первый 8, вто- 15 рой 9 и третий 10 источники тока,первую 11 и вторую 12 шины источника питания.

Дифференциальный усилитель работает следующим образом. 20

Равные токи источников 8 и 9 тока усиливаются транзисторами 1 и 2, проходят через транзистор 7 и отпирают транзисторы 5 и 6 так, что токи транзисторов 3 и 4 становятся рав- 25 ными токам источников 8 и 9 тока.

- При этом суммарный ток транзисторов

1 и 2 равен току источника 10 тока.

Разность токов, протекающих через входы дифференциального усилителя, 30 равйа разности токов транзисторов 3 и .4 и равна разности базовых токов транзисторов 1 и 2. Таким образом, разность входных токов усиливается в P раэ дифференциальным каскадом на транзисторах 1 и 2. Потенциальное смещение на входах относительно средней точки источникд питания равно разности напряжений эмиттер-база транзисторов 3 и 4 и транзистора 7, 40 т.е. не превьпаает нескольких милливольт

Синфазное входное сопротивление усилителя равно: 45

R вх.с р 6/P в,в > где ц — температурный потенциал р-и-перехода;

I - ток источников 8 и 9 тока;

f5 — усиление транзисторов по току.

Дифференциальное входное. сопротивление равно вкя 2 т вq

Таким образом, предлагаемый дифференциальный усилитель имеет небольшое входное сопротивление и потенциальное смещение входов, что позволяет использовать его в качестве усилителя тока.

Формула изобретения

Дифференциальный усилитель, содержащий первый и второй транзисторы, коллекторы которых являются выходом дифференциального усилителя, базы через соответствующие первый и второй источники тока соединены с первой шиной источника питания, эмиттеры — с базами соответственно третьего и четвертого транзисторов, коллекторы которых соединены с базами соответственно первого и второго транзисторов, а эмиттеры являются соответственно первым и вторым входами дифференциального усилителя и соединены с коллекторами соответственно пятого и шестого транзисторов, базы которых объединены, эмиттеры объединены и подключены к второй шине источника питания, о т л и ч а ю щ и й-, с я .тем, что, с целью повышения коэффициента подавления сннфазного входного тока, введены третий источник тока и седьмой транзистор, имеющий структуру, противоположную структуре транзисторов дифференциального усилителя, коллектор которого подключен к базам пятого и шестого транзисторов, соединенным через третий генератор тока с второй шиной источника питания, при этом эмиттеры первого и второго транзисторов объединены и подключены к эмиттеру седьмого транзистора, база которого подключена к общей. шине.

1385256

Составитель И.Водяхина

Редактор Е.Копча Техред И.Попович

Корректор.И.Муска

Заказ 1420/52 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и.открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.ужгород, ул. Проектная, 4