Регенератор для цифровых сигналов с квантованной обратной связью

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - повышение помехоустойчивости. Устр-во содержит корректирующий усилитель 1, сумматоры (С) 2 и 5, инверторы 3 и 9, линии 4 и 10 задержки, решающий блок (РБ) 7. Введены С 8 и 11, управляемые ключи 6 и 13, РБ 12, блоки 14 компенсации искажений. Каждый блок 14 состоит из С 15 и.18, инвертора 16, линии 17 задержки, управляемых ключей 19 и 20 и РБ 21. Информацо импульсы (ИИ) с межсимвольными искажениями, частично скорректированные усилителем 1, поступают на 1-й вход С 2 и вход инвертора 3, далее на линию 4, где задерживаются на тактовый интервал , и на 2-й вход С 5о В С5 искаженные ИИ в противофазе суммируются с эталонными импульсами с блока 7, Б результате появляется, разностный сигнал , уровень к-рого будет соответствовать уровню, на к-рый снижается следующий заданным импульсом, импульс вследствие наличия межсимвольной помехи. Далее сигнал коррекции с С 5 через ключ 6 подается на 2-й вход С 2, где суммируется с искаженным сигналом и, ТоОбро, откорректированный сигнал подается на блок 7. Для увеличения вероятности, правильной регистрации единиц порог решения блока 7 приподнят вьш1е своего оптим. значения Пороги решения РБ 21 последующих блоков 14 постепенно снижаются , оставаясь при этом вьше оптим . 1 ЗоП, ф-лы, 1 ил о € (Л СО 00 СГ1 IsD СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU„„1385275 А 1 (58 4 Н 03 К 5/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ. И ОТНРЫТИЙ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (ИИ) с межсимвольными искажениями, частично скорректированные усилителем 1, поступают на 1-й вход С 2 и вход инвертора 3, далее на линию 4, где задерживаются на тактовый интервал, и на 2-й вход С 5. В С5 искаженные ИИ в противофазе суммируются с эталонными импульсами с блока 7. В результате появляется разностный сигнал, уровень к-рого будет соответствовать уровню, на к-рый снижается следующий заданным импульсом, импульс вследствие наличия межсимвольной помехи, Далее сигнал коррекции с С 5 через ключ 6 подается на 2-й вход С 2, где суммируется с искаженным сигналом и, т.обр., откорректированный сигнал подается на блок 7.

Для увеличения вероятности, правильной регистрации единиц порог решения блока 7 приподнят вьш е своего оптим. значения. Пороги решения РБ 21 последующих блоков 14 постепенно снижаются, оставаясь при этом выше оптим. 1 з.п. ф-лы, 1 ил. (21) 4170575/ 24-09 (22) 14.11.86 (46) 30.03.88 ° Бюл. ¹ 12 (71) Одесский электротехнический институт связи им. А.С. Попова (72) И.Е. Байдан, Е,А. Еркин и Д,А. Сирбиладзе (53) 621.394,6(088.8) (56) Патент ФРГ № 3132972, кл. Н 03 К 5/00, 1983. (54) РЕГЕНЕРАТОР ДЛЯ ЦИФРОВЫХ СИГ- .

НАЛОВ С КВАНТОВАННОЙ ОБРАТНОЙ СВЯЗЬЮ (57) Изобретение относится к электросвязи, Цель изобретения — повышение помехоустойчивости, Устр-во содержит корректирующий усилитель 1, сумматоры (С) 2 и 5, инверторы 3 и 9, линии

4 и 10 задержки, решающий блок (РБ) 7.

Введены С 8 и 11, управляемые ключи 6 и 13, РБ 12, блоки 14 компенсации искажений. Каждый блок 14 состоит из С 15 и 18, инвертора 16, ли- нии 17 задержки, управляемых ключей

19 .и 20 и РБ 21. Информац. импульсы

ОПИСАНИЕ ИЗОБРЕТЕНИЯ(, 1385275

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи.

Цель изобретения — повышение поме- 5 хоустойчивости.

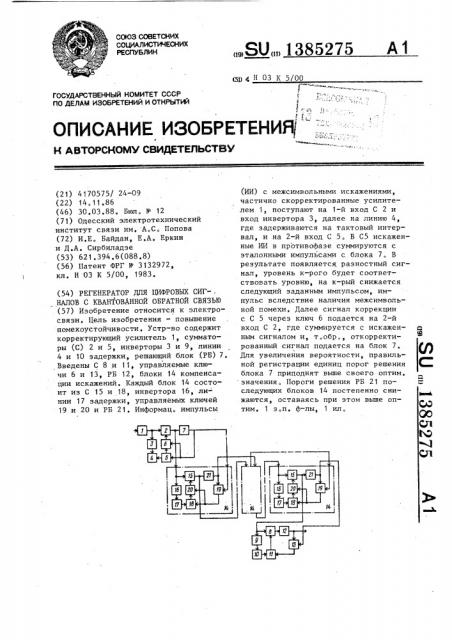

На. чертеже изображена структурная электрическая схема предложенного регенератора.

Регенератор для цифровых сигналов 10

I с квантованной обратной связью со- . держит первый корректирующий усилитель 1, первый сумматор 2, первый инвертор 3, первую линию 4 задержки, второй сумматор 5, первый управляе- 15 мый ключ 6, первый решающий блок 7, третий сумматор 8, второй инвертор 9, вторую линию 10 задержки, четвертый сумматор 11, второй решающий блок.

12, второй управляемый ключ 13 и бло- 20 ки 14 компенсации искажений.

Каждый блок компенсации искажений состоит иэ первого сумматора 15, инвертора 16, линии 17 задержки, второго сумматора 18, первого 19 и второ- 25 го.20 управляемых ключей и решающего блока 21.

Регенератор работает следуюпим образом.

Информационные импульсы в виде 30 единиц и нулей с межсимвольными искажениями, частично скорректированные корректирующим усилителем 1, поступают на первый вход сумматора 2 и вход ННВррТорВ 3, с выхода KQTopoI o 35 далее поступают на линию 4 задержки, где задерживаются на тактовый интервал и далее подаются на второй вход сумматора 5, на первый вход которого поступают информационные импульсы 40 после того, как они были зарегистрированы и пронормированы по высоте и длительности решающим блоком 7. B сумматоре 5 искаженные информационные импульсы в противофазе суммиру45 ются с эталонными импульсами с выхода решающего блока 7, В результате на выходе сумматоре 5 появляется разностный сигнал, уровень которого соответствует уровню, на который снижается последующий данному импульсу

50 импульс вследствие наличия межсим-. вольной помехи. Далее сигнал коррекции с выхода сумматора 5 через управляемый ключ 6 подается на второй вход сумматора 2, где суммируется

55 с искаженным сигналом и, таким образом, откорректированный сигнал подается на вход вешающего блока 7.

Правильность работы рассмотренной части регенератора во многом определяется правильностью работы решающего блока 7, в частности, вероятностью безошибочной регистрации как единиц, так и нулей.

Для увеличения вероятности правильной регистрации единиц порог решения решающего блока 7 приподнят вьппе своего оптимального значения.

Однако при этом уменьшается количество регистрируемых единиц, так как. уже меньшее их число достигается уровня приподнятого порога.

Управляемый ключ 6 замыкается импульсами, действующими на его первый управляющий вход с выхода решающего блока 7. Таким образом, он пропускает на сумматор 2 корректирующий сигнал только при регистрации единиц, достигающих уровня приподнятого поро-

ra, и предотвращает прохождение мешающего разностного сигнала, который формируется на выходе сумматора 2 в результате суммирования в противофазе недостающих уровня приподнятого порога единиц с нулевым уровнем с выхода решающего блока 7. Таким образом, в рассмотренной части регенератора происходит частичная, но более достоверная компенсация влияния последействия верных единиц на соседний тактовый интервал. Далее частично скорректированный сигнал с выхода сумматора 2 поступает на информационный вход первого блока 14 компенсации искажений и попадает на первый вход первого сумматора 15 и на вход инвертора 16. С выхода последнего сигнал задерживается на тактовый интервал линией 17 задержки и поступает на второй вход второго сумматора

18, на первый вход которого подаются нормированные импульсы с выхода решающего блока 21 через управляемый ключ 19. С выхода сумматора 18 разностный сигнал коррекции через управляемый ключ 20 подается на второй вход сумматора 15, с, выхода которого откорректированный сигнал поступает на;вход решающего блока 21, порог решения которого снижен по сравнению с порогом решения решающего блока 7, оставаясь однако вьппе оптимального.

При этом решающим блоком 21 будет с большой достоверностью зарегистрировано большее, чем. в решающем блоке

7, количество импульсов, однако кор1385275 ректироваться будут последствия только т ех импульсов, которые зарегистрировались решающим блоком 21 первого блока 14 компенсации искажений, но не были регистрированы решающим блоком 7. Для этого прямоугольные импульсы с выхода решающего блока 7 подаются на первый управляющий вход первого блока 14 компенсации искажений, размыкают управляемый ключ 19 и тем самым предотвращают повторную коррекцию уже откорректированных импульсов. С первого выхода первого блока 14 компенсации искажений уже большей степени откорректированный сигнал подается на информационный вход второго блока 14 компенсации ис. кажений,, на управляющий вход которого импульсы запрета поступают с второго выхода первого блока 14 компенсаций искажений. Так, постепенно поблочно с увеличением количества. блоков все большей степени компенсируется межсимвольная помеха, причем пороги решения решающих блоков последующих блоков компенсации искажений постепенно снижаются, оставаясь при этом выше оптимального.

С первого выхода последнего блока

14 компенсацИи искажений откорректированный сигнал подается на первый вход третьего сумматора 8 и вход второго инвертора 9. С выхода сумматора 8 далее импульсы попадают на вход второго решающего блока 12 pere«35 нератора, где они регистрируются уже на уровне оптимального hopora (равного половине высоты неискаженного импульса). С выхода решающего блока .

12 пронормированные импульсы передаются в линию и через управляемый ключ 13 на первый вход четвертого сумматора 11, на второй вход которого действует сигнал с выхода инвертора 9, задержанный линией 10 задержки на тактовый интервал. С выхода сумматора 11 сигнал коррекции подается непосредственно на второй вход сумматора 8, где и происходит окончательная его коррекция. Управляемый ключ 13 пропускает только те импульсы, которые регистрируются решающим блоком 12 и не были зарегистрированы предыдущими блоками решения.

Таким образом, применением каскадно включенных компенсационных блоков с приподнятыми порогами решения достигается постепенное очищение искаженных входных импульсов от межсимвольной помехи.

Формула и з обретения

1. Регенератор для цифровых сигналов с квантованной обратной связью, содержащий корректирующий усилитель, выход которого соединен с входом первого инвертора и с первым входом первого сумматора, выход которого подключен к входу первого решающего блока, выход которого соединен с первым входом второго сумматора, второй вход которого подключен к выходу первой линии задержки, вход которой подключен к выходу первого инвертора, отличающийся тем, что, с целью повышения помехоустойчивости, введены третий и четвертый сумматоры, второй решающий блок, два управляемых ключа и блоки компенсации искажений, при этом первый вход .первого управляемого ключа соединен с первым входом второго сумматора, выход которого подключен к второму входу первого управляемого ключа, выход которого соединен с вторым входом первого сумматора, выход которого соединен с первым входом первого блока компенсации искажений, второй вход которого соединен с выходом первого решающего блока, первый и второй выходи первого блока компенсации искажений через каскадно соединенные последующие блоки компенсации искажений подключены соответственно к первому и второму входам последнего блока компенсации искажений, первый выход которого подключен к входу второго инвертора и . входу третьего сумматора, выход которого соединен с входом второго решающего блока, выход которого соединен с первым входом второго управляемого ключа, выход которого подключен к первому входу четвертого сумматора, второй вход которого подключен к выходу второй линии задержки, вход которой подключен к выходу второго инвертора, выход четвертого сумматора соединен с вторым входом третьего сумматора, а второй выход последнего блока компенсации искажений подключен к второму входу второго управляемого ключа.

1385275

Составитель О,Геллер

Техред М.Ходанич Корректор M.Ìàêñèìèøèíåö

Редактор Е.Копча

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 1421/53

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

2. Регенератор по п. 1, о т л ич а ю шийся тем, что каждый блок компенсации искажений содержит два управляемык ключа, два сумматора, решающий блок, линию задержки и инвертор, вход которого подключен к первому входу первого сумматора, выход которого через решающий блок подключен к первому входу первого управляемого ключа, выход которого соединен с первым входом второго управляемого ключа и с первым входом второго сумматора, выход которого соединен с вторым входом второго управляемого ключа, выход которого подключен к. второму входу первого сумматора, выход инвертора через линию задержки подключен к второму входу второго сумматора, при этом первый вход первого сумматора и второй вход первого управляемого ключа являются соответственно первым и вторым входами блока компенсации искажений, первым и вторым выходами которого являютея соответственно выход первого сумматора и выход решающего блока.