Магистральный формирователь импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к электронно-вычислительной технике и может быть использовано в качестве выходного буферного устройства в больших интегральных схемах при работе выхода йа общую шину, нагрузкой для которой являются, например, МДП-схемы. Изобретение повышает надежность устройства в режиме динамического .функционирования, а также при наличии неисправности выходной шины. Это обеспечивается путем перевода выходных транзисторов магистрального элемента в момент прихода входного импульса в закрытое состояние на время, равное времени задержки установления этого состояния, и введения блокировки переключения магистрального элемента при константной неисправности выходной шины с задержкой, равной времени срабатывания магистрального элемента. Устройство содержит магистральный элемент 1, элементы 2 и 3 .задержки, элементы 4 и 5 сравнения, элементы ИЛИ-НЕ 6 и 7, входную 8 и выходную 9 шины. Каждый из элементов 2 и 3 задержки выполнен в виде цепочки , последовательно соединенных инверторов 10. На чертеже также показаны дополнительный выход 11 элемента 2, клеммы 12 и 13 магистрального элемента 1, который выполнен на МДП- транзисторах 14 и 15 одного типа проводимости , выход 16 элемента 1, шина питания 17, общая шина 18. 2 з.п. ф-лы, 1 ил. i сл

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИК (19) SU(ii) А1 (5D 4 Н 03 К 5 01 19/003 (ОПИСАНИЕ ИЗОБРЕТЕНИЯ:

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ,1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4075926/24-21 (22) 13,05.86 (46) 30.03.88. Бюл. N - 12 (71) Институт проблем управления (автоматики и телемеханики) (72) И.А. Газарян (53) 621.374(088i8) (56) Европейский патент Р 102670, кл. Н 03 К 19/094, 1983.

Патент Великобритании кл. Н 03 К 19/003, 1982. (54) МАГИСТРАЛЬНЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ (57) Изобретение относится к электронно-вычислительной технике и мо-. жет быть использовано в качестве выходного буферного устройства в больших интегральных схемах при работе выхода на общую шину, нагрузкой для которой являются, например, МДП-схемы. Изобретение повышает надежность устройства в режиме динамического функционировавия, а также при наличии неисправности выходной шины. Это обеспечивается путем перевода выходных транзисторов магистрального элемента в момент прихода входного импульса в закрытое состояние на время, равное времени задержки установления этого состояния, и введения блокировки переключения магистрального элемента при константной неисправности выходной шины с задержкой, равной времени срабатывания магистрального элемента. Устройство содержит магистральный элемент 1, элементы 2 и 3 задержки, элементы 4 и 5 сравнения, элементы ИЛИ-НЕ 6 и 7, входную 8 и выходную 9 шины. Каждый из элементов

2 и 3 задержки выполнен в виде цепочки последовательно соединенных инверторов 10. На чертеже также показаны дополнительный выход 11 элемента 2, клеммы 12 и 13 магистрального элемента 1, который выполнен на МДПтранзисторах 14 и 15 одного типа проводимости, выход 16 элемента 1, шина питания 17, общая шина 18. 2 s.n. ф-лы, 1 ил, 1385277

Устройство относится к электронно-вычислительной технике и может быть использовано в качестве выходного буферного устройства в больших интегральных схемах при работе вы5 хода на общую шину, нагрузкой для которой являются, например, МДП-схемы. !

Целью изобретения является повышение надежности устройства в режиме динамического функционирования, а также при наличии константной неисправности выходной шины путем перевода выходных транзисторов магистрального элемента в момент прихода входного 15 импульса в закрытое состояние на время, равное времени задержки установления этого состояния, и введения блокировки переключения магистрального элемента при константной не- 20 исправности выходной шины с задержкой, равной времени срабатывания магистрального элемента.

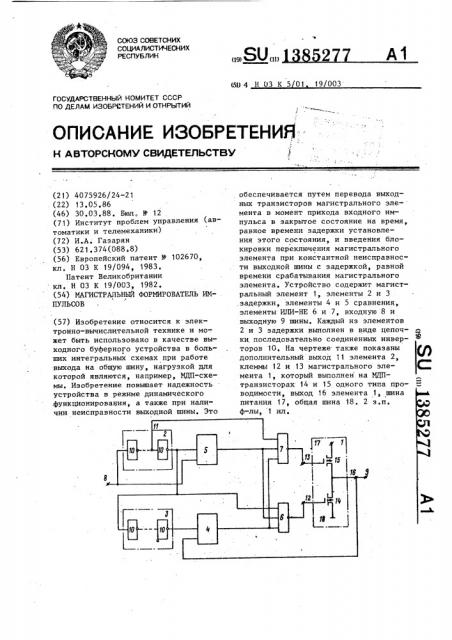

На. чертеже приведена принципиальная схема формирователя импульсов при использовании МПП-транзисторов и-типа в магистральном элементе и устройства сравнения, реализующего функцию неравнозначности (ИСКЛЮЧАЮЩЕЕ ИЛИ).

Устройство содержит магистральный элемент 1, первый 2 и второй 3 элементы задержки, первый 4 и второй 5 элементы сравнения, первый 6 и второй 7 элементы ИЛИ-НЕ, входную 8 и выходную 9 шины, Каждый из элементов, 2 и 3 задержки выполнен в виде цепочки последовательно соединенных инверторов 10, первый из которых являь ется входом, а последний — выходом элемента задержки, Первый вход первого элемента 4 сравнения подключен к выходной шине

9 устройства, которая соединена с выходом магистрального элемента 1.

Первый вход второго элемента 5 сравнения соединен с входной шиной

8 устройства и входом первого элемента 2 задержки, а второй вход, — с первым входом первого элемента - 50

ИЛИ-НЕ 6, с входом второго 3 и выходом первого 2 элементов задержки, а выход элемента 5 сравнения — с входами первого 6 и второго 7 элементов MJDI-НЕ. Второй вход первого эле- 55 мента 4 сравнения подключен к выходу второго элемента 3 задержки, а его выход — к третьим входам элементов

ИЛИ-НЕ 6 и 7 ° Третий вход второго элемента ИЛИ-HE 7 подключен к дополнительному выходу 11 первого элемента 2 задержки, который является входом последнего инвертора цепочки инверторов, составляющих элемент 2 задержки.

Выходы первого 6 и второго 7 элементов ИЛИ-НЕ подключены соответственно к входным клеммам 12 и 13 магистрального элемента 1.

Магистральный элемент 1 выполнен в виде последовательно соединенных II-транзисторов 14 и 15 одного типа проводимости, общая точка которых является выходом 16 магистрального элемента. Затворы транзисторов подключены к входным клеммам 12 и 13 магистрального элемента 1, а свободные токовые электроды — соответственно к шине 17 питания и общей шине 18;

Устройство функционирует следующим образом.

В исходном состоянии логические уровни на входной 8 и выходной 9 шинах, а также на выходах первого 2 и второго 3 элементов задержки одинаковые и соответствуют, например, логическому О. Поскольку на входах элементов 4 и 5 сравнения действуют одинаковые уровни, их выходы имеют нулевые значения. На выходе первого элемента ИЛИ-HE 6 действует единичный уровень, и первый МДП-транзистор

14 магистрального элемента 1 открыт, а на выходе второго элемента ИЛИ-НЕ 7 действует при этом нулевой уровень, поскольку на один из входов этого элемента подан единичный уровень с дополнительного выхода 11 элемента 2 задержки.

Когда на входную шину 8 устройства поступает единичный импульс, второе устройство 5 сравнения переключается и на его выходе появляется уровень логической 1, который действует в интервале, равном времени задержки элемента 2 задержки. На вы ходах первого 6 и второго 7 элементов ИЛИ-НЕ устанавливаются нулевые уровни сигналов, МДП-транзисторы 15 и 14 магистрального элемента 1 переходят в закрытое состояние. Магистральный элемент 1 переходит при этом в третье состояние, когда его выход 16 отключен от входной части устройства. Процесс перехода в третье состояние происходит без какого-ли1385277

45 бо потребления мощности в магистраль.ном элементе 1. К концу первого этапа переключения, соответствующего времени задержки элемента 2 задержки, на выходе второго элемента 5 сравнения вновь устанавливается сигнал логического О, а на первом входе первого элемента ИЛИ-НЕ 6 и третьем входе второго элемента ИЛИНЕ 7 устанавливаются новые значения сигналов — соответственно логическая 1 и логический О.

Задержка первого элемента 2 за-держки устанавливается примерно рав- 15 ной времени перезаряда емкости затворов МДП-транзисторов 14 и 15.

Во время второго этапа переключения второй элемент ИЛИ-НЕ 7 переходит в едйничное состояние, второй

МДП-транзистор 15 магистрального элемента 1 открывается и выходная шина 9 устройства от шины источника

17 питания заряжается до уровня логической 1. Первый МДП-транзистор 14 магистрального элемента 1 при этом остается закрытым. Зто исключает сквозное протекание тока между шинами 17 и 18 в переходном процессе °

Задержка второго элемента 3 задержки устанавливается несколько

30 большей, чем время изменения состояния выходной шины 9 при наибольшей нагрузке, В этом случае на выходе первого элемента 4 сравнения действует сигнал логического О до полно- 35

ro завершения процесса переключения выходной шины 9. Если процесс переключения на выходной шине 9 завершится ранее, чем на выходе второго элемента 3 задержки установятся но- 40 вые (единичные) значения уровня, то второй элемент ИЛИ-НЕ 7 временно может изменить свое состояние, переводя второй МДП-транзистор 15 в закрытое состояние. Однако это уже не может повлиять на работу устройства, так как процесс на выходной шине 9 завершен (емкость затворов

МДП-схем, являющихся нагрузкой, заряжена до требуемого уровня).. 5D

В случае, когда на выходной шине

9 устройства действует константная неисправность (в .данном случае за коротка на нулевую шину 18), то по истечении времени, равном задержке 55 второго элемента 3 задержки, на выходе первого элемента 4 сравнения установится сигнал логической 1, который переключит второй элемент

ИЛИ-НЕ 7 в нулевое состояние и тем самым переведет магистральный элемент 1 в третье состояние, когда оба его МДП-транзистора закрыты. При этом устраняется возможность протекания больших токов короткого замыкания через один из транзисторов магистрального элемента 1 в течение длительного промежутка времени, превышающего задержку элемента задержки.

Формула и з обретения

1 . Магистральный формирователь импульсов, содержащий магистральный элемент и первый элемент сравнения, первый вход которого соединен с выходной шиной формирователя импульсов, подключенной к выходу магистрального элемента, о т л и ч а юшийся тем, что, с целью повышения надежности в режиме динамического функционирования, а также при наличии константной неисправности выходной шины, в него дополнительно введены два элемента задержки, выполненные в виде цепочки из четного числа последовательно соединенных инверторов, два элемента ИЛИ-НЕ и второй элемент сравнения, первый вход которого соединен с входной шиной формирователя импульсов и входом первого элемента задержки, второй вход — с первым входом первого элемента ИЛИ-НЕ, с входом второго и выходом первого элементов задержки, а выход †с вторым входом первого и первым входом второго элементов

ИЛИ-НЕ, второй вход первого элемента сравнения подключен к выходу второго элемента задержки, выход первого элемента сравнения подключен к третьему входу первого и второму входу второго элементов ИЛИ-НЕ, третий вход второго элемента ИЛИ-НЕ подключен к дополнительному выходу первого элемента задержки, являющемуся выходом предпоследнего инвертора цепочки инверторов, выходы первого и второго элементов ИЛИ-НЕ подключены соответственно к первой и второй входным клеммам магистрального элемента.

У

2. Формирователь по и. 1, о т л и ч а ю шийся тем, что ма1385277

МДП-транзисторов соединены соответственно с шиной питания и нулевой шиной, Составитель А.Очеретяный

Техред М.Ходанич Корректор Л. Пилипенко

Редактор Е.Копча

Заказ 142.1/53

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 гистральный элемент выполнен в виде последовательно соединенных ИДП-транзисторов одного типа проводимости, общая точка которых является выходом магистрального элемента, затворы.подключены к первой и второй входным клеммам магистрального элемента, а свободные токовые выводы

3. Формирователь по п. 1, о т— л и ч а ю шийся тем, что элемент сравнения выполнен в виде элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.