Анализатор сигнатур

Иллюстрации

Показать всеРеферат

Изобретение относится к технике контроля и диагностики цифровых систем передачи и обработки информации . Цель изобретения - повышение быстродействия путем устранения пауз на время сравнения сигнатур./Устр-во содержит регистры 2 и 3, дешифратор 4, индикатор 5, селектор 6, формир ователь 7 стробов, компаратор (К) 8 сигнатур. Введены следящий К 1 и фиксатор 9 нестабильности. К 1 содержит два сумматора по модулю два, D-триггер. К 8 выполнен в виде пятнадцатиразрядного блока сравнения. Фиксатор 9 содержит эл-т ИЛИ, инвертор,D-триггер, 1К-триггер. На вход селектора 6 поступают сигналы, определяющие длительность и положение во времени интервала измерения, а также выборки принимаемых данных, определяющих сигнал синхронизации. В селекторе 6 производится выбор активного фронта этих сигналов к-рые затем поступают в формирователь 7 стробов, а сигнал тактовой синхронизации - на входы регистра 2, К 1 и фиксатора 9. Сигнал с выхода 1К-триггера управляет соответствуюпщм сегментом индикатора 5, определенным как индикатор нестабильности , горение к-рого указывает.на наличие сбоев во входных данных. 3 3.п. ф-лы, 2 ил. с (О (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

00 А1 (19) (11) (51)4 Н04 В 3 46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ;

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4086102/24-09 (22) 09.07.86 (46) 30.03.88. Вюл. )) 12 (72) А.Л.Ратанов, Д.M.Манкевич и Е.Г.Анцыпович (53) 621.395.664(088.8) (56) Авторское свидетельство СССР

N - 798852, кл . С 06 F 11/30, 1981. (54) АНАЛИЗАТОР СИГНАТУР (57) Изобретение относится к технике контроля и диагностики цифровых систем передачи и обработки информации. Цель изобретения — повышение быстродействия путем устранения пауз на время сравнения сигнатур. (Устр-во содержит регистры 2 и 3, дешифратор

4, индикатор 5, селектор 6, формирователь 7 стробов, компаратор (К) 8 сигнатур. Введены следящий К 1 и фиксатор 9 нестабильности. К 1 содержит два сумматора по модулю два, D-триггер. К 8 выполнен в виде пятнадцатиразрядного блока сравнения ° Фиксатор

9 содержит эл-т ИЛИ, инвертор,D-триггер, IK-триггер. На вход селектора

6 поступают сигналы, определяющие длительность и положение во времени интервала измерения, а также выборки принимаемых данных, определяющих сигнал синхронизации. В селекторе 6 производится выбор активного фронта этих сигналов к-рые затем поступают в формирователь 7 стробов, а сигнал тактовой синхронизации — на входы регистра 2, К 1 и фиксатора 9. Сигнал с выхода ЕК-триггера управляет соответствующим сегментом индикатора 5, определенным как индикатор нестабильности, горение к-рого указывает на наличие сбоев во входных данных.

3 з.п. ф-лы, 2 ил.

1385300

Изобретение относится к технике контроля и диагностики цифровых систем передачи и обработки информа— ции.

Цель изобретения — повышение быстродействия путем устранения пауз на время сравнения сигнатур.

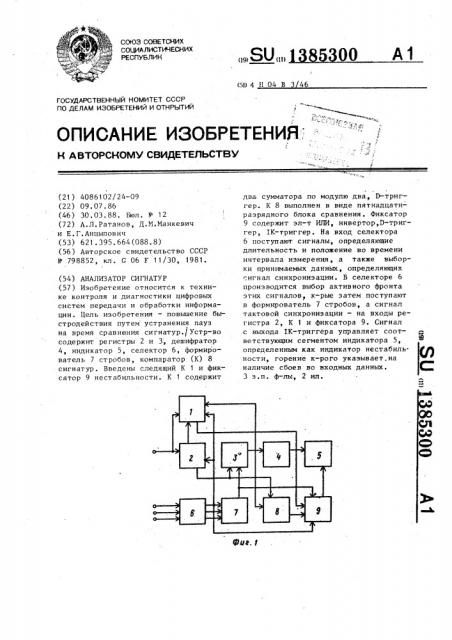

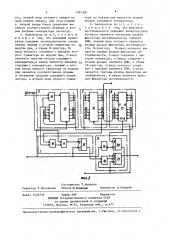

На фиг.1 представлена электрическая структурная схема анализа- 10 тора сигнатур; на фиг.2 — пример конструктивного выполнения первого и второго регистров, компаратора сигнатур, следящего компаратора и фиксатора нестабильности. 15

Анализ атор сигнатур (фиг. 1) содержит следящий компаратор 1, первый 2 и второй 3 регистрь1, дешифратор 4, индикатор 5, селектор 6, формирователь 7 стробов, компаратор 8 20 сигнатур, фиксатор 9 нестабильности.

Следящий компаратор 1 (фиг.2) содержит первый 10 и второй 11 сумматоры по модулю два, D-триггер 12.

Первый регистр 2 (фиг.2) содержит 25 шестнадцатиразрядный регистр 13, первый 14 и второй 15 сумматоры по модулю два.

Второй регистр 3 (фиг.2) выполнен в виде шестнадцатиразрядного регист- 30 ра 16.

Компаратор 8 сигнатур (фиг,2) выполнен в виде пятнадцатиразрядного блока 17 сравнения.

Фиксатор 9 нестабильности (фиг.2) содержит элемент ИЛИ 18, инвертор 19, D-триггер 20, IK-триггер 21, Анализатор сигнатур работает следующим образом.

На вход селектора 6 поступают сиг- 40 налы, определяющие длительность и положение.во времени интервала измерения, а также выборки принимаемых данных,. определяющих сигнал синхронизации. В селекторе 6 производит45 ся выбор активного фронта этих сигналов, которые затем поступают в формирователь 7 стробов, а сигнал тактовой синхронизации на входы первого регистра 2, следящего компаратора 1 и фиксатора 9 нестабильности. В первом регистре 2 сигналы с выходов 7-, 9", 12 и I 6-ro разрядов шестнадцатиразрядного регистра 13 суммируются в первом сумматоре 14, а результат поступает на вход следящего компаратора 1 и сумматора 10, где они суммируются с последовательностью входных данных и поступают на вход шестнадцатиразрядного регистра 13 Структура первого регистра 2 соответствует структуре шестнадцатиразрядного ге— нератора сигнатур с образующим полиномом вида

Ь(х) = х1< + х1 + хЗ + х + 1, в котором происходит деление двоичной входной последовательности на инверсный полином вида

? (х) = 1 + х + х8+ х" +.х с получением шестнадцатиразрядного остатка, который и называется сигна— турой. Математически этот процесс описывается выражением а(х) = h (х) - g(x) + S где Q(x) — частное от деления;

S — сигнатура.

Процесс вычисления заканчивается в конце интервала измерения, когда установившееся состояние разцядов шестнадцатиразрядного регистра 13 записывается во второй регистр 3. Значение вычисленной сигнатуры преобразуется дешифратором 4 в комбинацию управления .четырехразрядным семисегментным индикатором, входящим в состав индикатора 5, на котором 16 дво— ичных разрядов полученной сигнатуры представляются в виде четырех шестнадцатиричных цифр в соответствии с алфавитом — О, 1, 2, 3, 4, 5, 6,7, 8, 9, А, С, F Н, Р, U. Дешифратор 4 представляет собой комбинационный кодопреобразователь двоичного кода в код семисегментного индикатора.

После того, как вновь вычисленная сигнатура перепишется во второй. ре— гистр 3, первый регистр 2 готов к началу вычисления новой сигнатуры.

Последовательностьвходных данных, складываясь с сигналами обратных связей, записывается в первый разряд шестнадцатиразрядного регистра 13 с одновременным сдвигом остальных разрядов. Допустим, что в текущем цикле вычисляется сигнатура последователь— ности данных, стробируемых К такта— ми синхронизации. Пусть с приходом (К-1)-го такта состояние регистра

13 следующее

8 188 15 8 14 8 13 8 1Я 8 1т Sg SqS 8 8 1 В 6 8 5 В 4 3 В 81.

1 385300

Во втором регистре 3 в этот момент хранится сигнатура, вычисленная в предыдущем цикле:

Р16Р15 Р 1Ф 13 12 11 ю g 9 РйР5Р4 РЗ Р1

Если с приходом К-го бита последовательности входных данных вновь полученная сигнатура равна ранее вычисленной, справедливо равенство где j = 1, 2,...,15.

Следовательно, в рассматриваемый момент времени состояния пятнадцати разрядов первого регистра 2S ... S и второго регистра Р ...Р одинаковы, но сдвинуты на шаг относительно друг друга.

Это позволяет организовать предварительное сравнение этих разрядов с опережением на такт синхронизации прихода последнего бита входной последовательности данных.

С учетом задержки комбинационной схемы компаратора 8 сигнатур фиксировать результат предварительного сравнения следует инверсным сигналом синхронизации,, т.е. обратным фронтом записи входных данных.

Эта фиксация обеспечивается в Dтриггере 20 фиксатора 9 нестабильности, на D-вход которого поступает сигнал с выхода пятнадцатиразрядного блока 17, стробируемый по С-входу

D — триггера 20 инверсным тактовым сигналом с выхода селектора 6. Таким образом, на втором входе элемента

ИЛИ 18 присутствует сигнал результата сравнения 15 разрядов текущей и предыдущей сигнатур за полпериода тактового сигнала до окончания вычисления текущей сигнатуры.

Предположим, что на последнем такте текущего цикла вычисления сигнатуры на вход первого регистра 2 поступает последний бит входных данных со значением х. Согласно уравнению обратных связей в первый разряд шест 50 надцатиразрядного регистра 13 запишется бит

Так как для равенства сигнатур необходимо, чтобы S О = p1,,то следовательно

Формируя по этому закону значение ожидаемого бита на последнем такте цикла формирования сигнатуры и сравнения его с пришедшим, можно отслеживать и фиксировать совпадение сигнатур одновременно с их формированием. Окончательно факт несовпадения сигнатур можно фиксировать одновременно с окончанием цикла.

Сигнал с выхода IK-триггера 21. управляет соответствующим сегментом индикатора 5, определенным как индикатор нестабильности, горение которого указывает оператору на наличие сбоев во входных данных.

Формула изобретения

1. Анализатор сигнатур, содержащий последовательно соединенные первый регистр, второй регистр, дешифратор и индикатор, компаратор сигнатур, формирователь стробов и селектор, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами формирователя стробов, первый выход первого регистра соединен с первым входом компаратора сигнатур, второй вход .которого соединен с выходом второго регистра, выход формирователя стробов соединен с вторым входом второго регистра, а первый вход первого регистра соединен с первым выходом Селектора, о т л и ч а юшийся тем, что, с целью повышения быстродействия путем устранения пауз на, время сравнения сигнатур, введены следящий компаратор, первый вход которого объединен с вторым входом первого регистра, а второй, третий и четвертый входы соединены соответственно с вторым выходом первого регистра, первым выходом селектора и .выходом второго регистра, фиксатор нестабильности, первый, второй, третий и четвертый входы которого соединены соответственно с выходами компаратора сигнатур, следящего компаратора, формирователя стробов и с первым выходом селектора, а выход соединен с вторым входом индикатора.

2. Анализатор по п.1, о т л и ч аю .щ и и С я тем, что кампаратор сигнатур выполнен в виде, блока сравнения двух пятнадцатиразрядных двоичных чи1385300

Составитель Э. Ьорисов

Редактор Т. Лазоренко Техред Л. олийнык Корректор О. Кундрик

Заказ 1423/54 Тираж 660 Подпис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4 сел, второй вход которого смещен на один разряд вправо, при этом первый и второй входы блока сравнения являются соответственно первыми и вто5 рым входами компаратора сигнатур.

3. Анализатор по и. 1, о т л и ч аю шийся тем, что следящий компаратор содержит последовательно соединенные первый и второй сумматоры по 10 модулю два, а также В-триггер, Dвход которого соединен с выходом второго сумматора по модулю два, С-вход является третьим входом следящего компаратора,а выход является выходом следящего компаратора, первый и второй входы первого сумматора по модулю два являются соответственно вторым и четвертым входами следящего компаратора, а второй вход второго сумматора по модулю два является первым входом следящего компаратора.

4. Анализатор по п.1, о т л и— ч а ю шийся тем, что фиксатор нестабильности содержит инвертор,вход которого является четвертым входом фиксатора нестабильности, элемент

ИЛИ, первый вход которого является вторым входом фиксатора нестабильности, D-триггер, D-вход которого является первым входом фиксатора нестабильности, С-вход соединен с выходом инвертора, а выход соединен с вторым входом элемента ИЛИ, а также

IK-триггер, 1-вход которого соеди нен с выходом элемента ИЛИ, С-вход является третьим, входом фиксатора нестабильности, а выход является выходом фиксатора нестабильности.