Цифровой фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для ЦИФРОВОЙ обработки сигналов, ; /г / в частности для цифровой фильтрации в различных цифровых комплексах.Цель изобретения .- упрощение устройства. Поставленная цель достигается за счет того, что в состав устройства входят N регистров серии 1.1-1.J, регистр 2 среза, элементы ИЗ, шифратор 4, регистр 5 адреса, блок постоянной памяти 6, сумматор 7, регистр В, элемент И-НЕ 9, блок 10 синхронизации , разряды 11 регистра среза , информационный вход 12, информационный выход 13, тактовый вход 14, вход 15 останова блока синхронизации, выходы 16-19 блока синхронизации. 2 ил. i (Л

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1

ÄÄSUÄÄ 1387 (gp 4 G 06 F 15/353, H 03 Н 17/06

ГОСУДАРСТ8ЕКНЫИ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Р

/ р

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, g н авторском свидктельстам ! Т, Й с;,-, . г °, (21) 4153335/24-24 (22) 27.10.86 (46) 07.04.88. Вюл. ¹ 13 (72) А.Н.Сычев, В.Н.Лясин и В.В.Колесник (53) 68!.32 (088.8) (56) Патент США № 3993890, кл. G 06 F 15/20, 1976.

Авторское свидетельство СССР

¹ 1205152, кл. G 06 F 15/353, 1985. (54) ЦИФРОВОЙ ФИЛЬТР (57) Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для цифровой обработки сигналов, в частности для цифровой фильтрации в различных цифровых комплексах. Цель изобретения — упрощение устройства.

Поставленная цель достигается за счет того, что в состав устройства входят N регистров серии 1.1-1.Л, регистр 2 среза, элементы И 3, шифратор 4, регистр 5 адреса, блок постоянной памяти 6, сумматор 7, регистр 8, элемент И-HE 9, блок 10 синхронизации, разряды 11 регистра среза, информационный вход 12, информационный выход 13, тактовый вход 14, вход 15 останова блока синхронизации, выходы 16-19 блока синхронизации.

2 ил.

1387016

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для цифровой обработки сигналов, в частности для цифровой фильтрации в различных цифровых комплексах.

Цель изобретения — упрощение фильтра.

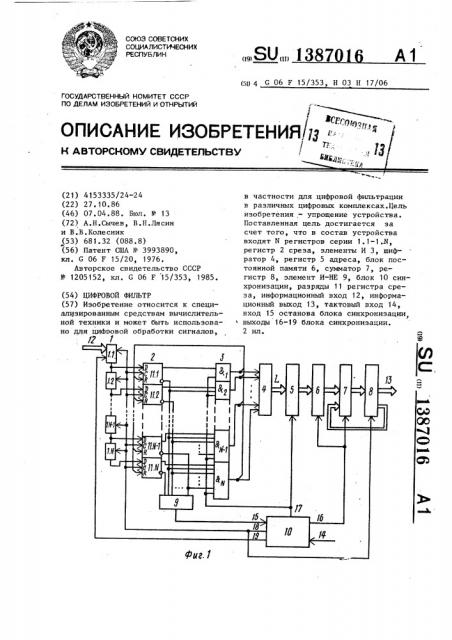

На фиг. 1 приведена функциональная схема цифрового фильтра; на фиг.2 временные диаграммы работы цифрового фильтра.

Цифровбй фильтр (фиг. 1) содержит

N регистров сдвига 1„1 -. 1.N, регистр

2 среза, элементы И 3, шифратор 4, регистр 5 адреса, блок 6 постоянной памяти, сумматоры 7, регистр 8 (выходной), элемент И-HE 9, блок 10 син" хронизации, разряды 11 регистра 2 среза, информационные вход 12 и выход 13 цифрового фильтра, тактовый вход 14 фильтра, вход 15 останова блока синхронизации, первый 16, второй 17, третий 18 и четвертый 19, выходы блока синхронизации.

Работа цифрового фильтра описывается алгоритмом

Y(n) = а; Z,» -(1)

1И где Y(n) " выходная выборка фильтра в и-й момент времени;

N — число выводов из сдвиговых регистров или число операндов, участвующих в формировании передаточной функции; а — коэффициенты, обеспечиваю

1 щие требуемую импульсную характеристику или передаточную функцию фильтра,:

Z, - представленные в двоич" ном цифровом коде выборки входного. сигнала Х„, (для нерекурсивного фильтра i=1,2,...,N, для рекурсивного ь.1,2,...,7) и задержанные выходные сигналы Уп> (1с=1,2,..., ...,В.) для рекурсивного фильтра, V+R=N.

При представлении выборок входного сигнала, а для рекурсивного фильтра и задержанных выборок выходного сигнала, В-разрядным (включая знаковый разряд) числом в дополнительном коде с фиксированной запятой в-

Z; = -Z, o+ Z; ° 2, (2)

45 где Z; — двоичные переменные, = 0 — (В-1), Z;, — значение знакового разряда, после перестановки слагаемых в (1) получают алгоритм цифровой фильтрации в виде вF(Zio Zzo э ° ° э Ено ) y (3) где Г(Е;;, Е,..., Z >)

М а; Е;, j =0 — ( — 1). (4)

i=i

Цифровой фильтр работает. следующим образом.

Перед началом вычисления очередного и-ro выходного отсчета в первый регистр 1.1 сдвига под управлением импульсов записи (фиг.2е) вводится очередная выборка входного-сигнала Х„. Импульс записи новых опе рандов (фиг. 2е) формируется на выходе 19 блока 10 синхронизации с помощью тактового импульса на входе 14 в том случае, если прошло В циклов.

Импульс с выхода 19 блока 10 синхронизации подается на управляющие входы параллельной записи первого регистра 1.1 сдвига. Теперь в N регистрах 1.1-1.N ñäâèãà находятся операнды Z<, Z Z которые для рассматриваемого нерекурсивного цифрового фильтра представляют собой N последних отсчетов входного сигнала

X X ° ° ., Х„

Период вычисления одного выходного отсчета Y(n) по алгоритмам (3) и (4) в предлагаемом цифровом фильтре состоит из В циклов, границы которых показаны пунктирными вертикальными линиями .(Фиг. 2е).

Окончание очередного цикла происходит тогда, когда на всех входах элемента И-НЕ 9 появляется единичный

1 потенциал, следов ательно, на выходе элемента И-НЕ 9 нулевой потенциал. В эуом случае тактовые импульсы (фиг. 2а) с входа 14 проходят на выход 18 блока 10 (фиг. 2а). По переднему фронту этих импульсов- в каждом очередном j""ì (j = 0 — (В-1)) цикле осуществляется сдвиг вправо на один разряд содержимого выходного регистра 8. Таким образом, в соответ15 ствии с формулой (3) выполняется ум. ножение на 2 . суммы, накопленной в результате обработки предыдущих (с номерами меньше j) разрядов операндов. Этими же импульсами (фиг..2с) 1387016 осуществляется сдвиг на один разряд вправо операндов, хранящихся в регистрах 1.1-1.N сдвига, и фиксация очередного (j-го) среза операндов

5 (Е,, Е,..., Z„j ) в И-разрядном регистре 2 среза. Зафиксированный в регистре 2 срез анализируется Nвходовым элементом И-НЕ 9. При этом возможны две ситуации. 10

В первой ситуации все разряды в регистре 2 имеют нулевые значения.

Тогда на выходе элемента И-НЕ 9 присутствует нулевой уровень. В этом случае тактовый импульс не проходит 15 на выход 17 блока 10, поэтому информация с шифратора 4 в регистре 5 адреса не фиксируется. Блок 6 памяти и сумматор — вычитатель 7 неактивизированы, так как на выходе 16 блока 20

10 присутствует нулевой уровень. Никаких арифметических операций цифровой фильтр в этой ситуации не выполняет. Очередной тактовый импульс снова проходит на выход 18 блока 10 и 25 аналогично выполняется следующий ()+I)-й цикл фиксации и анализа среза.

Во второй ситуации, если при выполнении j-ro цикла хотя бы один из 30 триггеров 11.1-11.N регистра 2 среза находится в единичном состоянии, то на выходе элемента И-НЕ 9 появляется единичный уровень и тактовые импульсы с входа 14 пропускаются на выход 17 блока 10 (фиг. 2д). . 35

При этом в течение каждого следующего из P периодов тактовых импульсов код с выхода регистра 2 среза поступает на входы группы 3 элемен- 40 тов И, на выходах которых, за исключением одного, формируются нулевые потенциалы. При поступлении на входы элементов И импульса с выхода 17 блока 10 на выходе элемента И, первый вход которого соединен с прямым выходом старшего значащего разряда регистра 2 среза операндов Z " (i порядковый номер разряда, его прио-, ритет), появляется единичный импульс.

Код с выходов группы 3 элементов И поступает в шифратор 4 на выходе которого формируется L-разрядный код ! (L = log И) номера старшего (в выполняемом такте) значащего разряда среза операндов.

Код старшего нулевого разряда при поступлении тактовых. импульсов с выхода 17 блока 10 фиксируется в регистре 5 адреса. При этом сигналом с выхода 16 блока 10 (фиг. 2б) активизируются блок 6 постоянной памяти и сумматор 7. Из ячейки блока 6 постоянной памяти, адрес которой соответствует коду старшего единичного разряда среза Е;;, считывается весовой коэффициент а °, который в сумматоре 7 складывается с ранее накопленной суммой, хранимой в выходном регистре 8 (сдвиг в выходном регистре после арифметической операции не выполняется). Таким образом, осуществляется операция вычисления F (j) по формуле (4) и одновременное сложение ее с полученной в предыдущих циклах частичной суммой (3) путем сложения (без сдвига) считываемой из памяти величины а; Z с содержимым выходного регистра 8.

В этом же такте импульс с выхода

i-го элемента И группы 3 поступает на установочный вход двухступенчатого триггера 11.i в регистре 2 среза.

По окончании такта триггер 11.i обнуляется. Теперь N âõîäoâîé элемент

И-НЕ 9 анализирует новый код на выходе регистра 2 среза и снова возможны две ситуации: на выходе элемента

И-НЕ 9 находится нулевое значение и цикл обработки среза заканчивается, хотя бы один триггер (из числа имеющих приоритет меньше i) в регистре 2 среза находится в единичном состоянии. В последнем случае указанная операция обработки нового старшего ненулевого разряда повторяется. Так происходит до тех пор, пока все разряды регистра 2 среза не примут нулевое значение. На этом цикл обработки среза заканчивается, на выходе N-входового элемента И-НЕ 9 появляется нулевой уровень, осуществляется очередной сдвиг в выходном регистре 8 и регистрах 1.1-1.N сдвига, а новый (j+1)-й срез фиксируется в регистре 2 среза — начинается новый ()+1)-й цикл. После выполнения В циклов обработки среза вводятся и выдаются из цифрового фильтра новые отсчеты и обработка новых выборок повторяется.

Рекурсивный фильтр отличается от нерекурсивного только тем, что для рекурсивных фильтров регистры 1, 1—

1.N сдвига разбиты на две группы V

1 I и R (V+R=N) последовательно соединенФ ных регистров. Параллельный (m-разрядный) вход первого регистра из второй группы R. 1 подключен к второй ш" разрядной группе вьгкодов выходного регистра 8, которая являетсч выходом

13 фильтра. Управляющие в; оды параллельной записи первых регистров из первой и второй групп V,1 и К.1 объединены и соединены с выходом 19 блока синхронизации. 1Î

Перед началом вычисления очередного и-го выходного отсчета под управлением импульсов (фиг. 2е) в первый регистр сдвига первой группы

V.1 параллельным кодом записывается очередная входная выборка Х„, а в первый регистр сдвига второй группы

R. 1 — предыдущий выходной отсчет Y... поступающий с выхода цифрового фильтра, В И регистрах сдвига находятся операнды Е Z y,, р Z KOTopbIB представляют собой V последних отсчетов входного сигнала Х„, Х„,,..., ° ° * Х,д хранимых в Регистрах пер вой группы, и R последних отсчетов 25 выходного сигнала Y Y„ ..., Y„ ц, хранимых в регистрах втарои группы. Далее процесс обработки операндов Е,, Е,..., Е „ осуществляется аналогично. ЗО

Формула изобретения

Цифровой фильтр, содержащий N регистров сдвига (N — порядок фильтра), регистр среза, блок синхронизации, 35 регистр, сумматоры, блок постоянной памяти, регистр адреса и шифратор, выход которого подключен к информационному входу регистра адреса, выход которого подключен к адресному входу блока постоянной памяти, выход которого подключен к первому информационному ахору с лячатора, выход которого подключен к информационному входу регистра, выход которого является информационным выходом фильтра и подключен к второму информационному входу сумматора, вход синхронизации которого соединен с входом разрешеуия считывания блока постоянной памяти и подключен к первому выходу блока синхронизации, второй выход кото-рого подключен к тактовому входу регистра адреса, третий выход блока синхронизации подключен к тактовым входам регистра, регистра среза и

i-го (i = 1,М) регистра сдвига, выход j-ro (j = 1,N-1) регистра сдвига подключен к 1-му разряду информационного входа регистра среза и информационному входу (j +1) -ro регистра сдвига, выход N-ro регистра сдвига подключен к N-му разряду информациîííîro входа регистра среза, четвертый выход блока синхронизации под— ключен к входу разрешения приема информации i-ro регистра сдвига„ а информационный вход первого регистра. сдвига является информационным входом фильтра, тактовым входом которого является тактовый вход блока синхронизации, отличающийся тем, что, с целью упрощения фильтра, он содержит И элементов И и элемент

И-НЕ, выход которого подключен к входу останова блока синхронизации, прямой выход i-го разряда регистра среза подключен к первому входу i-ro элемента И, второй вход которого подключен к второму выходу блока синхронизации, выход i-ro элемента И подключен к i-му входу шифратора и i-му установочному входу регистра среза, инверсный выход которого подключен к (i+2) ìó входу j-го (j=i+1,N) элемента И и i-му входу элемента И-НЕ.

1387016 ( ъ bb bc 4 Ь

ЦЮ

4w з аэ

Составитель А.Баранов

Редактор И.Шулла Техред А..Кравчук Корректор, Л.Патай

Заказ 1496/49 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскан наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4