Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано для накопления и вывода цифровой информации в старт-стопных магнитных регистраторах, устройствах ввода-вывода вычислительных систем и аппаратуре передачи данных. Устройство содержит блок 1 памяти, счетчик 2 адресов, регистр 3 адресов записи, регистр 4 адресов чтения, блок 5 управления, включающий дешифраторы 6 и 7, триггеры 8, 9, элементы И-НЕ 10, 11, счетчик 12 тактовых импульсов, элементы ИЛИ 13, 14 и генератор 15 тактовых импульсов. Введенные в блок управления новые элементы позволяют использовать устройство в нескольких режимах работы: асинхронном, асинхронно-синхронном и квазисинхронном с автоматическим переходом из одного режима в другой по внешним управляюпдим сигналам . 1 ил.

СОЮЭ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

15Р 4 G 11 С 19 00 л ° .-с ". 7 р х .;.;

13„

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A BTOPCHOMV СВИДЕТЕЛЬСТВУ

„Л7Л4 Сб (21) 3926163/24-24 (22) 08.07.85 (46) 07.04.88. Бюл. № 13 (71) Азербайджанский институт нефти и химии им. М. Азизбекова (72) М. П. Грановский и А. Г. Мельников (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР № 822287, кл. G 11 С 19/00, 1979.

Заявка ФРГ № 2547628, кл. G 06 F 13/00, опублик. 1977. (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТPOACTBO (57) Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано для накопления и вывода цифровой информации

„„Я0„„1387042 А1 в старт-стопных магнитных регистраторах, устройствах ввода-вывода вычислительных систем и аппаратуре передачи данных.

Устройство содержит блок 1 памяти, счетчик 2 адресов, регистр 3 адресов записи, регистр 4 адресов чтения, блок 5 управления, включающий дешифраторы 6 и 7, триггеры

8, 9, элементы И вЂ” НЕ 10, 11, счетчик 12 тактовых импульсов, элементы ИЛИ 13, 14 и генератор 15 тактовых импульсов. Введенные в блок управления новые элементы позволяют использовать устройство в нескольких режимах работы: асинхронном, асинхронно-синхронном и квазисинхронном с автоматическим переходом из одного режима в другой по внешним управляющим сигналам. I ил.

1387042

Формула изобретения

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано для накопления и вывода цифровой информации в старт-стопных магнитных регистраторах, устройствах ввода-вывода вычислительных систем и аппаратуре передачи данных.

Целью изобретения является повышение надежности устройства при одновременном поступлении сигналов записи и чтения данных.

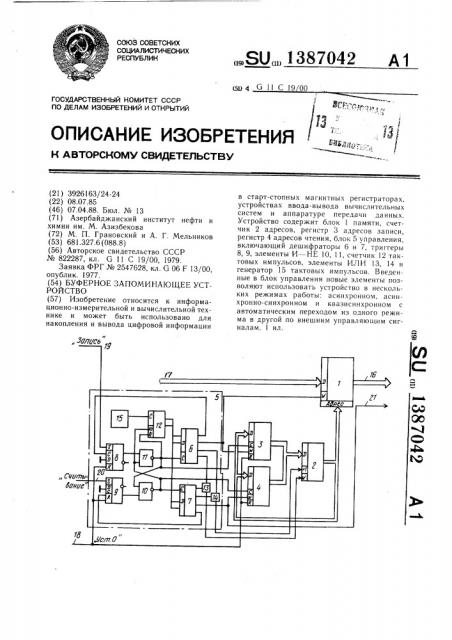

На чертеже показана схема предлагаемого устройства.

Устройство содержит блок 1 памяти, счетчик 2 адресов, регистр 3 адресов записи, регистр 4 адресов чтения, блок 5 управления, включающий дешифраторы 6 и

7, триггеры 8 и 9, элементы И вЂ” НЕ 10 и 11, счетчик 12 тактовых импульсов, элементы

ИЛИ 13 и 14 и генератор 15 тактовых импульсов. Кроме того, устройство имеет информационные выходы 16, информационные входы 17, вход 18 начальной установки, вход

19 записи, вход 20 чтения и выход 21 строба чтения.

Устройство работает следующим образом.

При подаче сигнала на вход 18 «Установка О» сбрасываются в нуль регистры

3 и 4 адресов записи и чтения, а также триггеры 8 и 9, которые запирают элементы

И вЂ” НЕ 10 и 1! и блокируют счетчик 12, а также дешифраторы 6 и 7.

При подаче сигнала записи на вход 19

«Запись» срабатывает триггер 8, открывается элемент И вЂ” HE 11 и включан тся в работу счетчик 12, дешифратор 6 и регистр 3 адресов записи. Сигнал с выхода дешифратора 6 через элемент ИЛИ 13 подается на вход записи регистра 3. При этом хранящийся в регистре 3 адрес записи записывается в счетчик 2. По сигналу с выхода дешифратора 6, поступающему через элемент

ИЛИ 14 на счетный вход счетчика 2 адресов, на выходе счетчика формируется адрес записи.

По сигналу с выхода дешифратора 6, поступающему на вход режима блока 1, входная информация 17 записывается в память по сформированному адресу записи, который одновременно записывается в регистр 3. По сигналу с выхода. дешифратора 6, поступающему на тактовый вход триггера 8 записи, триггер возвращается в исходное состояние и элемент И вЂ” НЕ 11 запирается. В результате блокируются счетчик

12 и дешифратор 6. На этом 4-тактный цикл записи заканчивается. Описанный цикл записи повторяется каждый раз с поступлением на триггер 8 сигнала записи.

При поступлении сигнала чтения на вход

20 срабатывает триггер 9, открывается элемент И вЂ” НЕ 10 и включаются в работу счетчик 12, дешифратор 7 и регистр 4 адресов чтения. Сигнал с выхода дешифрато5

35 ра 7 через элемент ИЛИ 13 поступает навход записи счетчика 2 адресов. При этом хранящийся в регистре 4 адрес считывания записывается в счетчик 2. По сигналу с выхода дешифратора 7, поступающему через элемент ИЛИ 14 на счетный вход счетчика

2 адресов, на выходе счетчика формируется адрес чтения. По сигналу с выхода дешифратора 7, поступающему на вход регистра 4, адрес чтения записывается в регистр

4. Считанная по этому адресу информация с выхода 16 может быть передана потребителю по входу 21 строба чтения. По сигналу с выхода дешифратора 7, поступающему на тактовый вход триггера 9, триггер возвращается в исходное состояние и элемент И вЂ” НЕ

10 запирается. В результате блокируются счетчик 12 и дешифратор 7. На этом 4-тактный цикл считывания заканчивается. Описанный цикл считывания повторяется с поступлением на триггер 9 сигнала чтения.

В случае одновременного поступления в устройство совпадающих по фазе сигналов записи и чтения совместно срабатывают триггеры 8 и 9. При этом включается один из элементов И вЂ” НЕ, так как наличие взаимно блокирующих связей между элементами

И вЂ” НЕ исключает совместное включение двух элементов. Для примера предположим, что включился элемент И вЂ” НЕ 11. В этом случае первым в устройстве начинается цикл записи информации, выполнение которого описано. После окончания цикла записи запирается элемент И вЂ” HE 11 и снимается блокирующий потенциал с элемента 1О, так как триггер 9, запомнивший поступление сигнала чтения, продолжает находиться во включенном (сработанном) состоянии. Элемент 10 открывается и вслед за циклом записи в устройстве выполняется описанный цикл считывания информации.

Буферное запоминающее устройство, содержащее блок памяти, информационные входы и выходы которого являются информационными входами и выходами устройства, регистр адресов записи, регистр адресов чтения, счетчик адресов, выходы которого подключены к адресным входам блока памяти и к информационным входам регистра адресов записи и регистра адресов чтения, и блок управления, первый и второй входы которого являются соответственно входом записи и входом чтения устройства, третий вход блока управления является входом начальной установки устройства и подключен к входам сброса регистра адресов записи и регистра адресов чтениИ, тактовые входы которых подключены соответственно к первому и второму выходам блока управления, третий и четвертый выходы которых подключены к входам записи соответственно регистра адресов запи1387042

Составитель С. Шустенко

Редактор О. Головач Техред И. Верес Корректор Л. Пилипенко

Заказ 1225/50 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 си и регистра адресов чтения, вход режима блока памяти подключен к третьему выходу блока управления, пятый и шестой выходы блока управления подключены соответственно к счетному входу и к входу записи счетчика адресов, отличающееся тем, что, с целью повышения надежности устройства при одновременном поступлении сигналов записи и чтения данных, блок управления содержит генератор тактовых импульсов, счетчик тактовых импульсов, первый и второй дешифраторы, первый и второй триггеры, первый и второй элементы И вЂ” НЕ и пер вый и второй элементы ИЛИ, выходы которых являются соответственно шестым и пятым выходами блока управления, выход генератора подключен к счетному входу счетчика тактовых импульсов, выходы которого подключены к информационным входам первого и второго дешифраторов, первые выходы которых подключены соответственно к тактовому входу первого триггера и к первому входу первого элемента ИЛИ, выход первого элемента И вЂ” НЕ подключен к первому входу сброса счетчика тактовых импульсов, к первому входу второго элемента И вЂ” НЕ, к входу строба первого дешифратора и является первым выходом блока управления, выход второго элемента И вЂ” НЕ является вторым выходом блока управления

5 и подключен к второму входу сброса счетчика тактовых импульсов, к первому входу первого элемента И вЂ” НЕ и к входу строба второго дешифратора, второй выход которого подключен к первому входу второго элемента ИЛИ, второй выход первого дешифратора является третьим выходом блока управления, третий и четвертый выходы первого дешифратора подключены к вторым входам соответственно второго и первого элементов ИЛИ, третий выход второго де15 шифратора является четвертым выходом устройства, четвертый выход второго дешифратора подключен к тактовому входу второго триггера, вход сброса которого подключен к входу сброса первого триггера и является третьим входом блока управления, вторые входы первого и второго элементов

И вЂ” НЕ подключены к выходам соответственно первого и второго триггеров, входы установки которых являются соответственно первым и вторым входами блока управления.