Устройство для управления транзисторным преобразователем

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ди 4 Н 02 М 3 10

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

>Car n-.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ .а„,-,„., (2!) 4017504/24-07 (22) 29.01.86 (46) 07.04.88. Бюл. № 13 (71) Мурманское высшее инженерное морское училище им. Ленинского комсомола и

Научно-исследовательский институт часовой промышленности (72) Н. И. Безгачин, В. И. Веретин и В. Б. Никитин (53) 62! .314.27 (088.8) (56) Авторское свидетельство СССР № 771846, кл. Н 02 М 3/10, 1978.

Авторское свидетельство СССР № 1249603, кл. Н 02 М 3/10, 1984. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ

ТРАНЗИСТОРНЫМ ПРЕОБРАЗОВАТЕЛЕМ (57) Изобретение относится к электротехнике и может быть использовано в транзисторных преобразователях. Целью изобретения является повышение точности стабиÄÄSUÄÄ 1387140 А1 лизации выходного напряжения преобразователя. В данном устройстве погреш ность стабилизации исключается тем, что высокий потенциал управляющего входа второго ключа обеспечивает подключение второго конденсатора к выходу операционного усилителя, а низкий потенциал управляющих входов соответствующих ключей отключает первый конденсатор от выхода интегратора и расшунтирует второй конденсатор. После того, как второй конденсатор подключается к выходу операционного усилителя, но еще не выключен транзистор, и на входе фильтра продолжает присутствовать напряжение, второй конденсатор начинает заряжаться до тех пор, пока не выключится транзистор. После его выключения напряжение остается постоянным и после следующего включения транзистора интегрирование начнется не с нуля, а с добавки, накопленной за счет задержки включения транзистора. 2 ил.

1387140

Изобретение относится к электротехнике и может быть использовано для управления тиристорными преобразователями постоянного тока.

Целью изобретения является повышение точности стабилизации выходного напряжения преобразователя.

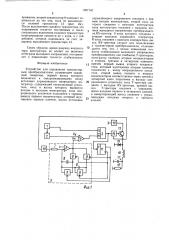

На фиг. 1 представлена функциональная схема устройства и один из вариантов схемы транзисторного преобразователя; на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг. 1) задающий генератор 1, соединенный с истоцником 2 управляющего напряжения и одним входом

RS-триггера 3, второй вход которого соединен с выходом компаратора 4, интегратор 5, состоящий из оперативного усилителя 6, резистора 7, конденсаторов 8, ключей 9, датцика 10 выходного напряжения преобразователя, соединенный с входом интегратора 5, Т-триггер 11, счетный вход которого подключен к выходу триггера 3, а выходы соединены с управляющими входами ключей 9.

Транзисторный преобразователь содержит источник 12 напряжения, силовой транзистор 13, усилитель 14 мощности, вход которого соединен с выходом RS-триггера, служащим для управления силовым транзистором, возвратный диод 15, дроссель 16, конденсатор 17 и нагрузку 18.

Устройство работает следующим образом.

Задающий генератор 1 вырабатывает узкие импульсы (фиг. 2а), которые подаются на вход триггера 3; переводя его в состояние с высоким потенциалом на выходе (фиг. 2д). Высокий потенциал, поступающий с выхода триггера 3 на вход усилителя 14, вызывает появление положительного тока управления силового транзистора 13 (фиг. 2е), что соответствует открытому состоянию транзистора 13 и появлению на его эмиттере положительного, а на выходе датчика 10 отрицательного напряжения, пропорционального мгновенному значению выходного напряжения (фиг. 2б).

Это напряжение, поступая на вход интегратора 5, приводит к линейному нарастанию напряжения на выходе интегратора (фиг. 2в) . Время интегрирования определяется сопротивлением резистора 7 и емкостью конденсатора 8. Это время определяет длительность открытого состояния силового транзистора 13, необходимую для точной стабилизации выходного напряжения на уровне. заданном управляющим напряжением б .

Импульсы, формируемые триггером 3 (фиг. 2д), поступают на вход триггера 11, благодаря чему выходные сигналы триггера 11 переключаются в моменты спада импульсов триггера 3 (фиг. 2ж, э). Высокий потенциал выходных импульсов тригге5

55 ра 11 подключает вторые обкладки одного из конденсаторов 8 к выходу операционного усилителя 6 через ключи 9 и соответственно шунтирует другой конденсатор 8.

В момент времени t, когда напряжение на выходе интегратора V. достигнет величины управляющего напряжения 1Ь, компаратор 4 на короткое время переходит из состояния с нулевым выходным потенциалом в состояние с высоким выходным потенциалом и на его выходе сформируется короткий импульс (фиг. 2г). Это происходит потому, что сформировавшийся на выходе компаратора 4 импульс, поступив на вход триггера 3, переводит его в состояние с нулевым потенциалом на выходе (фиг. 2д), что соответствует отрицательному напряжению на базе силового транзистора 13, поступающему от усилителя 14. Ток базы меняет свое направление на противоположное (фиг. 2е) и начинается процесс рассасывания избыточного заряда в базе.

Процесс рассасывания избыточного заряда, в течение которого транзистор еще находится в открытом состоянии, закончится в тот момент, когда спадет практически до нуля отрицательный ток базы (фиг. 2е).

После этого только закроется силовой транзистор 13 и напряжение на его эмиттере и на выходе датчика 10 станет равным нулю. В этот же момент времени t нулевой потенциал на выходе триггера 3 (фиг. 2д) приводит к изменению состояния триггера 11 на противоположное (фиг. 2ж, з). Высокий потенциал управляющего входа ключа 9 (фиг. 2з) зашунтирует первый конденсатор 8, заряженный к моменту времени t, и конденсатор 8 начинает разряжаться (фиг. 2к) на интервале времени т.

В предлагаемом устройстве погрешность стабилизации, возникающая из-за конечного времени разряда конденсатора, исключается тем, что высокий потенциал (фиг. 2з) управляющего входа второго ключа 9 обеспечивает подключение второго конденсатора

8, разряженного в этот момент (фиг. 2и), к выходу операционного усилителя 6, а низкий потенциал управляющих входов соответствующих ключей 9 (фиг. 2ж) отключает первый конденсатор 8 от выхода интегратора 5 и подключает второй конденсатор 8. Все это приводит к резкому уменьшению напряжения на выходе интегратора 5 (фиг. 2в) и, следовательно, к очень быстрому переходу компаратора 4 опять в состояние с нулевым потенциалом на выходе независимо от инерционности цепи разряда первого конденсатора. После того как второй конденсатор 8 подключается к выходу операционного усилителя (в момент времени фиг. 2), но еще не выключен силовой транзистор 13 и на входе фильтра преобразователя продолжает присутствовать на1387140 пряжение, второй конденсатор 8 начинает заряжаться до тех пор, пока не выключается силовой транзистор 13 (фиг. 2и) .

После выключения силового транзистора это напряжение остается постоянным и после следующего включения силового транзистора интегрирование начнется не с нуля, а с той добавки, которая накопилась за счет задержки выключения транзистора 13.

Таким образом, время разряда конденсатора интегратора не влияет на величину интеграла выходного напряжения, что приводит к повышению точности стабилизации.

Формула изобретения

Устройство для управления транзисторным преобразователем, содержащее задающий генератор, первый выход которого подключен к синхронизирующему входу источника управляющего напряжения, интегратор, содержащий операционный усилитель, вход и выход которого являются входом и выходом интегратора, вход операционного усилителя подключен к первому выводу первого конденсатора, который шунтирован первым ключом, выход источника управляющего напряжения соединен с первым входом компаратора, второй вход которого соединен с выходом интегратора, вход интегратора соединен с выходом датчика выходного напряжения преобразователя,RS-триггер, S-вход которого соединен с вторым выходом задающего генератора, R-вход соединен с выходом компаратора, выход RS-триггера служит для подключения к транзисторам преобразователя, отличаюи ееся тем, что, с целью повышения точности стабилизации выходного напряжения преобразователя, оно снабжено Т-триггером, интегратор снабжен вторым конденсатором и вторым, третьим и четвертым ключами, причем первый вывод второго конденсатора, который шунтирован вторым ключом, подключен к входу операционного усилителя, второй вывод первого и второго конденсаторов соответственно через третин и четвертый ключ подключен к выходу опе20 рационного усилителя, вход Т-триггера соединен с выходом RS-триггера, прямой выход Т-триггера соединен с управляющими входами первого и четвертого ключей, а инвертирующий выход соединен с управляющими входами второго и третьего ключей.

1387140

Составитель В.Миронов

Редактор Г. Волкова Техред И. Верес Корректор М. Демчик

Заказ 1227/55 Тираж 665 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4