Устройство для аналого-цифрового преобразования

Иллюстрации

Показать всеРеферат

Изобретение относится к электроизмерительной вычислительной технике. В устройство для аналого-цифрового преобразования , содержащее аналого-цифровой преобразователь 1, сумматор 3, цифроаналоговый преобразователь 4, усилитель-вычитатель 2 и аналого-цифровой преобразователь 5, введены N-1 усилителей-вычитателей 2, Л/-1 аналого-цифровых преобразователей 5, N элементов 6 задержки, N компараторов 7, мультиплексор 8, задатчик 9 кода, шифратор 10 и блок 11 памяти. За счет правильного выбора числа разрядов в зависимости от скорости изменения входного кодируемого сигнала устройство позволяет повысить точность кодирования быстроизменяюшихся в широком частотном спектре сигналов . 2 ил.

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1387195 A 1

<534 Н 03М 1.18" ась,.„ ""

ri:

ОПИСАНИЕ ИЗОБРЕТЕНИ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4084826/24-24 (22) 04.07.86 (46) 07.04.88. Бюл. № 13 (71) Всесоюзный научно-исследовательский институт электроизмерительных приборов (72) Г. Г. Живилов, Б. К. Лещев, В. А. Прянишников и А. А. Фремке (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 785989, -кл. Н 03 M 1/18, 1980.

Электроника, 1982, № 9, с, 58. (54) УСТРОЙСТВО ДЛЯ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ (57) Изобретение относится к электроизмерительной вычислительной технике. В устройство для аналого-цифрового преобразования, содержащее аналого-цифровой преобразователь 1, сумматор 3, цифроаналоговый преобразователь 4, усилитель-вычитатель 2 и аналого-цифровой преобразователь 5, введены Л вЂ” 1 усилителей-вычитателей 2, N — 1 аналого-цифровых преобразователей 5, _#_ элементов 6 задержки, Л компараторов 7, мультиплексор 8, задатчик 9 кода, шифратор 10 и блок 11 памяти. 3а счет правильного выбора числа разрядов в зависимости от скорости изменения входного кодируемого сигнала устройство позволяет повысить точность кодирования быстроизменяющихся в широком частотном спектре сигналов. 2 ил.

1387195

Формула изобретения

Изобретение относится к электроизмерительной и вычислительной технике и предназначено для преобразования широкополосных сигналов в цифровой код.

Цель изобретения — повышение точности.

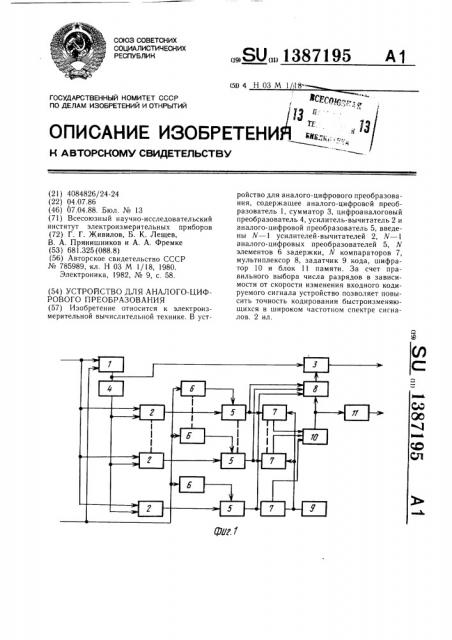

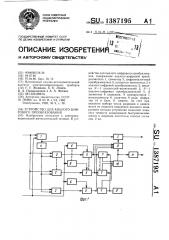

На фиг. 1 показана блок-схема устройства для аналого-цифрового преобразования; на фиг. 2 — графики зависимости среднеквадратического значения погрешности от частоты входного сигнала o„ =f() для структур аналого-цифровых преобразователей (АЦП), работающих по принципу уточнения остатка.

Устройство содержит АЦП 1, усилители 2, сумматор 3, цифроаналоговый преобразователь 4, АЦП 5, элементы 6 задержки, компаратор 7, мультиплексор 8, задатчик 9 кода, шифратор 10 и блок 11 памяти.

Сущность изобретения заключается в оптимальном выборе числа разрядов преобразования в зависимости от частоты входного сигнала. Анализируя приведенные на фиг. 2 графики, можно сделать вывод, что погрешность преобразования быстроизменяющихся в широком диапазоне частот сигналов можно существенно уменьшить, если в зависимости от частоты входного сигнала правильно выбирать число разрядов выходного кода. Критерием для изменения числа разрядов выходного кода Увы. может служить напряжение с выхода усилителя-вычислителя или же, что эквивалентно, выходной код с выхода дополнительного АЦП, увеличение значения которого до значения, близкого к N., (ëðåäåë измерения АЦП 5), >agn служит сйгналом для уменьшения коэффициента усиления усилителя-вычислителя.

Сущность предлагаемого технического решения состоит в том, что код с выходов дополнительных АЦП сравнивается с помощью цифровых компараторов с кодом уставки Nyc., значение которого выбирается равным или меньшим значения N„,„, задаваемым задатчиком кода. Результаты сравнения шифруются и мультиплексор подключает к входу сумматора выход того дополнительного АЦП, который обеспечивает максимально возможную разрядность выходного кода при соблюдении условия. В блоке памяти, представляющем собой постоянное запоминающее устройство, предварительно записаны коды максимальной погрешности преобразования устройства, причем в каждой ячейке этот код соответствует разрядности результата преобразования. Таким образом, по окончании преобразования информация о разрядности выходного кода и максимальная погрешность преобразования поступают от блока памяти на второй выход устройства.

Устройство для аналого-цифрового преобразования работает следующим образом.

Импульсом «Пуск» запускается АЦП 1, который кодирует входной сигнал. Резуль5

35 тат преобразования поступает на первый вход сумматора 3 и на вход цифроаналогового преобразователя 4, который преобразует код первого такта преобразования в аналоговое напряжение. Это напряжение вычитается из входного сигнала и усиливается N усилителями-вычитателями 2.

Коэффициенты усиления N усилителей-вычитателей 2 устанавливаются равными от 2 до 2", где и — разрядность АЦП 1. Напряжения с выходов усилителей-вычитателей 2 поступают на информационные входы аналого-цифровых преобразователей 5.

Запуск аналого-цифровых преобразователей 5 осуществляется с помощью N элементов 6 задержки. Время задержки относительно запускающего импульса «Пуск» различное у каждого из N элементов 6 задержки и определяется временем окончания переходного процесса установления конкретного усилителя-вычитателя. Коды с выхода дополнительных АЦП 5 сравниваются N компараторами 7 с кодом уставки, задаваемым задатчиком 9 кода. Величина кода уставки выбирается меньшей или равной коду предела преобразования АЦП 5. Результаты сравнения шифруются шифратором 10, и мультиплексор 8 подключает к второму входу сумматора 3 выход того АЦП 5, который обеспечивает максимальную разрядность выходного кода при соблюдении условия

Л4чп (Л4у-. Одновременно код с шифратора

10, являющийся адресом соответствующей ячейки памяти блока 1 памяти, подключает к второму выходу устройства информацию с выхода блока 11 памяти, где записана заранее максимальная погрешность преобразования при соответствующей разрядности выходного кода.

Результаты первого и второго тактов преобразования суммируются сумматором 3 и результат преобразования выдается на вы ход устройства.

Устройство для аналого-цифрового преобразования, содержащее первый аналого-цифровой преобразователь, информационный вход которого является входной шиной и соединен с первым входом первого усилителя-вычитателя, второй вход которого подключен к.выходу цифроаналогового преобразователя, вход которого объединен с первым входом сумматора и подключен к выходу первого аналого-цифрового преобразователя, управляющий вход которого является шиной запуска, выход усилителя-вычитателя подключен к информационному входу второго аналого-цифрового преобразователя, а выход сумматора является выходной шиной, отличающееся тем, что, с целью повышения точности, в него введены N — 1 усилителей-вычитателей, (N — 1) дополнительных аналого-цифровых преобразовате1387195

Фие. 2

Составитель Н. Козлов

Редактор П. Гереши Тех ед И. Ве ес

Заказ 1232/58 р д И. Верес Корректор Н. Король

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

П

113035, Москва, К вЂ” 35, Раушская наб, 4/5 роизводственно-полиграфическое предприяти, . У а., д. тие, r. жгород, ул. Проектная, 4 леи, аналогичных второму аналого-цифровому преобразователю, N элементов задержки, N компараторов, мультиплексор, задатчик кода, шифратор и блок памяти, где N — количество каналов устройства, а первые и вторые входы (N — 1) усилителя-вычитателя объединены соответственно с первым и вторым входами первого усилителя-вычитателя, выходы подключены к информационным входам соответствующих (N — 1) дополнительных аналого-цифровых преобразователей, управляющие входы которых через соответствующие (N — 1) элементы задержки и управляющий вход второго аналого-цифрового преобразователя через первый элемент задержки объединены с управляющим входом первого аналого-цифрового преобразователя, выходы второго и дополнительных аналого-цифровых преобразователей соеди5 иены с соответствующими информационными входами мультиплексора и первыми входами соответствующих компараторов, вторые входы которых подключены к выходу задатчика кода, а выходы соединены с соответствующими входами шифратора, выход которого подключен к адресным входам мультиплексора и блока памяти, выход мультиплексора подключен к второму вход с ммат у тора, а выход блока памяти являетму входу ся дополнительной выходной шиной.