Устройство для преобразования частоты следования импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и преобразовательной технике и может быть использовано в системах цифровой фазовой синхронизации. Цель изобретения - повышение быстродействия формирования выходной импульсной последовательности. Устройство цифрового преобразования частоты следования импульсов содержит группу 1 из N+L последовательно соединенных счетных триггеров, формирователь 2 импульсов, элемент ИЛИ 3, jV-разрядный регистр 4, группу 5 из элементов задержки, группу 6 из N элементов стробирования и L+1-разрядный сумматор 7. Введение в устройство группы 6 из /V элементов стробирования, L+1-разрядного сумматора 7, формирователя 2 задержки позволяет повысить быстродействие и уменьшить время задержки формирования выходной импульсной последовательности при смене управляющего кода до величины, не превышающей периода следования импульсов преобразуемой последовательности . 2 ил. (Q (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1387199 А1 511 4 Н 03 М 1/60, Н 03 В !9/00

Ц ( с„

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4065695/24-24 (22) 11.05.86 (46) 07.04.88. Бюл. № 13 (72) Ф. M Андреев, В. Н. Лебедев и В. В. Райда (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 843157, кл. Н 03 В 19/00, 1981.

Жодзищский М. И. и др. Цифровые системы фазовой синхронизации.— М.: Советское радио, 1980, с. 49, рис. 1 — 22,а. (54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ

ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ (57) Изобретение относится к автоматике и преобразовательной технике и может быть использовано в системах цифровой фазовой синхронизации. Цель изобретения — повышение быстродействия формирования выходной импульсной последовательности. Устройство цифрового преобразования частоты следования импульсов содержит группу 1 из

N+ L последовательно соединенных счетных триггеров, формирователь 2 импульсов, элемент ИЛИ 3, N-разрядный регистр 4, группу 5 из элементов задержки, группу 6 из N элементов стробирования и 1.+1-разрядный сумматор 7. Введение в устройство группы 6 из N элементов стробирования, L+1-разрядного сумматора 7, формирователя 2 задержки позволяет повысить быстродействие и уменьшить время задержки формирования выходной импульсной последовательности при смене управляющего кода до величины, не превышающей периода следования импульсов преобразуемой последовательности. 2 нл. S

13871

Формула изобретения

Изобретение относится к автоматике и преобразовательной технике и может быть использовано в системах цифровой синхронизации связных станций.

Цель изобретения — повышение быстродействия формирования выходной импульсной последовательности.

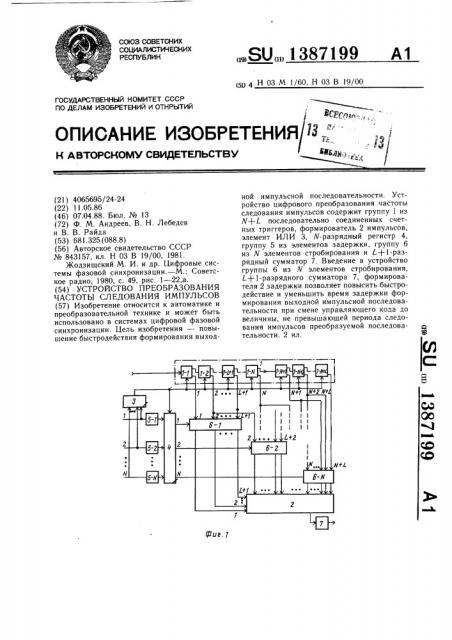

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство цифрового преобразования частоты следования импульсов содержит группу из (N+L) последовательно соединенных счетных триггеров, формирователь

2 импульсов, элемент ИЛИ 3, N-разрядный регистр 4, группу 5 из N элементов задержки, группу 6 из N элементов стробирования и (L+1) -разрядный сумматор 7.

Устройство работает следующим образом.

При поступлении управляющего импульсного кода на входную шину цифрового управления на выходе элемента ИЛИ 3 формируется импульсный сигнал, устанавливающий в единичное состояние счетные триггеры 1 — 1 — 1 — (N+L) и обнуляющий N-разрядный регистр 4. В результате блокируются элементы 6 — 1 — 6 — N стробицирования, на выходах которых формируются сигналы «Лог

0», поступающие на входы (L+1) -разрядного сумматора 7. При этом на выходе (L+

+1)-го разряда сумматора 7 присутствует сигнал «ЛогО».

Через некоторое время, задаваемое элементами 5 — 1 — 5 — Nзадержки,,в (Ч-разрядный регистр 4 заносится новое значение Y управляющего кода, в соответствии с которым открываются соответствующие элементы стробирования группы 6. С поступлением на вход счетного триггера 1 — 1 первого импульса входной преобразуемой последовательности с частотой f ° следования импульсов (фиг. 2а) на инверсных выходах всех (N+L) счетных триггеров формируются уровни «Лог. l ». Уровни напряжения «Лог.!» через соответствующие открытые элементы 6 стробирования поступают на входы (L+1)разрядного сумматора 7, на выходе (L+1)го разряда которого формируется сигнал

«Лог. 1». В результате изменения напряжения на выходе (L+1) -го разряда сумматора

7 с уровня «Лог.О» на «Лог. l » формирователь 2 импульсов на своем выходе формирует первый импульс выходной преобразованной последовательности импульсов.

При поступлении на вход группы 1 счетных триггеров очередных импульсов входной последовательности на инверсных выходах счетных триггеров формируется линейно убывающий двоичный код. Сигналы с инверсных выходов с -ro по (i+L)-й счетных тригге99

2 ров через -й открытый элемент 6 стробирования поступают на i-e входы (L+1) -разрядного сумматора 7, который обеспечивает суммирование кодов чисел по модулю

2 "+ 1. В зависимости от значения Y управляющего кода на выходах (L+1) -разрядного сумматора 7 формируется изменяющийся во времени код. На фиг. 2б — ж показано формирование кодов на выходах (L+1) -разрядного сумматора 7 для случаев, соответствующих десятичному эквиваленту Z управляющего кода 1, 2, 3, 4, 5 и 7 соответственно.

Формирователь 2 импульсов вырабатывает стандартные импульсы каждый раз, когда сигналы на выходе (L+1)-го разряда сумматора 7 изменяются с уровня «Лог.О» на «Лог.l» (фиг. 2 з — н). Задержка формирования первого импульса выходной последовательности относительно момента времени смены управляющего кода не превышает интервала времени, равного периоду следования импульсов входной импульсной последовательности.

5 l0

Устройство преобразования частоты следования импульсов, содержащее группу из (N+L) последовательно соединенных счетных триггеров, счетный вход первого из которых является входной информационной шиной, N-разрядный регистр и элемент ИЛИ, отличающееся тем, что, с целью повышения быстродействия формирования выходной импульсной последовательности, в него введены группа из N элементов стробирования, (L+ 1)-разрядный сумматор с N входами, формирователь импульсов и группа из N элементов задержки, входы которых объединены с соответствующими входами элемента ИЛИ и являются входной шиной цифрового управления, выходы элементов задержки группы соединены с соответствующими информационными входами N-разрядного регистра, выходы которого подключены к входам стробирования соответствующих элементов стробирования группы, а вход установки в нулевое состояние объединен с одноименными входами (N+L) -x счетных триггеров группы и подключен к выходу элемента ИЛИ. инверсные выходы с i-го по (i+L)-й счетных триггеров группы соединены с соответствующими информационными входами -го элемента стробирования группы, выходы каждого i-ro элемента стробирования группы соединены с соответствующими -ми входами (L+1) -разрядного сумматора с N входами, выход (L+1)-го разряда которого подключен к входу формирователя импульсов, выход которого является выходной шиной, причем i=I, 2,..., N.

1387199

Составитель Н. Капитанов

Редактор П. Гереши Техред И. Верес Корректор О. Кундрик

Заказ 1232 58 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4