Устройство для деления чисел с фиксированной запятой

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может найти применение в специализированных системах обработки информации. Цель изобретения состоит в повышении точности вычислений. Поставленная цель достигается тем, что устройство для деления чисел с фиксированной запятой, содержащее сумматор 1, блоки 2, 3 элементов И, элементы И 4, 5, 6, счетчик 10 аргумента и регистр 18, содержит элемент ИЛИ 11 и счетчик 17 частного с соответствующими связями. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51)4 G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4149961/24-24 (22) 20.11.86 (46) 15.04.88. Бюл. Ф 14 (72) И.П.Галабурда, А. Г.Пичугин, А.И.Буков и В.П.Лачугин (53) 681 . 325 (088. 8) (56) Авторское свидетельство СССР

Ф 1203514, кл. G 06 F 7/52, 1984.

Авторское свидетельство СССР

Ф 1059570, кл. G 06 F 7/52, 1982. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ С

ФИКСИРОВАННОЙ ЗАПЯТОЙ (57) Изобретение относится к цифро„„SU„„1 8853 А I вой вычислительной технике и может найти применение в специализированных системах обработки информации.

Цель изобретения состоит в повышении точности вычислений. Поставленная цель достигается тем, что устройство для деления чисел с фиксированной запятой, содержащее сумматор l, блоки 2, 3 элементов И, элементы И 4, 5, 6, счетчик 10 аргумента и регистр

18, содержит элемент ИЛИ ll и счетчик 17 частного с соответствующими связями. 1 ил.!

388853

1О

30 дятся.

Изобретение относится к вычислительной технике и может найти применение при создании специализированных систем переработки цифровой информации.

Целью изобретения является повышение точности вычислений.

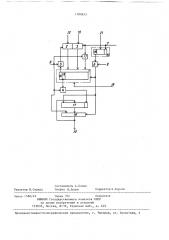

На чертеже представлена схема предлагаемого устройства для деления чисел с фиксированной запятой.

Устройство содержит сумматор 1, блоки 2 и 3 элементов И, элементы

И 4-6, тактовые входы 7-9 устройства, счетчик 10 аргумента, элемент ИЛИ 11, прямой вход 12 делителя устройства, инверсный выход 13 знакового разряда .,сумматора 1, прямой выход 14 знакового разряда сумматора 1, инверсный выход 15 знакового разряда счетчика

10 аргумента, инверсный вход 16 делителя устройства, счетчик 17 частного, регистр 18, вход 19 делимого устройства,,выход 20 частного устройства, вход 21 аргумента устройства.

На тактовые входы 7-9 устройства поступает последовательность импульсов.

Алгоритм работы устройства для получения и-разрядного частного следующий.

Выполняется r циклов формирования старших разрядов частного. При этом в каждом цикле: от аргумента r вычитается единица; по формуле х = х + у вычисляется остаток; по формуле

Е Zñ+I ó при х >О; с

Z+ P прих О, формируются значения старших разрядов частного и, если полученный оста ток х меньше нуля, то по формуле х = х+у производится его восстановление.

Выполняется и-r циклов определения младших разрядов частного.

Устройство работает следующим образом.

Для реализации деления делимое х направляется в сумматор 1, делитель у — на входы 12 и 16 делителя, аргумент (-r) масштабного множителя, представленный в дополнительном коде, — в счетчик 10 аргумента. Пусть необходимо реализовать пример

2 0 !010

Х

0,0110

В этом случае ня входе 12 делителя будет находиться код 0,0110, в сумматоре — 1 — 0,1010, в счетчике аргумента †.1,101 .

Для определения (n=4) цифр частного выполняется 4 цикла деления. Для (r=3) первых циклов устройство работает следующим образом.

В первом такте (тактовый вход 7) каждого цикла из кода на сумматоре вычитается делитель и производится прибавление единицы, к содержимому счетчика 10 аргумента. Во втором такте (тактовый вход 8) в случае, если на сумматоре 1 остаток положителен, то по переднему фронту сигнала с.тактового входа 8 на счетный вход счетчика 17 поступает единица. Кроме тоro, по заднему фронту сигнала с тактового входа 8 производится запись содержимого счетчика 17 на регистр

18, и, если на сумматоре I остаток отрицателен, то производится его восстановление (к остатку прибавляется делитель).

По третьему такту для r первых циклов в устройстве арифметические и логические действия не произво-, Для последующих циклов в первом и втором такте устройство работает аналогично описанному. По третьему такту на входе элемента И 6 возникает сигнал, по переднему фронту которого производится сдвиг на один разряд влево содержимого сумматора

1 и регистра 18, а по заднему фронту этого сигнала производится переза" пись содержимого регистра 18 на счетчик 17.

Для нашего примера формирование частного на выходном регистре 18 в зависимости, от содержимого сумматора

1, счетчика 10 аргумента и счетчика

17 происходит следующим образом.

В первом цикле деления по сигналу (тактовый вход 7) инвертированное значение делителя с входа 16 (1,1001) складывается с содержимым сумматора

1 (0,1010). На сумматоре 1 образуется код 0,0100. По переднему фронту сигнала (тактовый вход 8) на выходе первого элемента И 4 возникает единичный сигнал, по которому на счетный вход счетчика 17 поступает единичный сигнал. На счетчике 17 образу ется код 0001, который по заднему

1388853

В четвертом цикле деления по сигналу (тактовый вход 7) на сумматоре 30

1 образуется код 0,0010. По переднему фронту сигнала (тактовый вход 8) на выходе первого элемента И 4 возникает сигнал, по которому на счетный вход счетчика 17 поступает единичный сигнал. На счетчике 17 образуется

35 код 0011, который по заднему фронту переписывается на регистр 18. По переднему фронту третьего сигнала (тактовый вход 9) содержимое регистра 18 4О сдвигается на один разряд влево.

После окончания четвертого цикла на регистре 18 будет сформирован код

00110, который после добавления знакового разряда (формирование знакового разряда не рассматривается) будет иметь вид 0,00110.

Среднеквадратическая ошибка деле- 0 ния по алгоритму предлагаемого устройства может быть определена по формуле

Г

° 2 3

55

-n у=у „„=2 для x = х„, „ фронту сигнала (тактовый вход 8) переписывается на регистр 18.

Бо втором цикле деления по сигналу (тактовый вход 7) на сумматоре 1 формируется отрицательный код 1,1101, 5 а на счетчике 10 аргумента — код

1lll. По переднему фронту сигнала (тактовый вход 8) производится восстановление остатка х = 1,1101 и на сумматоре 1 образуется код 0,0100.

В третьем цикле деления по сигналу (тактовый вход 7) на сумматоре 1 (формируется отрицательный код 1,1101, а на счетчике 10 аргумента — код

0000. По переднему фронту сигнала (тактовый вход 8) производится восстановление остатка Х и на сумматоре

1 образуется код 0,0100. По передне му фронту сигнала (тактовый вход 9) производится сдвиг на один разряд влево содержимого сумматора 1 и регистра 18. На сумматоре 1 образуется код 0,1000, а на регистре )8 — код

0,0010. По заднему фронту этого сигнала содержимое регистра 18.переписывается на счетчик 17.

Ф о р м у л а и з о б р е т е н и я

Устройство цля деления чисел с фиксированной запятой, содержащее сумматор, два блока элементов И, три элемента И, счетчик аргумента и регистр, причем вход делимого устройства соединен с установочным входом сумматора, вход разрешения сдвига влево которого соединен с входом разрешения сдвига влево регистра, выход которого является выходом частного устройства, вход аргумента которого соединен с установочным входом счетчика аргумента, прямой и инверсный входы делителя устройства соединены соответственно с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с входами первого и второго слагаемых сумматора, инверсный и прямой выходы знакового разряда которого соединены соответственно с первыми входами первого и второго элементов И, первый тактовый вход устройства соединен с вторым входом второго блока элементов И, второй тактовый вход устройства соединен с вторыми входами первого и второго элементов И, выход второго элемента И соединен с вторым входом первого блока элементов И, инверсный выход знакового разряда счетчика аргумента соединен с первым входом третьего элемента И, второй вход которого соединен с третьим тактовым входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повьппения точности вы— числений, оно содержит счетчик частного и элемент ИЛИ, причем первый тактовый вход устройства соединен со счетным входом счетчика аргумента и с первым входом элемента ИЛИ, выход которого соединен с входом разрешения сложения сумматора, вход разрешения сдвига влево которого соединен с выходом третьего элемента И, и с входом разрешения записи счетчика частного, второй тактовый вход устройства соединен с вторым входом элемента ИЛИ и с входом разрешения записи регистра, выход которого соединен с информационным входом счетчика частного, выход которого соединен с информационным входом регистра, выход первого элемента И соединен со счетным входом счетчика частного.!

388853

Составитель А.Клюев

Техред M.ÄHäûê

Редактор Ю.Середа

Корректор Н.Король

Заказ 1580/49

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4