Устройство для адресации блоков памяти

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

П9) (11) (51) 4 G 06 F 12/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1298755 (21) 4116906/24-24 (22) 08.09.86 (46) 15.04.88. Бюл. Р 14 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) А.В.Ковалев, В.Ю.Лоэбенев, А,П.Купровский, Н.Г.Пархоменко и А ° Н.Халявка (53) 681.325 (088.8) (56) Авторское свидетельство СССР

У 1298755, кл. G 06 F 12/00, 1985, (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ БЛОКОВ

ПАМЯТИ (57) Изобретение относится к вычислительной технике. Целью изобретения является расширение функциональных возможностей за счет реализации обращения к частично годным модулям памяти. Поставленная цель достигается путем введения в состав устройства для адресации блоков памяти, элемента ИЛИ, выход которого является выходом выборки модуля устройства и и групп элементов И, каждая из которых коммутирует физический адрес блока памяти, признанного годным при предварительной проверке. Устройство формирует непрерывное поле математических адресов годных блоков памяти, входящих в систему, и выдает общее число годных блоков. 2 ил, 1388875

Изобретение относится к вычислительной технике, предназначено для адресации блоков памяти в системе памяти и является дополнительным к авт.св. N - 1298755.

Целью изобретения является расширение функциональных возможностей за счет реализации обращения к частично годным модулям памяти.

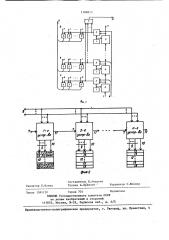

На фиг.1 представлена функциональная схема устройства для адресации блоков памяти; на фиг.2 — соединение устройств для адресации блоков памяти при работе в системе памяти.

Устройство содержит группу переключателей 1, группу сумматоров 2, группу элементов 3 сравнения, элемент ИЛИ 4, m групп элементов И 5 и имеет вход 6 текущего адреса устройства, вход 7 начального адреса устройства, m входов 8 адресов годных блоков, выход 9 адреса устройства, выход 10 выборки модуля устройства, выход 11 конечного адреса устройства. Кроме того, на фиг.2 показаны модули 12 памяти, содержащие m блоков 13 памяти каждый.

Устройство работает следующим образом.

Формирование непрерывного адресного поля по гоцным блокам 13 памяти модулей 1? памяти аналогично устройству-прототипу.

Математические адреса годности годных блоков 13 памяти, поступающие на вход 6 текущего адреса устройства, вызывают срабатывание соответствующих элементов 3 сравнения.

Сигнал с выхода сработавшего i-го (i = 1,...,m) элемента 3 сравнения вызывает появление сигнала выборки модуля на выходе 10 устройства и оцновременно открывает i-ю группу элементов И 5, на вторые входы которых постоянно подается физический адрес

i-го блока 13 памяти.

С выходов элементов И 5 i-й группы фттзический адрес годного блока 13 памяти поступает на выход 9 устройства и далее в модуль 12 памяти.

Обращение к негодному блоку 13 памяти (например, j-му) в предлагаемом устройстве блокируется j ì переключателем.

Допустим, что требуемая емкость системы памяти Ц определяется следующим образом:

g = К,К тпптт, 10 где q

Формула изобретения

Устройство для адресации блоков памяти по авт.св. N 1298755, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет реализации обращения к частично годным модулям памяти, в него введены элемент ИЛИ и m групп элементов И, причем первые входы элеменТоН И i-Й (i = 1, ° ° °,m) группы соедиHeны с выходом 1.-го элемента сравнения и с i-м входом элемента ИЛИ, выход которого является выходом выборки модуля устройства, вторые входы

50 элементов И 1-й группы являются i-м входом адреса годного блока памяти устройства, выходы элементов И всех

m групп подключены к соответствующим разрядам адресного выхода устройства. — емкость блока 13 памяти; — число блоков 13 в модуле 12 памяти;

n — число модулей 12 памяти;

К, — средний коэффициент годнос15 ти модулей 12 памяти (К, 1/m, 2/m, m/m);

К вЂ” требуемый коэффициент запаса по емкости (К 1) .

Тогда для построения такой систе20 мы памяти потребуется и устройств для адресации блоков памяти, содержащих тп групп элементов И 5, m элементов 3 сравнения, m сумматоров 2, m переключателей 1 и элемент ИЛИ 4

25 каждое. Соединение устройств между собой видно из фиг.2. При этом на выходе 11 n-ro устройства появится ма- тематический адрес последнего годного блока 13 памяти и-ro модуля 12, численно равный общему числу годных блоков 13 в системе памяти, если на вход 7 1-го устройства подается нулевой начальный адрес.

1388875

Составитель И.Андреев

Техред А.Кравчук

Корректор С.П!екмар

Редактор Е.Копча

Заказ 1581/50 Тираж 704 Подписное

ВНИИПИ Государственного комитета .СССР по делам изобретений и открытий

113035, Москва, -35 ° Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4