Счетчик адресации для прямого доступа к памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности для передачи информации при прямом доступе к памяти. Цель изобретения - расширение функциональных возможностей счетчика адресации зй счет обеспечения побайтовой передачи информации в память и расширения адресного пространства при адресации прямого доступа к памяти. Счетчик содержит шесть триггеров, шесть магистральных передатчиков, элементы И, ИЛИ и НЕ.- Счетчик предназначен для использования в устройствах, имеющих прямой доступ к памяти. Для согласования с каналом микроЭВМ магистральные передатчики имеют три состояния на выходе. Счетчик позволяет производить байтовую передачу информации. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) 79 А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4118197/24-?4 (22) 10.09.86 (46) 15.04.88. Вюл. Р 14 (72) П.Я.Комарченко, В.С.Лопатин, В.M.Ìàòâååâ, В.А.Машаров и M.b.Ö åêèí (53) 681.325 (088.8) (54) СЧЕТЧИК АДРЕСАЦИИ ДЛЯ ПРЯМОГО

ДОСТУПА К ПАМЯТИ (57) Изобретение относится к вычислительной технике, в частности для передачи информации при прямом доступе к памяти. Цель изобретения— расширение функциональных возмож(51) 4 С 06 Р 13/28 Н 03 К 23/00 ностей счетчика адресации за счет обеспечения побайтовой передачи информации в память и расширения адресного пространства при адресации прямого доступа к памяти. Счетчик содержит шесть триггеров, шесть магистральных передатчиков, элементы

И, HJIH и НЕ; Счетчик предназначен для использования в устройствах, имеющих прямой доступ к памяти. Для согласования с каналом микроЭВМ магистральные передатчики имеют три состояния на выходе. Счетчик позволяет производить байтовую передачу информации. 1 ил, 1388879

Изобретение относится к вычислительной технике и может быть применено для блочной передачи информации при прямом доступе к памяти.

Цель изобретения — расширение

5 функциональных возможностей за счет обеспечения побайтовой передачи информации в память и расширения адресного пространства при прямом дос- 10 тупе к памяти.

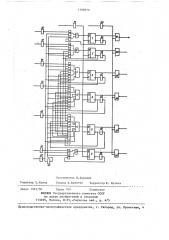

На чертеже изображена структурная схема счетчика адресации для прямого доступа к памяти.

Счетчик содержит шесть триггеров

1-6, шесть элементов 7-12 НЕ, двадцать два элемента 13-34 И, формирователь 35 импульсов,, выполненный на элементе И, пятнадцать элементов

36-50 НЕ и шесть магистральных передатчиков 51-56.

Высокий уровень сигнала на входе разрешения прямого доступа устанавливает выходы магистральных передатчиков 51-56 в высокоимпедансное состояние. При низком уровне сигнала на входе разрешения прямого доступа разрешается прохождение адреса для прямого доступа с выходов триггеров

1-6 через магистральные передатчики

51-56.

Информация, содержащаяся в разряде АДОО, указывает на выполнение операции с младшим байтом при низком логическом уровне сигнала АДОО или старшим байтом при высоком логическом уровне сигнала на линии АДОО.

Таким образом, информация, содержащаяся в этом разряде, должна быть передана без изменения в течение всего цикла блочной передачи.

Для организации блочной передачи по 16-ти адресам необходимо четыре разряда счетчика адресации, Разряд АД05 также передается без

Ю 45 изменения в течение половины цикла адресации для прямого доступа к паI мяти и служит для расширения адресного пространства.

Количество адресуемых ячеек памяти определяется количеством импульсов, 50 поступающих на вход синхронизации и максимально может составлять 16 адресов.

Начальный адрес каждой передачи информации при прямом доступе к памяти определяется информацией, содержащейся на шинах АД(05-00), защелкиваемой установкой из низкого логического уровня в высокий логический уровень сигналов на входах синхронизации и разрешения счета.

Для организации блочного режима передачи прямого доступа к памяти необходимо наращивание адресов от исходного блоками дважды по 16. Блочный режим передачи информации существенно экономит время, необходимое для обновления содержимого памяти, так как для обращения к 32-м последовательным ячейкам памяти необходимо вырабатывать исходный адрес только один раз.Для осуществления действия по наращиванию адресов применяется предлагаемый счетчик адресации для прямого доступа памяти, Информация на шине АД05 при низком логическом уровне обеспечивает адресацию к первым 16-ти адресам, при высоком логическом уровне — к последующим

l6-ти адресам.

Формула и з обретения

Счетчик адресации для прямого доступа к памяти, содержащий четыре триггера, шесть элементов НЕ, двенадцать элементов И, инверсные выходы с первого по четвертый триггеров соединены с входами с первого по четвертый элементов НЕ соответственно, выход первого элемента НЕ соединен с первым входом первого элемента И, выход второго элемента НЕ сое-: динен с первыми входами с второго по пятый элементов И, выход третьего элемента НЕ соединен с первыми входами с шестого по Восьмой элементов

И и вторым входом третьего элемента

И, выход четвертого элемента HE соединен с первыми входами девятого и десятого элементов И и вторыми входами четвертого и седьмого элементов И, инверсный выход четвертого триггера соединен с первыми входами одиннадцатого и двенадцатого элемен-. тов И, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения побайтовой передачи информации в память и расширения адресного пространства при прямом доступе к памяти, в него введены два триггера, шесть магистральных передатчиков, формирователь импульса, шесть элементов ИЛИ, десять элементов И, одиннадцать элементов НЕ, вход синхрони1388879 зации счетчика через формирователь импульсоа соединен с входами синхронизации с первого по шестой триггеров, прямые выходы которых соединены с информационными входами с первого по шестой магистральных передатчиков соответственно, выходы которых являются выходами счетчика, вход разрешения прямого доступа счетчика через 0 пятый элемент НЕ соединен с входами управлением передачей с первого па шестой магистральных передатчиков, инверсный выход пятого триггера соединен с вторым-входом двенадцатого элемента И, инверсный выход шестого. триггера через шестой элемент НЕ соединен с первым входом тринадцатого элемента И, инверсный выход пятого триггера через седьмой элемент НЕ соединен с первым входом четырнадцатого элемента И и вторыми входами пятого, восьмого и десятого элементов И, инверсный выход второго триггера соединен с первыми входами пят- 25 надцатого и шестнадцатого элементов

И, вторым входом одиннадцатого элемента И, и третьим входом двенадцатого элемента И инверсный выход третьего триггера соединен с вторым ЗО входом шестнадцатого элемента И, третьим входом одиннадцатого элемейта И и четвертым входом двенадцатого элемента И, выходы с восьмого по тринадцатый элементов НЕ являются информационными входами счетчика, 35 выходы с восьмого по тринадцатый элементов НЕ соединены с первыми входами с семнадцатого по двадцать второй элементов И соответственно, выходы с первого по шестой элементов

ИЛИ .соединены с информационными входами с первого по шестой триггеров соответственно, выходы первого .и семнадцатого элементов И соединены с первым и вторым входами первого элемента И И соответственно, выходы второго, пятнадцатого и восемнадцатого элементов И соединены с первого по третий входами второго элемента

ИЦИ соответственно, выходы третьего, шестого, шестнадцатого и девятнадцатого элементов И соединены с первого по четвертый входами третьего элемента HJIH соответственно, выходы четвертого, седьмого, девятого, одиннадца,того и двадцатого элементов И соединены с первого по пятый входами четвертого элемента ИЛИ соответственно, выходы пятого, восьмого, десятого, двенадцатого, четырнадцатого и двадцать первого элементов И соединены с первого по шестой входами пятого элемента ИЛИ соответственно, выходы тринадцатого и двадцать второго элементов И соединены с первым и вторым входами шестого элемента ИЛИ, вход разрешения счета счетчика через четырнадцатый элемент НЕ соединен с входом пятнадцатого элемента НЕ, вторыми входами второго, шестого, девятого, четырнадцатого элементов

И и вторыми входами с семнадцатого по двадцать второй элементов И, выход пятнадцатого элемента НЕ соединен с вторыми входами первого, тринадцатого и пятнадцатого элементов И, третьими входами с второго по десятый элементов И, третьими входами четырнадцатого и шестнадцатого элементов И, четвертым входом одиннадцатого элемента И и пятым входом двенадцатого элемента И.

1388879

Составитель В,Бородин

Редактор Е.Копча

Техред А.Кравчук Корректор В. Бутяга

Заказ 1381/50 Тираж 704 Подписное

ВНИИПй Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,.Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4