Устройство для управления регенерацией информации в динамической памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 синхронизации, преобразователи 2, 6 кодов, блок 3 па.мяти, регистры 4, 7, приоритетные шифраторы 5, 8, адресный мультиплексор 9. В устройстве с увеличением количества адресуемых по внешним обраш,ениям столбцов динамической памяти в течение допустимого периода регенерации сокраш,ается длительность опроса накопителя признаков внешних обрашений, что существенно сокращает время обращения по всем строчным адресам. 1 з.п. ф-лы, 4 ил. (С (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5И 4 б 11 С 11 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTQPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4124260/24-24 (22) 30.06.86 (46) 15.04.88. Бюл. № 14 (71) Львовский политехнический институт им. Ленинского комсомола (72) П. А. Кондратов, О. К. Мешков и И. Б. Боженко (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР № 809363, кл. G ll С 11/00, 1979.

Авторское свидетельство СССР № 1251183, кл. G 11 С 21/00, 1985.

„,SU „1388945 А1 (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ

РЕГЕНЕРАЦИЕЙ ИНФОРМАЦИИ В ДИНАМИЧЕСКОЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти. Цель изобретения — повышение быстродействия у стройства. Устройство содержит блок 1 синхронизации, преобразователи 2, 6 кодов, блок 3 памяти, регистры 4, 7, приоритетные шифраторы 5, 8, адресный мультиплексор 9. В устройстве с увеличением количества адресуемых по внешним обращениям столбцов динамической памяти в течение допустимого периода регенерации сокращается длительность опроса накопителя признаков внешних обращений, что существенно сокращает время обращения по всем строчным адресам. 1 з.п. ф-лы, 4 ил.

388945

1

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти.

Цель изобретения -- повышение быстродействия устройства.

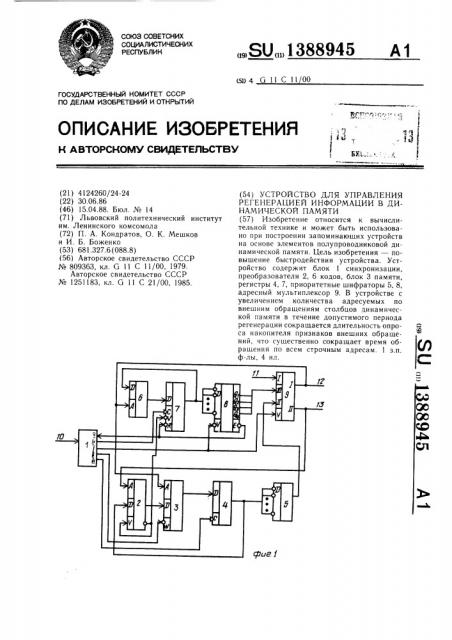

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 — функциональная схема преобразователя кодов адреса; на фиг. 3 и 4— временные диаграммы работы устройства в режимах внешнего обращения и регенерации соответственно.

Устройство содержит (фиг. 1) блок 1 синхронизации, первый преобразователь 2 кодов адреса, блок 3 памяти, первые регистр 4 и приоритетный шифратор 5, вторые преобразователь 6, регистр 7 и шифратор 8, а также адресный мультиплексор 9, управляющий 10 и адресный 11 входы устройства и информационные выхсды 12 и 13 устройства.

Преобразователь 2 кодов адреса (фиг. 2) содержит дешифратор 14, элементы ИЛИ 15, И 16 и элемент И-HE 17. Входы дешифратора 14 являются адресными входами преобразователя, вторые входы элементов ИЛИ

15 — адресными входами, вторые входы элементов И 16 — управляющий вход преобразователя. Выходы элементов И 16 являются информационным выходом преобразователя, выход элемента И-НЕ является выходом запроса преобразователя. Выходы дешифратора 14 соединены с первыми входами элементов ИЛИ 15, выходы которых соединены с первыми входами элементов И и входами элементов И-НЕ, На фиг. 3 и 4 обозначены: а — г — выходы блока 1 синхронизации; д — е — младшие разряды соответственно выходов 12 и 13 устройства; ж — и — соответственно выходы первого, второго и восьмого разрядов дешифратора 14 преобразователя 2; к — м — соответственно выходы первого, второго и восьмого разрядов блока 3 памяти; н — п — выходы первого, второго и восьмого разрядов первого регистра 4; р — выход запроса преобразователя 2; с — т — зыходы первого и шестнадцатого разрядов второго регистра 7; у — выход запроса второго приоритетного шифратора 8.

По входу 10 поступают сигналы запроса внешнего обращения, гактирования, начала и конца регенерации, rro входу 1 — строчные адреса внешнего обращения. С выходов 12 задаются старшие разряды строчных адресов динамической памяти, с выходов

13 — младшие.

Устройство реализовано для управления адресацией динамической памяти, в которой для регенерации опрашиваются 128 столбцов по семи разрядам строчных адресов. В качестве AR- приняты разряды AR 7 — 4, в качестве AR..— АКЗ вЂ” 1. Первый преобразова5

I0

55 тель 2 реализован как преобразователь трехразрядного двоичного в восьмиразрядный позиционный код, блок 3 памяти — как матрица 8х16, первый приоритетный шифратор — как преобразователь восьмиразрядного позиционного в трехразрядный двоичный код, вторые преобразователь 6 и шифратор 8 — соответственно как преобразователи 4 — 16 и 16 — 4.

Устройство работает следующим образом.

Режим внешнего обращения задается уровнем «1» с выхода блока 1 синхронизации (фиг. 3a) . Строчные адреса (фиг. Зд, е) поступают синхронно с сигналами с выхода 1У блока 1 (фиг. Зг) .

Адресный мультиплексор 9 подключает к выходам 12 устройства сигналы AR-, к выходам 13 — - AR, поступающие по адресному входу 11. По АК- из обнуленного в течение цикла регенерации блока 3 памяти выбирается байт, заносящийся по сигналу с выхода 111 блока 1 (фиг. Зв) в первый регистр 4 (фиг. Зн — n). По AR- дешифратор 14 первого преобразователя 2 кодов адреса формирует признак внешнего обращения с уровнем «1», соответствующий этому АК.; (фиг. Зж — и). Затем он складывается по

ИЛИ с предыдущими признаками внешнего обращения по данному ARc зафиксированными в регистре 4, после чего информация с выхода преобразователя 2 по сигналу записи с выхода Il блока 1 (фиг. Зб) записывается в блок 3 памяти (фиг. Зк — м).

После этого по следующему АК- из блока 3 памяти выбирается следующий байт. Так обнуленные за цикл регенерации ячейки блока 3 памяти устанавливаются в «1» по строчным адресам внешних обращений.

В случае, когда внешняя выборка происходит по всем AR ., соответствующим данному АК ., то при выборке из блока 3 памяти байта при подаче последнего из этих адресов, записи в регистр 4, сложении его содержимого с последним признаком выборки все выходы элементов ИЛИ 15 блока 2 устанавливаются в состояние «1». По ним блок 2 вырабатывает сигнал запроса уровня

«0» (фиг. Зр), по которому информационные выходы блока 2 устанавливаются в состояние «О», и это записывается в блок 3 памяти. По этому же запросу синхросигналом с выхода 1У блока 1 (фиг. Зг) во второй регистр 7 заносится признак внешнего обращения по АК- (фиг. 3c — т), который сформирован вторым преобразователем 6 кодов адреса. При поступлении следующего адреса сигнал запроса сбрасывается. Так, при обращении по всем АК., соответствующим данному AR--, во всех разрядах байта, хранящегося в блоке 3 по адресу АК-, устанавливаются «О», а во втором регистре 7— признак внешнего обращения в разряде, соответствующем этому АК-.

Если внешнее обращение ведется по всем строчным адресам AR 1 — 7, все разряды ре1388945

4 ращения по АК. в блоке 2 памяти и по

АК- в регистре 7 оказываются сброшенными.

Формула изобретения

3 гистра 7 устанавливаются в «1» и все байты блока 3 памяти оказываются обнуленными

В этом случае при переводе устройства в режим регенерации второй приоритетный шифратор 8 выдает сигнал запроса (фиг. Зу), по которому регистр 7 сбрасывается, и устройство вновь становится готовым к работе в режиме внешнего обмена.

В режиме регенерации адресный мультиплексор подключает к выходам 12 устройства выходы второго приоритетного шифратора 8, к выходам 13 — выходы первого шифратора 5. АК- определяются по отсутствию признаков внешнего обращения во втором регистре 7, АК . — по отсутствию признаков внешнего обращения в регистре 4.

Шифратор 8 формирует код AR-, соответствующий первому из «О» на выходах регистра 7. По нему из блока 3 памяти выбирается информационный байт и записывается в регистр 4. Шифратор 5 формирует код AR.-, соответствующий первому из «0» на выходах регистра 4. Преобразователь 2 устанавливает «1» в разряде, соответствующем этому AR, и складывает его с содержимым регистра 4. Эта информация по сигналу с выхода 11 блока 1 (фиг. 4б) записывается в блок 3 памяти (фиг. 4к — м) и по синхросигналу с выхода 111 блока 1 (фиг. 4в) перезаписывается в регистр 4 (фиг. 4н n).

Тем самым первый из «О» на входах шифратора 5 сбрасывается, а на его выходах устанавливается AR ., соответствующий следующему «О». Процесс продолжается до выставления на выходе шифратора 5 кода

AR.. соответствующего последнему «0» на выходах регистра 4. При сложении по ИЛИ в преобразователе 2 кода, соответствующего этому AR ., и содержимого регистра 4 выход запроса преобразователя 2 (фиг. 4р) устанавливается в «О». Информация на выходе преобразователя 2 сбрасывается, и по сигналу записи с выхода II блока 1 в блок памяти по данному АК- записывается нулевой байт. Затем при наличии сигнала запроса преобразователя 2 по синхросигналу с выхода IУ блока 1 (фиг. 4г) во второй регистр 7 заносится код, оразованный во втором преобразователе 6 сложением по ИЛИ содержимого регистра 7 с преобразованным в позиционный кодом АК ° (фиг. 4с — т). В результате первый из «0» на входах приоритетного шифратора сбрасывается, и на его выходах устанавливается AR:., соответствующий следующему «О» на выходах регистра 7, Процесс продолжается до исчезновения последнего из «О» на выходах регистра 7, после чего шифратор 8 выдает сигнал запроса (фиг. 4у). По нему регистр 7 сбрасывается, и выдается сигнал окончания регенерации. Тем самым в процессе регенерации адресуются только те столбцы динамической памяти, которые не адресовались в предыдущем цикле внешнего обращения, а в конце регенерации все признаки внешнего об20

Таким образом, в устройстве с увеличением количества адресуемых по внешним обращениям столбцов динамической памяти в течение допустимого периода регенерации сокращается длительность опроса накопителя признаков внешних обращений, что существенно сокращает время занятости регенерацией. В преде.пьном случае, при внешних обращениях по всем строчным адресам, быстродействие предлагаемого устройства дпя рассматриваемого варианта повышается по сравнению с прототипом в 16 раз по числу кодов адресов АК-.

1. Устройство для управления регенерацией информации в динамической памяти, содержащее адресный мультиплексор, блок памяти, первые преобразователь кодов адреса, регистр, приоритетный шифратор и блок синхронизации, первый вход которого является входом запроса внешнего обращения устройства, первый выход блока синхронизации подключен,к управляющему входу адресного мультиплексора, второй выход блока синхронизации подключен к входу записи блока памяти, третий выход блока синхронизации подключен к синхровходу первого регистра, информационные входы которого подключены к выходам блока памяти, выходы первого регистра соединены с входами первого приоритетного шифратора и информационными входами первого преобразователя кодов адреса, информационные выходы которого подключены к информационным входам блока памяти, адресный вход которого подключен к первому выходу адресного мультиплексора и является первым информационным выходом устройства, адресный вход первого преобразователя кодов адреса подключен к второму выходу адресного мультиплексора и является вторым информационным входом устройства, первый адресный вход адресного мультиплексора является адресным входом устройства, второй адресный вход адресного мультиплексора подключен к выходу первого приоритетного шифратора, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй преобразователь кода адреса, второй регистр и второй приоритетный шифратор, информационные выходы которого подключены к информационным входам адресного мультиплексора, выход запроса второго приоритетного шифратора подключен к входу сброса второго регистра и входу задания режима блока синхронизации, информационные входы второго приоритетного шифратора соединены с выходами второго регистра и информационными входами второго преобразователя ко1388945

Фиг. Р с т

У дов адреса, адресные вхсды которого подключены к первым выходам адресного мультиплексора, выход второго преобразователя кодов адреса соединен с информационными входами второго регистра, синхровход которого подключен к четвертому выходу блока сйнхронизации, вход разрешения записи второго регистра соединен с выходом запроса и управляющим входом первого преобразователя кодов адреса.

2. Устройство по и. 1, отличаюш,ееся тем, что преобразователь кодов адреса содержит элементы И-НЕ, ИЛИ, И и дешифратор, выходы которого подключены к первым входам а

8 г д е

U и м н а и

6 элементов ИЛИ, выходы которых соединены с первыми входами элементов И, выходы которых являются информационными выходами преобразователя кодов адреса, входы дешифратора являются информационными

5 входами преобразователя кодов адреса, адресными входами которого являются вторые входы элементов ИЛИ, вторые входы элементов И объединены и являются управляющим входом преобразователя кодов адреса, входы элемента И-НЕ соединены с выходами элементов ИЛИ, выход элемента И-НЕ является выходом запроса преобразователя кодов адреса.

l388945

Составитель С. Шустенко

Редактор А. Лежнина Техред И. Верес Корректор А. Зимокосов

Заказ 525/54 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород. ул. Проектная, 4