Аналоговое устройство для выборки и хранения информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области аналоговых вычислительных и моделирующих устройств и может быть использовано для построения блоков слежения-хранения и интеграторов . Цель изобретения - повышение быстродействия аналогового устройства для выборки и хранения информации. Поставленная цель достигается за счет введения инвертора 5, разделительного конденсатора 6, управляющего ключа 7, компенсирующего резистора 8, обеспечивающих компенсацию постоянной времени слежения. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК g 4 G ll С 27 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4119094/24-24 (22) 16.09.86 (46) 15.04.88. Бюл. № 14 (71) Институт проблем управления автоматики и телемеханики (72) В. П. Морозов (53) 681.327.6 (088.8) (56) Бахтиаров Г. Д. и др. Аналоговые цифровые преобразователи. М.: Советское радио, 1980, с. 152, рис. 629.

Корн Г. и Корн Т. Электронные аналоговые и аналого-цифровые вычислительные машины. Т. 2, М.: Мир, 1968, с. 56, рис. 10.8б.

ÄÄSUÄÄ 1388954 A 1 (54) АНАЛОГОВОЕ УСТРОЙСТВО ДЛЯ

ВЫБОРКИ И ХРАНЕНИЯ ИНФОРМАЦИИ (57) Изобретение относится к области аналоговых вычислительных и моделирующих устройств и может быть использовано для построения блоков слежения-хранения и интеграторов. Цель изобретения — повышение быстродействия аналогового устройства для выборки и хранения информации. Поставленная цель достигается за счет введения инвертора 5, разделительного конденсатора 6, управляющего ключа 7, компенсирующего резистора 8, обеспечивающих компенсацию постоянной времени слежения. 1 ил.

1388954

Формула изобретения

Составитель A. Ершова

Редактор Н. Швыдкая Техред И. Верес Корректор М. Демчик

Заказ 525/54 Тираж 590 Подписное

ВНИИПИ Государственного комитета CC(:Р по делам изобретений и открытий

I l 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Изобретение QTHocHTcsII к аналоговым вЫчислительным и моделирующим устройствам, в частности к интеграторам и блокам слежения-хранения аналоговых устройств.

Цель изобретения — повышение быстродействия устройства.

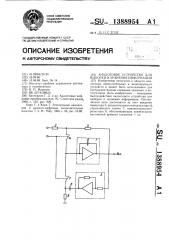

На чертеже представлено устройство.

Устройство содержит интегратор 1 тока, резисторы 2, 3 токозадающий и обратной связи, первый управляющий ключ 4, инвертор 5, разделительный конденсатор 6, второй управляющий ключ 7, компенсирующий резистор 8, накопительный конденсатор 9, Устройство работает следующим образом.

При подаче логического сигнала (единичного или нулевого в зависимости от типа элементной базы) на управляющие входы ключей 4, 7 последние замыкаются и устройство переходит в режим выборки. При этом 20 на входе интегратора 1 суммируются токи, поступающие с выхода устройства через конденсатор 9 и резистор 3 с током через резистор 2. Резисторы 2 и 3 выбираются одинаковыми.

Сюда же поступает ток через ключ 7 и конденсатор 6 с выхода инвертора 5. В устройстве скорость слежения определяется постоянной времени т=КС, где C=C — С, R-сопротивление резисторов 2 и 3, С-емкость конденсатора 9; Ci-емкость конденсатора 6.

В режиме хранения ключи 4, 7 разомкнуты, а конденсатор 6 разряжается через резистор 8, что уменьшает утечку тока через ключ 7.

Аналоговое устройство для выборки и хранения информации, содержащее токозадающий и обратной связи резисторы, интегратор, управляющий ключ, причем первый вывод токозадающего резистора подключен к информационному входу устройства, вход интегратора и вторые выводы токозадающего и обратной связи резисторов подключены к первому управляющему ключу, первый вывод резистора обратной связи подключен к выходу интегратора и является информационным выходом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены инвертор, разделительный конденсатор, компенсирующий резистор, второй управляющий ключ, вход инвертора подключен к выходу интегратора, выход инвертора подключен к одной обкладке разделительного конденсатора, другая обкладка которого соединена с вторым управляющим ключом, входом инвертора и первым выводом компенсирующего резистора, второй вывод которого подключен к шине нулевого потенциала устройства, первый и второй управляющие ключи объединены и подключены к управляющему входу устройства.