Дельта-модулятор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Его использование в системах преобразования и передачи информации позволяет расширить область применения за счет дополнительного преобразования двухполярного входного сигнала в цифровое произведение этого сигнала на его приращение . Дельта-модулятор содержит генератор 1 тактовых импульсов, компаратор 2, реверсивный счетчик 3, блок 4 управления, -преобразователь 5 код - напряжение, элементы ИЛИ 6 и 13, формирователи 7 и 8 переднего фронта, элемент ЗАПРЕТ 9, элемент И 10, элемент 12 задержки, RST-триггер 11 и D-триггер 14. Введение двухполупериодного выпрямителя 15, источника 16 опорного напряжения и сумматора 17 обеспечивает требуемое преобразование . 3 ил. с «S (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) А1 (51) 4 Н 03 М 3/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

1Ю

1У

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4103358/24"24 (22) 11,08.86 (46) 15.04.88. Бюл. № 14 (71) Специальное конструкторскотехнологическое бюро Физико"механического института АН УССР (72) И. B. Рожанковский, В. А. Погрибной и О, P. Пристайко (53) 621.376.56(088,8) (56) Авторское свидетельство СССР № 661789, кл. Н 03 M 3/02, 1977.

Авторское свидетельство СССР № 1257849, кл. Н 03 M 3/02, 1985. (54) ДЕЛЬТА-МОДУЛЯТОР (57) Изобретение относится к вычислительной технике. Его использование в системах преобразования и передачи информации позволяет расширить область применения за счет дополнительного преобразования двухполярного входного сигнала в цифровое произ" ведение этого сигнала на его приращение. Дельта-модулятор содержит генератор 1 тактовых импульсов, компаратор 2, реверсивный счетчик 3, блок 4 управления, преобразователь 5 код— напряжение, элементы ИЛИ 6 и 13, формирователи 7 и 8 переднего фронта, элемент ЗАПРЕТ 9, элемент И 10 элемент 12 задержки, RST-триггер 11 и

D-триггер 14. Введение двухполупериодного выпрямителя 15, источника 16 опорного напряжения и сумматора 17 обеспечивает требуемое преобразование. 3 ил. (x!

t6) 1 =l х

Ь =0 (х)

К 9 (2 х

Ь(1! = 0 ° с 2) Э

Ь(х1

1к З)

Ь о 1

Зк

t ), Ь(." =

)к („

1; (Т.:

0;

7 °

,) -Ь (x! х

t )"- L. = 0 (x) в Э

1 13889

Изобретение относится к вычислительной технике и может быть использовано в системах преобразования и (ередачи информации.

Цель изобретения - расширение об( дасти применения эа счет дополнительного преобразования двухполярного входного сигнала в цйфровое произведение этого сигнала на его прирап1ения.

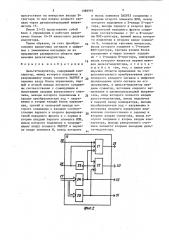

На фиг. 1 приведена блок-схема редлагаемого дельта-модулятора; . а фиг. 2 - функциональная схема лока управления; на фиг. 3 - времен" 16 (е диаграммы сигналов.

Дельта-модулятор содержит генера((ор 1 тактовых импульсов, компара. 1ор 2, реверсивный счетчик 3, блок 4 у1правления, преобразователь 5 кодапряжение, первый элемент ИЛИ 6, ервый и второй формирователи 7 и 8 ереднего фронта, элемент ЗАПРЕТ 9, ( з1лемент И 10. RST-триггер l l, элеент 12 задержки, второй элемент 25 ЛИ 13, Э-триггер 14, двухполупериОдный выпрямитель 15, источник 16 опорного напряжения и сумматор 17.

На фиг. 1 обозначены вход 18, первый и вторые выходы 19 и 20. 30

Блок 4 управления выполнен на первом и втором элементах ЗАПРЕТ 21

22, элементе НЕ 23 элементе ИЛИЕ 24 и элементе И .25, имеет входы

26-28 и выходы 29-32.

Дельта"модулятор работает следую" щим образом.

Входной аналоговый двухполярный сигнал (фиг. За) подается с входа 18 на двухполупериодный выпрямитель 15, которые выделяет абсолютное значение входного сигнала (фиг. Зб) Однополярный сигнал с выхода выпрямителя 15 поступает на первый вход компаратора 2, На второй вход компаратора 2 поступает сигнал обратной связи с выхода сумматора 17. (:умматор 17 производит суммирование выходного сигнала преобразователя 5 код - напряжение, аппроксимирующего входной сигнал (поступающий на первый вход компаратора 2), с выходным иапряжением постоянного тока величи" иой у = - 1, где q — шаг квантова" иия дельта-модулятора (поступающий с, 92 2 выхода источни а 16 опорного напряжения). Это необходимо для получения линейной (равномерной) шкалы кодов на выходе реверсивного счетчика 3 в области нулевых значений входного сигнала устройства.

Блоки 1-14 предлагаемого дельтамодулятора при подаче однополярного аналогового сигнала работают так же, как и блоки 1-14 известного дельта-модулятора fl) на выходе D-триггера 14 которого формируется одноразрядный дельта-код, характеризующий приращение входного сигнала (х! A A . (х! (х! е „ =х „ -х „,, е „ (= ) L K а на выходах реверсивного счетчика

3 - m-р аэр ядный смещенный код, соотв етствующий величине входного сиг нала.

При подаче же на вход компаратора 2 абсолютного значения входного сигнала, поступающего с выхода двухполупериодного выпрямителя 15, на выходах m"ðàçðÿäíîãî реверсивного счетчика 3 формируется прямой код, соответствующий входному сигналу Uq„ (фиг. Зв), а на инверсном выходе Dтриггера 14 - результат, аналогичный перемножению битов знака входного сигнала на символ дельта"кодовой последовательности за счет двухполупериодного выпрямления входного сигнала (фиг. Зг). Так, в интервалах, (х! времени (О; t,), (t„ t ) знак Ь и (х!

1 приращение- L(! (взятое в дискретные к моменты времени, равные периоду дискретизации при дельта-модуляции) входного сигнала П,„ положительны (х! (х!

L = l, L „ = 1, и поэтому р е з уль т ат умножения, аналогично суммированию по модулю два, должен быть также и оложител ен

I (x! (х! (х!

Ь,„= L; SL„= 1O+1 = О.

В интервалах времени (к!

Такой же результат, равный L

1к в соответствующие интервалы времени, 1388992

ЗО присутствует на инверсном выходе Dтриггера 14 при подаче входного сигнала через двухполупериодный выпря- . митель 15.

Блоки 21-25 представляют собой блок 4 управления и работают аналогично блокам 15-19 известного дельтамодулятора.

Таким образом, за счет преобразования аналоговых сигналов в цифровые с умножением последних на их приращения расширяется область применения дельта-модулятора.

Формула изобретения

Дельта-модулятор, содержащий компаратор, выход которого подключен к разрешающему входу элемента ЗАПРЕТ и первому входу блока управления, первый и второй выходы которого соединены соответственно с суммирующим и вычитающим входами реверсивного счет" чика, выходы которого подключены к входам преобразователя код - напряжение и вторым входам блока управления, третий и четвертый выходы которого соединены с входами соответственно первого и второго формирователей переднего фронта и с первым и вторым входами первого элемента ИЛИ, выход которого подключен к запрещающему входу элемента ЗАПРЕТ и первому входу элемента И, выход которого и выход элемента ЗАПРЕТ соединены с входами второго элемента ИЛИ, выход которого подключен к D-входу D-триг" гера, выходы первого и второго формирователей переднего фронта соединены соответственно с (S- и R-входами RST".òðèããåðà, прямой выход которо" го подключен к второму входу элемента И, генератор тактовых импульсов, выход которого соединен с Т-входом

RST-триггера, третьим входом блока управления и через элемент задержки — с С-входом D"òðèãгера, инверсный выход которого является первым выходом дельта-модулятора, о т л и ч а " ю шийся тем, что, с целью расширения области применения за счет дополнительного преобразования двухполярного входного сигнала в цифровое произведение этого сигнала на его приращения, в дельта-модулятор введены сумматор, источник опорного напряжения и двухполупериодный выпрями" тель, вход которого является входом дельта-модулятора, выход подключен к первому входу компаратора, выходы преобразователя код " напряжение и источника опорного напряжения подключены соответственно к первому и второму входам сумматора, выход которого соединен с вторым входом компаратора, выходы реверсивного счет. чика являются вторыми выходами дельта-модулятора. чс

1 388992

Составитель G. Ревинский

Редактор Т, Парфенова Техред J1 ° Îëèéíûê Корректор Л.Патаи

Заказ 1585/56 Тираж 928 Подписное

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

11роизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

1 (1 !

l