Устройство для передачи дискретных сообщений

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи и повышает помехоустойчивость путем адаптации по тестовому сигналу к изменениям импульсного отклика канала. Устр-во содержит на передающей стороне кодер 1, блоки 3, 6 и 8 памяти, вычислитель 7 дискретного преобразования Фурье, ЦАП 9, на приемной стороне .- АЦП 10, временной селектор 11, вычислитель 12, обратного дискретного преобразования, регистр 13, умножитель 14, формирователь 15 разрешенного сигнала, блоки 16 и 22 деления, регистр 17, вычислитель 18 дискретного преобразования Фурье, сумматор 19, умножитель 20, вычислитель 21 обратных дискретных преобразований Фурье, блоки 23 и 24- памяти. 1 ил. (Л С

„„SU„„1389006

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК. (51)4 Н 04 L 17/02, 17/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

P l

t !

РЬЛВ: l (.:."

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1239880 (21) 4147438/24-09 (22) 13.11.86 (46) 15.04.88. Бюл. М 14 (71) Московский электротехнический институт связи (72) Д.P.Àíêóäèíîâ, В.Б.Зоткин, А.И.Кобленц, Д.Л.Коробков и А.Л.Леонидов (53) 621.394.6 (088.8) (56) Авторское свидетельство ССС

К 1239880, кл. Н 04 L 17/02, 1984., (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНЫХ СООБЩЕНИЙ (» ) Изобретение относится к технике связи и повышает помехоустойчивость путем адаптации по тестовому сигналу к изменениям импульсного отклика канала. Устр-во содержит на передающей стороне кодер 1, блоки

3, 6 и 8 памяти, вычислитель 7 дискретного преобразования Фурье, ЦАП 9, на приемной стороне . — АЦП 10, временной селектор 11, вычислитель 12. обратного дискретного преобразования, регистр 13, умножитель 14, формирователь 15 разрешенного сигнала, блоки

16 и 22 деления, регистр 17, вычислитель 18 дискретного преобразования

Фурье, сумматор 19, умножитель 20, вычислитель 21 обратных дискретных преобразований Фурье, блоки 23 и 24 памяти. 1 ил.

1389006

Изобретение относится к технике связи и может использоваться для передачи дискретных сообщений по каналам связи с пакетной передачей и является усовершенствованием изобрете5 ния по авт". св. У 1239880.

Цель изобретения — повышение помехоустойчивости путем адаптации по тестовому сигналу к изменениям импульсного отклика канала.

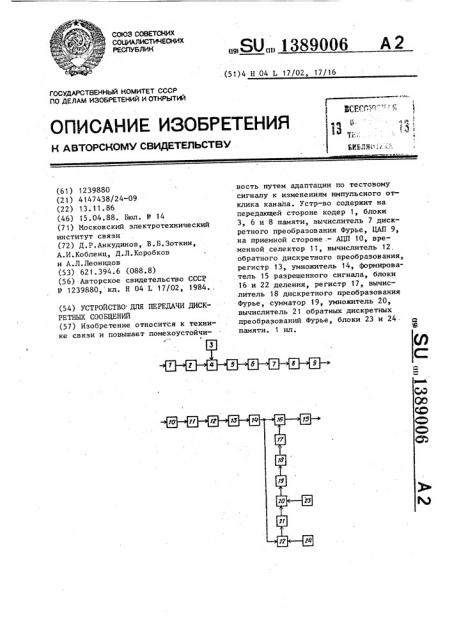

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство для передачи дискретных сообщений содержит на передающей стороне кодер 1, первый блок 2 памяти, четвертый блок 3 памяти, ключ

4 умножитель 5, третий блок 6 памяти, вычислитель 7 дискретных преобразава- 20 ний Фурье, второй блок 8 памяти, цифроаналоговый преобразователь 9, на приемной стороне — аналого-цифровой преобразователь 10, временной селек- . тор 11, вычислитель 12 обратных дис- 25 кретных преобразований Фурье, регистр 13, умнажитель 14, формирователь 15 разрешенного сигнала, второй блок 16 деления, дополнительный регистр 17, вычислитель 18 дискретных преобразований Фурье, сумматор 19, дополнительный умнажитель 20, вычислитель 21 обратных дискретных преобразований Фурье, первый блок 22 де.ления, первый блок 23 памяти, второй блок 24 памяти.

Устройства работает следующим образом.

На тактовый вход (не показан) кодера 1 с генератора (не показан) пас- тупают тактовые импульсы (ТИ), следующие с частотой F„ ïåðåäà÷è информации..Те же ТИ поступают также на тактовые входы (не показаны) блока 2 памяти, четвертого блока 3 памяти, умножителя 5 и на тактовый вход записи (не показан) блока 6 памяти.

Кроме того, с того же генератора поступают следующие ТИ {тактовые входы не показаны): на тактовый вход ключа 4 — ТИ,длительность которых равна N тактов частоты Р,а частота следования

Г = F< /(mN),ãäå N — длина передаваемого блока, m — количество блоков в передаваемом пакете; на тактовый вход считывания блока 6 памяти, на тактовый вход записи блока 8 памяти, на тактовый вход вычислителя 7 дискретных преобразований Фурье — ТИ, следующие с частотой F =F„ M/N, где М

= 2(N+L,), Ь вЂ” длина дискретного импульсного отклика канала (ИОК) на тактовый вход цифроаналогового преобразователя 9 и на тактовый вход считывания блока 8 памяти — ТИ, следующие с частотой F< =F (N+L )/N.Äèñêретные сообщения, поступающие на вход кодера 1 амплитудна-фазовой модуляции, преобразуются в нем в последовательность цифровых сигналов x,. i=

=О,N-1. С. выхода кодера 1.эта последовательность поступает на вход блока 2 памяти. Запись и считывание в блоке 2 памяти происходит с частотой

Г,. В четвертом блоке 3 памяти заранее записана последовательность тестовых сигналов х р 1=0 И 1р из вестная на приеме. В зависимости от состояния ключа 4 на вход умножителя 5 поступает либо последователь.о ность цифровых сигналов х;, i=O N-1 либо тестовый блок х; е„, 1=0,0-1, последовательность ТИ частоты F обеспечивает пропускание на выход ключа 4 тестового блока только в те" чение М тактов частоты F в начале каждого передаваемого пакета (состоящего из m блоков,,m i). Выбор параметра.ш = 2,3,... должен осуществляться, исходя из разумного компромисса между разумными потерями в скорости передачи информации (при малых значениях m) и снижением помехоустойчивости из-за ухудшения оценивания канала (при слищком больших значениях m), В умножителе 5 производится предыскажение путем умножения компонент сигнала х;, i=0 N-1 на коэффициент предыскажения С, =О,N-1.:Поступающий с выхода умножителя 5 предыскаженный сигнал z.=

= х; С;, i = O,И-1 записывается счастатай F, в блок 6 памяти. Считывание информации из второго блока 6 памяти происходит с частотой F . На выходе блока 6 памяти формируется блок Е;, = О,M-1 цифровых сигналов:

О, i=0 х„,, 1=1 N

0 1=И+1 р ,„э э

Z „ i=P+1 М-1, Z где P = M/2.

Здесь и далее символ + означает комплексное сопряжение. Последовательность Е;, i=O М-1 компонент сигнала поступает на вход вычислителя 7

1389006 . дискретных преобразований Фурье, на выходе которого формируется последовательность . %

Z = —,Е.Е е

1Р1

И

t p

n=0 M-1.

Тактовая частота работы вычисюп теля 7 дискретных преобразований

Фурье равна Fq Последовательность

Е„ с частотой Fq поступает на вход третьего блока 8 памяти, на выходе которого формируется блок Т;, = 0,Ì+!ð-1 путем дополнения блока

Е„, п=О,М-1 своими последними Lo ком-15 понентами так, что

t М О р

Lo р i=L o M+Lo (2) Т. =

Сформированный блок Т;, =0;М+Ь -1 с частотой Рф поступает на вход цифроаналогового преобразователя 9, с выхода которого аналоговый сигнал 25 поступает в канал связи.

Аналогичные преобразования осуществляются и в случае поступления с выхода ключа 4 тестового блока

Жй Фрсу = 0 N 1 °

На приемной стороне на тактовый вход (не показан) аналого-цифрового преобразователя 10 с генератора (не показан) поступают ТИ частоты Р . Те же ТИ поступают также на тактовый вход записи (не показан) временного селектора 11. Кроме того, с того же генератора поступают следующие ТИ (тактовые входы не показаны): на тактовые входы считывания временного селектора 11 и вычислителя 21 обратных дискретных преобразований

Фурье, на тактовый вход записи регистра 13, на тактовые входы вычислителя 18 дискретных преобразований

Фурье, сумматора 19, дополнительного умножителя 20, блока 23 памяти, A вычислителя 12 обратных дискретных преобразований Фурье — ТИ частоты Р, на тактовые входы считывания регистра 13 и дополнительного регистра 17, на тактовые входы записи блока 16 деления и вычислителя 21 обратных дискретных преобразований Фурье, на тактовйе входы умножителя 14, блока 22 деления, блока 24 памяти — ТИ частоты F

, тактовый вход записи дополнительного регистра 17 — последовательность ТИ частоты F представляющая собой логическое произведение последовательности ТИ частоты Р г и последовательности ТИ частоты Р .

Аналоговый сигнал поступает из канала связи на вход аналого-цифрового преобразователя 10, в котором сигнал преобразуется в цифровую форму. Затем цифровой сигнал поступает на временной селектор 11, который выделяет а последовательность Z» =О,М-1 поступающую на вход вычислителя 12 обратных дискретных преобразований е

Фурье, на выходе которого формируется последовательность

М-1 т .

1 -1 — lh У

Е;= — ЕZ„e, i=O,Ì-1 (3) И h=O которая записывается в регистр 13, с выхода которого считывается Последовательность Z;, i=O,Ð, поступающая на вход умножителя 14, в котором производится коррекция элементов последовательности Z- i=0 Р, путем умножения на коэффициенты g.ÀÑ,, i

= О,Р, в результате чего на выходе умножителя 14 формируется последовательность х,.=g. Z„, iW Р, поступающая одновременно на вторые входы блоков 1б,и 22 деления..

Аналогичные преобразования осуществляются и в случае поступления на вход аналого-цифрового преобразователя 10 тестового сигнала. В этом случае с выхода умножителя 12 наблюдения х,. „,, i=0 Ð поступают на второй вход блока 22 деления, в котором производится позлементное деление этой последовательности на тестовую последовательность х;„,, =О,Р, поступающую на первый вход блока 22 деления из блока 24 памяти, и на его выходе сигнал имеет вид

К,.=, i = О,Р (4)

Э 1тЕСУ

Последовательность К;, х=О,Р поступает на вход вычислителя 21 .обратных дискретньп преобразований Фурье, в котором производится р =М/L (р —целое) обратных L — точечных ДПФ пс, а следоаателеностей К„Н п=ОаL -1, 8=0,ð-1, причем для i=P+1,М-1,К;=К„,;.

С выхода вычислителя 21 обратных ди89006

l довательности х, i=O,Ð на коэффициенты К,, i = О,Р, представляющие собой оценки коэффициентов передачи, вычисленные при обработке тестового блока информации. С выхода блока 16 деления блок

ГДЕ "{7

В = I х„..., В=0,„-1 {7) На выходе дополнительного умножителя 20 формируются произведения

Формула изобретения л (57 - {g)

h g ={Взй g, S=O,u — 1, g=OòLо 1. (8) л {

Последовательности h с выхода

1 умножителя 20 поступают на вход сумматора 19,,с выхода которого последовательность,{4- 1 с; — { h, g-0 -1

S =O

О, g=L,,N-l л

Ф (9) Составитель Н.Лазарева

Редактор З.Слиган Техред Л.Олийнык Корректор Н. Король

Заказ 1586/57 Тираж 660

Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно"полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 скретных преобразований Фурье последовательности ь -1 + — з

{7- {7

g=,ОL 1, S =0p-1 (5) поступают на первый вход дополнительного умножителя 20, на второй вход которого из блока 23 памяти поступает заранее записанная в него последовательность

lu-1

И, =(В,, » В, ), S=O,p-1, (6) =о поступает на вход вычислителя 18 дискретных преобразований Фурье, с выхода которого оценки

М-1 . 2{{ л - — ф

К.= †.. h е < i=0 Ð (10)

% = коэффициентов передачи поступают на вход дополнительного регистра 17,запись в который происходит с частотой

F . Тем самым обеспечивается запись и хранение в регистре 17 только тех л оценок К,, которые получены в результате передачи и приема тестового блол ка. С выхода регистра 17 оценки К., 1

О, P по с тупают н а пе рвый вход блока 16 деления, в котором производится деление каждого элемента послеrt

УМ К;

Z =, i=0 Ð (11)

10 с частотой F поступает на вход формирователя 13 разрешенного сигнала, состоящего из последовательно соединенных решающего устройства и декодера амплитудно-фазовой модуляции, в котором формируется последоватЕльность дискретных сообщений, поступающая на выход устройства.

Устройство для передачи дискретных сообщений по авт. св. У 1239880, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости путем адаптации по тестовому сигналу к изменениям импульсного отклика канала, на передающей стороне введены последовательно соединенные четвертый блок памяти и ключ, причем выход первого блока памяти соединен с входом умножителя через ключ, на приемной стороне введены первый блок памяти, а также последовательно соединенные второй блок памяти, первый блок деления, вычислитель обратных дискретных преобразований Фурье,дополнительный умножитель, сумматор, вычислитель дискретного преобразования Фурье, дополнительный регистр и второй блок деления, причем выход умножителя соединен с входом формирователя разрешенного сигнала через второй блок деления, выход первого блока памяти соединен,с вторым входом дополнительного умножителя, а выход умножителя соединен с вторым входом первого блока деления.