Устройство для разделения направлений передачи в дуплексных системах связи

Иллюстрации

Показать всеРеферат

Изобретение относится к передаче данных. Цель изобретения - повышение пропускной способности. Уст-во содержит согласующий блок 1, коммутатор 2, ЦАП 3 и 11, АЦП 4, формирова

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) (111 (g1) 4 Н 04 В 1/52, Н 04 L 27/18

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОЬГКт НИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ Ц

gg„„„.. (54) устРОЙстБО для РАзделения нАПРАВЛЕ11ИЙ ПЕРЕДАЧИ Н ДУП11ЕКСНЫХ СИСТЕ1АХ СВЯЗИ (21) 4130216/24-09 (22) 01. 10. 86 (46) 23.04,88, Бюл. Р 15 (71) Новосибирский электротехнический институт связи им. Н.Д. Псурцева (72) В.В. Лебедянцев и В.Б. Иалинкин (53) 621.393.3(088.8) (56) Авторское свидетельство СССР

В 1133675, кл. EE 04 В 1/52, 1983. (57) Изобретение относится к передаче данных. Цель изобретения — повышение пропускной способности. Уст-во содержит согласующий блок 1, коммутатор 2, ЦАП 3 и 11, АЦП 4, формирова1390803 тель адреса (фА) 5, блоки 6, 10 памяти, генератор 7, блок 8 вычитания, сум-- матор 9. Введены блоки 12 и 13 памяти, делитель 14, триггер 15, блок 16 вычитания, счетчик 17, пороговый блок

18. ФА 5 имеет блок памяти, постоянный запоминающий блок, сумматор и пороговый блок. После подключения к каналу связи производится кратковременное принудительное обнуление всех узлов, Начинается рабочий цикл, к-рый можно расчленить на три одновременно происходящих процесса: 1) постоянное формирование и корректировка оценок

Изобретение относится к области передачи данных и может найти применение в дуплексных системах связи.

Цель изобретения — повьппение пропускной способности.

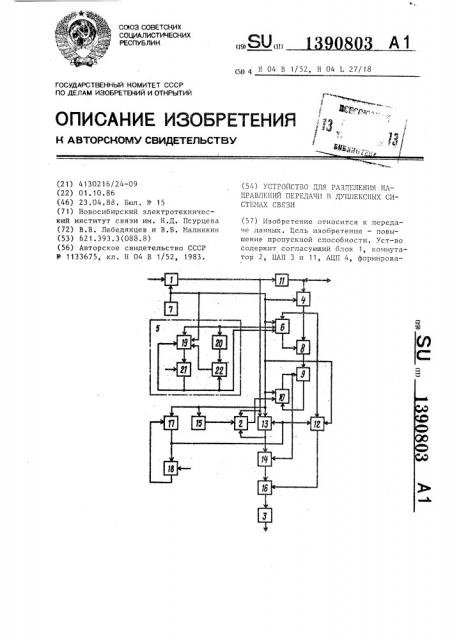

На чертеже изображена структурноэлектрическая схема устройства.

Устройство содержит входной согласующий блок 1, коммутатор 2, первый цифроаналоговый преобразователь 3, аналого-цифровой преобразователь 4, формирователь 5 адреса, первый блок 6 памяти, генератор 7, первый блок

8 вычитания, сумматор 9, второй блок

10 памяти„ второй цифроаналоговый преобразователь 11, третий блок 12 памяти, четвертый блок 13 памяти, делитель 14 триггер 15, второй блок

16 вычитания, счетчик 17 и пороговый блок 18, причем формирователь 5 адреса содержит б.пок 19 памяти, посто янный запоминающий блок 20, сумматор

21 и пороговый блок 22.

Устройство работает следующим образом.

После подключения к каналу связи по сигналу, поступающему от оконечного оборудования данных, производится кратковременное принудительное об- ЗО нуление всех узлов устройства. После этого начинается рабочий цикл работы устройства. В этом режиме работу устройства можно расчленить на три одновременно происходящих процесса. 35 отсчетов передав аемьг< сигналов (задействованы блоки 6 и 10, блок 8,сумматор 9 и ФА 5), 2) запоминание отсчетов передаваемых сигналов и суммы отсчетов передаваемых и принимаемых сигналов, поступающих во время первоначального фОрмирования оценок отсчетов передаваемого сигнала (задействованы блоки 1? и 13, счетчик 17 и блок

18), 3) компенсация отсчетов переда- ваемых сигналов в принимаемом суммарном сигнале (задействованы блок 16, блок 12, делитель 14. Устр-во явля- ется адаптивным). 1 з.п. ф-лы, 1 ил.

Первый процесс заключается в постоянном формировании и корректировке оценок отсчетов передаваемых сигналов. Он осуществляется с помощью первого 6 и второго 10 блоков памяти, первого блока 8 вычитания, сумматора

9 и формирователя 5 адреса.

Второй процесс заключается в запоминании отсчетов передаваемых сиг-« налов и суммы отсчетов передаваемых и принимаемых сигналов, поступающих иэ канала связи во время первоначального формирования оценок отсчетов передаваемого сигнала. Он осуществляется с помощью третьего 12 и четвертого 13 блоков памяти, счетчика

17 и порогового блока 18.

Третий процесс заключается в компенсации отсчетов передаваемых сигналов в принимаемом суммарном сигнале.

Компенсация передаваемых сигналов осуществляется путем вычитания во втором блоке 16 вычитания из отсчетов суммы передаваемого и принимаемого сигналов, выводимого из соответствующей ячейки памяти третьего блока 12 памяти, оценки соответствующего уровня отсчета сигнала передатчика, снимаемой с выхода делителя 14.

Суть первого процесса — процесса формирования оценки передаваемых сигналов заключается в следующем.

Пусть на вход входного согласующего блока 1 поступает некоторый информационный процесс n (t), подлежа1390803 щий передаче. Из канала связи приходит сигнал у (c), который следует отделить от сигнала и (t). Сигнал n (t), пройдя входной согласующий блок i, дискретизируется по уровню и во времени. При этом каждый уровень отображается соответствующей двоичной комбинацией п;(к

Ф п (t). Сумма сигналов и (t) и у (t) (где у (t) — принимаемый сигнал) поступает на вход аналого-цифрового преобразователя 4, в котором она дис-20 кретизируется и превращается в сигнал х (kit) = n (kit) + у (kit) . После этого сигнал х (kac) поступает на второй вход первого блока 8 вычитания и на вход первого блока 6 па-25 мяти. Первый блок 6 памяти выполнен секционированным, причем количество секций равно количеству двоичных комбинаций и;(kit), отображающих передаваемый сигнал n (t).

Таким образом, если входной согласующий блок l выполнен к-разрядным, то число возможных комбинаций n<(kit) при к = 8 равно 256 (2 =256). Следов вательно, в данном случае первый блок

6 памяти содержит 256 секций. 35

При этом в каждую секцию первого блока 6 памяти записывается соответствующая номеру данной секции величина отсчета передаваемого сигнала

n (t). К примеру, пусть в первый мо40 мент на вход входного согласующего блока поступает сигнал n (t), который превращается входным согласую- щим блоком 1 в комбинацию и, (k<3 t)=

128„ = 10000000в . Здесь подстрочные индексы обозначают основание системы счисления.

Сигнал и, (k, в t) превращается в и (tÄ ) во втором цифроаналоговом пре- 0 образователе 11, складывается с сигналом, поступающим в данный момент из канала связи у (t ), превращается в сигнал х (k< at) = n, (k<«t) + y< (k<8 t) в аналого-цифровом преобразователе

4,и записывается в 128-ю секцию пер55 вого блока 6 памяти. Причем каждая секция первого блока 6 памяти имеет длину К k-разрядных ячеек, где М; коэффициент усреднения i-ro передаваемого уровня. Величина И; рассчитывается заранее, исходя из требуемого качества фсрмирования оценки отсчетов передаваемых сигналов по формуле (4),и записывается в постоянном запоминающем блоке 20 до начала сеанса связи. Формирователь 5 адреса формирует адреса в каждой секции первого бло ка 6 памяти, начиная с первого и кончая И;, тем самым обеспечивая работу первого блока 6 памяти, выполненного на оперативном запоминающем устройстве с произвольной выборкой в режиме регистрового запоминающего устройства °

Таким образом, если на выходе входного согласующего блока 1 появляются

М; раэ двоичные комбинации n;(k gt), равные по величине, то отклики канаФ ла связи на данные цифровые комбинации фиксируются в i-й секции первого блока 6 памяти по адресам, начиная с первого и кончая И;.

Формирователь 5 адреса обеспечивает адресацию, начиная с единичной до N>,â каждой секции первого, блока .6 памяти. Это производится следующим образом. Пусть в первый момент на вы-. ходе входного согласующего блока 1

<<оявляется двоичная комбинация, равная

n z< (,д t) =128, = 10000000 . Данная двоичная комбинация указывает в блоке

19 памяти ячейку памяти с адресом, равным 128 <>. Так как в первый момент времени блок l9 памяти обнулен, то на выходе последнего по адресу 128< выводится нуль. Данный нуль в сумматоре 21 складывается с логической единицей, поступающей на его второй вход. Результат суммирования, равный единице, указывает в первом блоке 6 памяти первую ячейку памяти в 128-й секции, откуда вначале считывается прежнее содержимое (т.е., нуль), а затем записывается значение x(k Ь t)= Ъ <

= п< в (k,g t) + у, (k< pc) . Логическая единица с выхода сумматора 21 затем сравнивается со значением М<„., которое выводится иэ постоянного запоминающего блока 20 в пороговом блоке 22.

В случае, если содержимое данной (128-й)ячейки памяти блока 19 памяти меньше значения М,, выводимого иэ постоянного запоминающего блока 20, то на выходе порогового блока 22 появляется логический нуль. Если содержимое 128-й ячейки памяти блока 19

1390803 памяти станет равным или превысит значение М,2<, то на выходе порогового блока 22 появляется логическая единица и блок 19 памяти по адресу

128 обнуляется. Кроме того, результат суммирования — логическая единица с выхода сумматора 21 затем записывается в 128-ю ячейку памяти блока 19 памяти и хранится до тех пор, пока1O на выходе входного согласующего блока 1 не появляется вновь двоичная цифровая комбинация, равная и, (1с ьг.)=

1 00000002 1 28ð Если данная цифровая комбинация вновь появляется на выходе входного согласующего блока 1, то из 128-й ячейки памяти блока 19 памяти выводится прежнее содержимое (т,е., единица), которая складывается в сумматоре 21 вновь с единицей. Результат суммирования, равный двум, вновь записывается по

128-му адресу в блок 19 памяти, указывает вторую ячейку в 128-ю секцию первого блока 6 памяти и сравнивается вновь с М< в пороговом блоке 22 и т.д. Пусть М,2 =63. Тогда, после псредачи 62 раз величины М, д (k t) на выходе сумматора 21 появляется число, разное 63 (62+1), которое указывает вновь в ервом блоке 6 памя ти 63-ю ячейку памяти в 128-й секции, откуда сначала считывается нуль, а затем записывается значение п (1 Ь t)+

+уб, (k ь t) . На выходе порогового

6 2 блока 22 появляется логическая еди- 35 ница, которая обнуляет 128-ю ячейку памяти блока 19 памяти. После передачи 63 раза значения и 2 (1с,Ь Г) процесс повторяется, из первой ячейки памяти 128-й секции первого блока 6 памяти сначала считывается ее содержимое, т.е. n

+У 3 (К63 Ь 1) И Т Д 5

Таким образом, формирователь 5 адреса в сочетании с первым блоком 6 памяти производит задержку и хранение отсчетов передаваемых и принимаемых отсчетов сигналов. Одновременно

50 сумматор 9 совместно с вторым блоком

10 памяти производит накопление отсчетов передаваемых и принимаемых отсчетов сигналов. Работой второго блока 10 памяти управляет триггер 15 совместно с коммутатором 2. Цикл ра55 боты расчета оценок передаваемых сигналов разбит на два интервала. На первом интервале триггер 15 находится в нулевом состоянии, тем самым выход входного согласующего блока 1 оказывается подключенным через коммутатор 2 к адресным входам второго блока 10 памяти. При появлении двоичного числа (к примеру 128) на выходе входного согласующего блока 1 во втором блоке 10 памяти указывается 128ячейка памяти. Так как в первый момент времени последний был обнулен, то при поступлении с выхода аналогоцифрового преобразователя 4 первого значения отсчетов суммарного передаваемого и принимаемого сигналов, равного и (k Ь t) + y (!c Ьt) КОТОрыи

1 1 проходит через первый блок 8 вычитания на вход сумматора 9, результат

\ суюлирования, равный n, (k, Ь t) + 2В

+ y„(lc, ь t), з аписыв ает ся в 1 28-ю ячейку памяти второго блока 10 памяти. После второго цикла работы во втором блоке 10 памяти будет величина, равная; ni2Â (k 5 t) + yi (1c< A t) 4+ nÄ z (kzAt) + у (1с дГ) и т д.

После передачи Mi23 раз величины и» (k ь ) (М, „=63 в данном случае) йолучим:

s3 Я3

Р(х) = и, ° (1с;ь )+,y; (lc,ь t) (1)

1 г=

При передаче случайного текста цифровые комбинации n;(k;ьг) на выходе входного согласующего блока 1 появляются случайным образом, независимо друг от друга. Позтому отсчеты принимаемого сигнала у„ (k,ьг-) будут случайным образом распределены в первом блоке 6 памяти. Таким образом, можно считать, что отсчеты у;(k;ь t) характеризуются независимостью как между собой, так и между отсчетами сигнала передатчика п,(k;At). Поэтому дисперсия (мощность) второго слагаемого в уравнении (1) равна: >лом =М, D {Big= М; ° Рс,пр где DI9;)- дисперсия отсчетов сигнала противоположной стороны или мощность сигнала, поступающего из канала связи

Pc,пр.

Мощность первого слагаемого (1), которое представляет полезный результат суммирования, равна:

Отсюда можно найти R — отношение мощности полезного результата суммирования к мощности помехи, которая

1390803 обусловлена сигналом, поступающим из канала связи. Величина К; характеризует качество сформированной оценки

1.-го уровня сигнала передатчика:

P . 2

1 совета п Р4 (4)

R — М,—

Рс,пр

P с.пр

P к (5)

2 где к = 2 — количество возможных двоичных комбинаций на 411 выходе входного согласующего блока 1;

r — разрядность входного согласующего блока 1 и второго цифроаналогового45 преобразователя 11.

Если состояние счетчика 17 меньше

N, то на выходе порогового блока

18 нуль, в противном случае появляется логическая единица, которая 50 принудительна обнуляет счетчик 17.

Таким образом, коэффициент деления счетчика 17 равен Nä,, В момент включения счетчик 17 обнулен, поэтому в третьем 12 и четГ вертом 13 блоках памяти указаны нулевые ячейки памяти. В четвертом блоке 13 памяти вначале считывается нуль, Из уравнения (4) видно, что путем выбора соответствующего числа суммирования М;, которое затем фиксируется в постоянном запоминающем блоке 20, можно обеспечить сколь угодно высокое качество формирования оценки 1-ro уровня сигнала передатчика. Приближенно можно считать,что при больших значениях М; в i-й секции второго блока 10 памяти хранятся числа, в 1;; раз превышающие значения д-го уровня сигнала передатчика, наблюдаемого на входе канала связи.

Путем уменьшения в делителе 14 в М; раз получаем оценки для каждого i-го уровня сигналов передатчика.

Второй процесс — процесс накопления и хранения отсчетов передаваемых сигналов и суммы отсчетов передаваемых и принимаемых сигналов осуществляется с помощью третьего 12 и четвертого 13 блоков памяти, счетчика

17 и порогового блока 18. В первый момент времени перечисленные блоки обнулены. На входы порогового блока

18 подаются значения состояния счетчика 17 и значение N„o, которое 35 авиа а затем записывается первое значение передаваемого сигнала и (k, 4t), а в третьем блоке 12 памяти также считывается нуль и записывается значение суммарного сигнала с выхода аналогоцифрового преобразователя 4 в первый момент времени, которое равно х, (k„A t), (k, 4 )+у, (k,At). (6)

Аналогично при формировании входным согласующим блоком 1 очередной цифровой комбинации и (k At) в четвертый блок 13 памяти записывается по второму адресу значение п (1 at), а в третий блок 12 памяти записывается по тому же адресу значение х (1< 51) = n (k А ) + gg,k At) (7) и т.д. После достижения счетчиком 17 состояния Nä на выходе порогового

Ф блока 18 появляется логическая единица, которая принудительно обнуляет счетчик 17 и устанавливает вновь адреса в третьем 12 и четвертом 13 блоках памяти в нулевое состояние.

Из четвертого блока 13 памяти считывается значение n<(k,At), а из третьего блока 12 памяти считывается значение x„(k, A t) = n„(k, A t) +

+ у, (k 4 t), которое подается на второй вход второго блока 16 вычитания.

Значение п,(Е„л С) с четвертого блока 13 памяти используется затем для вывода соответствующей оценки переЧ даваемого сигнала n, (k, At), которая хранится во втором блоке 10 памяти.

После этого по нулевому адресу в четвертый блок 13 памяти записывается значение и „ (kit), а в третий блок 12 памятй записывается значение п рр(kit) + У „ „(kAt) °

Таким образом, как видно из описания второго процесса накопления отсчетов передаваемого и принимаемого сигналов, на период расчета оценки л уровня передаваемого сигнала и; (kAt) производится запоминание принимаемых отсчетов сигнала совместна с передаваемыми отсчетами в третьем блоке

12 памяти. В четвертом блоке 13 памяти производится запоминание последовательности передаваемых отсчетов п; (kid t).

Третий процесс — процесс компенсации отсчетов передатчика в принимаемом сигнале заключается в следующем.

Для расчета оценки передаваемого сигнала используются триггер 15 и комму1390803!

1 Г, n. (k; t) =-- g, n,(k; A t) + и, 1 ф;

+P y; (1с;ь t)) 1=1 (8) Далее полученная оценка передаваемого сигнала вычитает во втором блоке 16 вычитания из суммарного принимаемого и передаваемого сигналов отсчет передаваемого сигнала. Тем сачым из суммы передаваемых и принимамых сигналов компенсируется пере55 даваемый сигнал, чем и отделяется гракт передачи от тракта приема.

Устройство является адаптивным. татор 2. Данные узлы совместно с депителем 14, вторым блоком 16 вычитания и первым цифроаналоговым преобразователем 3 позволяют скомпенсировать 5 отсчеты передаваемых сигналов в принимаемом сигнале, Действительно,при расчете оценки передаваемого сигнала триггер 15 находится в нулевом состоянии и подключает коммутатор 2 таким 10 образом, что выход входного согласующего блока 1 оказывается подключенным к адресным входам второго блока

10 памяти. При компенсации отсчетов собственного передатчика в принимаемом сигнале триггер 15 следующим тактовым импульсом, поступающим от генератора 7, переходит в единичное состояние. Этим самым выход четвертого блока 13 памяти оказывается подключенным через коммутатор 2 к адресным входам второго блока 10 памяти. Цифровая комбинация с выхода четвертого блока 13 памяти, соответСтвующая передаваемому отсчету 25

n;(k At), указывает адрес во втором блоке 10 памяти, в котором для данной цифровой комбинации рассчитана оценка передаваемого сигнала. Данная оценка считывается из второго блока

10 памяти.и поступает в делитель 14.

Одновременно по,цругому входу на делитель 14 поступает также цифровая комбинация n„(k;at) с выхода четвергого блока 13 памяти. Эта цифровая комбинация определяет коэффициент деления делителя 14. Данные коэффициенты деления рассчитываются по формуле (4), поэтому в зависимости от уровня передаваемого сигнала n;(k;kt) при фиксированной величине помехи

Р„д делитель 14 имеет разные коэффициенты деления, Выходной сигнал делителя 14 равен

Действительно, при изменении параметров канала связи изменяется и уровень передаваемого сигнала на входе канала связи ° Однако через М; тактов работы устройства отсчеты сигнала передатчика записаны в первом блоке 6 памяти, Происходит расчет оценки передаваемого сигнала, который хранится во втором блоке 10 памяти, и устройство подстраивается под изменившиеся параметры. формула изобретения

1. Устройс во для разделения направлений передачи в дуплексных системах связи, содержащее первый цифроаналоговый преобразователь, формирователь адреса, последовательно соединенные второй цифроаналоговый преобразователь, аналого-цифровой преобразователь, первый блок памяти, первый блок вычитания, сумматор и второй блок памяти, последовательно соединенные генератор, входной согласующий блок и коммутатор, выход которого подключен к второму входу второго блока памяти, третий вход которого, а также второй вход первого блока памяти, второй вход аналого-цифрового преобразователя и первый вход формирователя адреса соединены с выходом генератора, выход аналого-цифрового преобразователя под ключен к второму входу первого блока вычитания, выход второго блока памяти подключен к второму входу сумматора, вход второго цифроаналогового преобразователя соединен с третьим входом первого блока памяти, о т л ич а ю щ е е с я тем, что, с целью .повышения пропускной способности,введены триггер, пороговый блок, третий блок памяти, последовательно соединенные счетчик, четвертый блок памяти, делитель и второй блок вычитания, второй вход и выход которого соединен соответственно с выходом третьего блока памяти и входом первого цифроаналогового преобразователя, выход генератора подключен к первому входу третьего блока памяти, второму входу четвертого блока памяти, входу триггера и первому входу счетчика, выход которого подключен к второму входу третьего блока памяти и входу порогового блока, выход которого подключен к второму входу

1390803

Составитель О. Андрушко

Техред М.Дидык Корректор А. Зимокосов

Редактор Н. Тупица

Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4!5

Заказ 1785/56

Производственно-полиграфическое предприятие, г ° Ужгород, ул. Проектная, 4 счетчика, выход входного согласующего блока подключен к входу второго цифроаналогового преобразователя,второму входу формирователя адреса и третьему- входу четвертого блока памяти, выход триггера подключен к второму входу коммутатора, третий вход которого соединен с выходом четвертого блока памяти, выход форми- 10 рователя адреса подключен к четвертому входу первого блока памяти,выход аналого-цифрового преобразователя подключен к третьему входу третьего блока памяти, а выход второго блока памяти подключен к второму входу делителя.

2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что формирователь адреса содержит последовательно соединенные постоянный запоминающий блок, пороговый блок, блок памяти и сумматор, второй вход которого является входом логической единицы, а выход подключен к вторым входам порогового блока и блока памяти, третий вход которого соединен с входом постоянного запоминающего блока и является вторым входом формирователя адреса, первым входом и выходом которого являются соответственно четвертый вход блока памяти и выход сум- матора.