Устройство для сопряжения процессоров в однородной вычислительной структуре

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессоров в однородную вычислительную структуру. Целью изобретения является расширение функциональных возможностей устройства за счет сопряжения процессоров с различными скоростями работы и анализа информационной напряженности данной ветви вычислительной системы. Для этого в устройство, содержащее счетчики 2 и 3 адреса записи и считывания соответственно , реверсивный счетчик 4, блок I памяти, группы эле.ментов ИЛИ 7 и И 5, 6, элементы задержки 20-23, элементы И 18, 19, триггеры 13, 14, 15, дополнительно введены два триггера 8, 9, два элемента ИЛИ 10 II, группа элементов И 12. I ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИ X

РЕСПУБЛИН

„„SU„„1392572 А 1 дд 4 G 06 F 15/16

I ф, Q r: аж !(Н ASTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

Il0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2!) 4 165620/24-24 (22) 24.12.86 (46) 30.04.88. Бюл. ¹ 16 (72) В. Н. !максименко и С. А. Важиов (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 989555, кл. G 06 F 13/00, 1981.

Авторское свидетельство СССР

¹ 1183975, кл. G 06 F 13/00, 1984. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

ПРОЦЕССОРОВ В ОДНОРОДНОЙ ВыЧИСЛИТЕЛЬНОЙ СТРУКТУРЕ (57) Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессоров в однородную вычислительную структуру. Целью изобретения является расширение функциона lbHblx возможностей устройства за счет сопряжения процессоров с различными скоростями работы и анализа информационной напряженности данной ветви вычислительной системы.

Для этого в устройство, содержащее счетчики 2 и 3 адреса записи и считывания соответственно, реверсивный счетчик 4, блок 1 памяти, группы элементов ИЛИ 7 и И 5, б. элементы задержки 20 — 23, элементы И 18, 19, триггеры 13, 14, 15, дополнительно введены два триггера 8, 9, два элемента ИЛИ 10

11, группа элементов 11 2. 1 ил.!

392572

Изобрстение Относится к Вычислительной технике и чижеT быть исполь;3овано для СОпря кения процессоров в однородную вычислительную структуру (ОВС).

11елью изобретения является рас<пирение функциональных Возможностей % стройства пут(ч сопряжения процессоров с различнычи (ê()1)<)H()II системы.

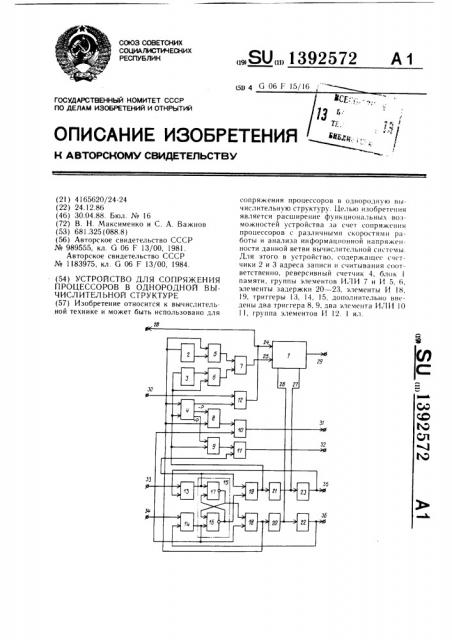

11а чертсжс показана структурная сыча (p ус гройства.

Ус гройство с одержит блок На ч яти, счетчик 2 адреса записи, счеTHèê 3 а <реса считыи;)ния, ренерсивный счетчик 4, элемент И 5

H< рll() Й гр3п11hl, э 1(. чс нты И 6 Второй гpx!! Ны, элемснты И. 1И 7 группы, четвсртый триггер <(, пятый триггер 9, первый элемент

И. 1И О, Второи элеченг И, 1И 11, элемаHT

И 12 третьей грхппы, первый триггер 13, Вгор<)й триггер 4, третий триггер 15, первый элсчент 11-HE 16, второй элемент И-НЕ 17, первый элемент 11 18, второй элемент И !9, первый 20, второй 21, третий 22 и четвертый 23 элементы задержки соответственно, информационный 24 и адресный 25 Входы

<)лока памяти, вход 26 записи блока памяти, Вход 27 считывания блока памяти, вход/вы- 25 хо 3 28 данных устройства, выход 29 данных

iстройства, I3xo;I, 30 считывания состояния загрхзки устройства, выход 31 сигнала запрета считывания устройства, выход 32 сигнала запрета записи данных устройства, Вход 33 сигнала считывания данных устрой- 30 (.тва, ВхОд 34 сигHd,1d записи данных В устройство, в Ix()g, 35 сигнала сопровождения (. ÷èTûâd Mhlx данных, выход 36 сигнала подтверждения записи.

Устройство работает следующим образом.

В исходном состоянии счетчики 2 записи, 3 считывания и реверсивный счетчик 4 находятся В нулевом состоянии, Hd разрядах адресного Входа 25 блока 1 памяти присутству T потенциал, соответствук)щий «О», Hd разрядах выхода 29 данных блока памяти и выходах элементов !2 третьей И группы по.(держивается Высокоичпедансное состояние, на выходе 32 запрета записи присугствует потенциал разрешающего сигнала, на выходе 31 сигнала запрета считывания поддерживается потенциал запрещающего 45 сигнала.

Выдача адресов записи и считывания со счетчиков 2 и 3 через схемы ИЛИ 7 группы на адресный вход 25 блокируется схемами 5 и 6 элементов И первой и второй групп, на вторые входы которых поступают нулевые управляющие сигналы с выходов элементов И 18 и 19.

Триггеры !3 и 14 установлены В нулевое состояние и с их выходов на входы схе.ч

2И-НЕ 16 и 17 и на вторые входы схем 2И 18 и 19 поступают нулевые потециалы, блокируя их.

Процесс записи или считывания данных в устройство начинается с анализа:3dl!)3(.I>!— вающим данные процессором (или считывающим данные процессором) состояния сигнальных выходов: 31 запрета считывания или 32 запрета записи. В исходном состоянии разрешается только запись данных в устройство. Записывающий данные процессор номе!цает данные на вход/выход 28 данных и вырабатывает команду записи на входе 34, которая устанавливает триггер

14 в единичное состояние, означающее запрос на запись информации в блок 1 памяти устройства. Запрос на запись высоким по<енциалом поступает на вход установки триггера 15 и второй вход элемента 2И 18, в то же

Время с выхода триггера 13 не выдается сигнал запроса на считывание и на первом выходе триггера 15, таким образом, присутствует высокий потенциал, что вызывает появление высокого потенциала на выходе элемента 2И 18. Этот потенциал поступает на вторые входы элементов 5 первой группы И, пропуская на выходы 25 через группу элементов ИЛИ 7 нулевой адрес с выходов счетчика 2 записи, и вырабатывает на выxîä(. элемента 20 задержки сигнал (26), управляющий записью данных в нулевую ячейку блока 1 памяти. Происходит запись данных в блок 1 памяти, а сигнал с выхода элемента 20 проходит элемент 22 задержки и поступает на вход сброса триггера 14, устанавливая его опять в нулевое состояние.

11ри sTîì с выхода элемента 18 снимается высокий потенциал управляю<пего сигнала, вы III«aH переход состояний счетчиков 2 записи и 4 реверсивного 4 к следующему значению адреса и установку триггера 8 в состояние, которое соответствует снятию сигнала запрета считывания с его выхода и выхода 31, на который сигнал проходит через схему ИЛИ 10. На этом цикл записи заканчивается. Во время каждого цикла записи на выходе 31 поддерживается сигнал запрета считывания, (ледующие циклы записи происходят аналогично, вызывая увеличение содержимого счетчиков 2 и 4. Окончание каждого цикла записи сопровождается со с Top() Mhl устройства сигналом (36) «Гlодтверждение записи».

Г1ри переполнении памяти устройства с выхода прямого переноса реверсивного счетчика 4+P выдается сигнал, устанавливающий триггер 9 в единичное состояние, соответствующее Выдаче через элемент

ИЛИ 1 на выход 32 сигнала «Запрет записи». Снятие сигнала «Запрет записи» происходит при осуществлении цикла считывания, когда сигнал с выхода элемента 19 возвращает трипер 9 в нулевое состояние. (цикл считывания начинается с анализа считывающим процессором состояния сигнала (32) «Запрет считывания». При отсутствии сигнала «Запрет считывания» процессор вырабатывает сигнал «Считывание» (33), который, проходя через элемент ИТ1И 11 на выход 32, устанавливает сигнал «Запрет записи» и переводит триггер 13 в единичное

1392572

10 состояние, 0;fначыющее запрос 113 счиTI,IB3uuc информации из блока 1 памяти хстройства. Этот сигнал устанавливает триггер 15 и нулевое состояние, при котором «нуль» с выхола элемента 2И-НЕ 17 посгупает на первый вход элемента 2И 18, тем самым блокируя его. На второй вхол элемента 2И 19 поступает елиничный сигнал с выхода триггеры 13 и на выхоле элемента 19 выра63тывается единичный сигнал, которь)й разрешает подачу адреса считывания со счетчика 3 считывания через группу элеxlpHToB

И 6 и группу элементов ИЛИ 7 tl;l адресные

Bxoды 25 блока 1 памяти. Информация из блока 1 памяти поступает на вы. Од 29 устр О Й(т в 3 I ro с и Г н 3;1 у считывания, t t p o x o, (Hщего с выхода элемента 21 за.ц ржки ны вход 27 разре(пения считывания блока памяти. Длительность сигнала считывания (27) опрелеляется элементом 23 задержки, с вых(>.jщий процессор. l lо сбросу сиги Зла сч иты ва и и я считывание из блока памяти завершается. триггер 13 устанавливается сигналом с выхода элемента 23 задержки в нулевое состояние, на выхоле элемента 2И 19 устанавливается низкий потенциал, со.(ержи мое счетчика 3 увеличивается, а реверсивного счетчика 4 — уменьшается на единицу. ( подачей на вход 3;3 устройства следукицего считывающего сигнала цикл о6служивыния запроса считывания повторяется. При считывании всей информации из устройства содержимое реверсивноп> счетчика стыновитсН равным нулю и сигнал с его выхола обратного переноса — Р1 устанывлива T трипер 8 в состояние, при котором с его выхода сигнал зыпр(та считывания поступает через элемент ИЛИ О на выход 31.

Возврат триггера 8 в исходное с(>стояние производится сигналом с выходы элс мента

2И 18 в цикле записи дынных в устройство.

LC. I H CH(II3, I вход 33 во время обслуживаиия запроса записи, он запоминается на триггере 13, не вызывая изменения состояния Tplll еры 15 до момента окончания цикла записи, т. с. до сброса триггера 14. После сбросы триггера 14 начинается цик.l обслуживания (ыпроса считывания.

Аналогично, если сигнал запроса зыпи H приходит на вход 34 во время протекания цикла считывания, сигнал запоминается на триггере 14 и обслуживание запроса записи начинается после окончания цикла считывания, т. е. после сбр<>са трип.еры 13.

Определение степени заполнения ланиыми устройства производится ри подаче с процессора сигнала считывания состояния загрузки на вход 30, который подклк)чает разрялы реверсивного счетчика 4 через группу 12 элементов И к шине 28. Анализ процессором содержимого счетчика 4 позволяет определить в однородной вычислительной системе информационнуlo напряженность

;инной ветви с целью оптимиз(>ции f;ll рхзки всех процессоров.

Таким образом, trpeплыгыемое усгройство осуществляет прием и вылачу ииформации при любом временном p3clloложении друг относительно друга сигналов записи и считывания и разных скоростях ры(н>ты полклк>чс иных к нс х1х процессОров.

ФОРI(f 1() I(IO(>P(г(н((1 ,vcTpoHcTBo лля сопряжения процессоров в однородной вычислительной структу рс, сол(ржащее счетчик адр(С3 записи, cчетчик

fäpåñ3 считывания, реверсивиый (четчик, лве группы элементов 11, группу эл(ментов

11;1И, блок памяти, четыре элементы задержки, три триггера, первьк Bxo;III элементов И первой и второй групп соединены (выхолами соответствуK)lllllx рызрялов счетЧ HKOB 3ЛРС (3 3(l tiff C H И 3ЛРЕС(1 (Ч И ТЫ Ы(> It HH

cooTBcтственнО, а выходы соелинены с первым и вторым вхолами элементов И, 1И группы соответственно, выходы которых соелинеtrbl с алресными вхолыми 6локы памяти, выход первого элеме>ггы зылержки с<>елинен с в холом записи 6лок(1 lrtf м яти и ч(p(. з Tp(1 и и

a;Ieмент залержки — — c вхолом С6роса второго триггс ра, Bxo;I, установки котороп> сос lltH H с входом режимы записи B 6лок памяти

>стройст(зы, ы выхоЛ второго триггеры с<к fftн«н с вхолом сброс3 третьегo триггеры, Bxo,l ус) ыновки KHTopot со(лин«н с выхолом первого триггеры, ti вход установки первоп> три(.геры соединен с вхолом режимы cчитывыния 6локы памяти устройства, вход cброс»

Ileрвого триггера соелинен с выхолом четвертого 3.1eмента ç3лержки, вход которого со(линен с выхолом второго элементы зылержки и вхолом считыв;(пия 6локы и;>мя)и, выхол которого соелинен с вы оцом данных устроис гва. От.)и càfor((,((c.í тем, чтО, с цельк> расширения функциональных во f»o>KttocTCII х сгройства путем сопряжения процессopoB с различными cкоростями работы и о6еспе|«ния 3H3.)и 33 информыционноЙ пап!)яж< Hiloct H данной ветви вычислительной структуры. в него введены четвертый и пятый триггеры, первый и второи элементы ИЛИ, третья группы элемеHTHB 11, первый и второй элементы И, Ireрвый вход первого элемент;l

И соединен с прямым выхолом третьеп> триггера, второй вход первого элементы И с<в IиН H c выходом второго TpHI Iåð3, выхол первого элемента И соелинен с вхолом первого элемента задержки, втор)(ми входами элементов И первой группы, сч(тным вхолом счетчика алреса записи, суммирук)и(им lfxoдом реверсивного счетчика и вхоЛом с6р<>са четвертого триггеры, первый вхол второго элемента И соединеH с инверсным выхоfoxt третьего триггера, а второй вход второго элемента И соединен с выхолом первого три(гера, выход второго элемента И соединен с входом второго элемента задержки, вторыми входами элементов И второй группы, счетиым вхолом счетчика адреса считывания, вычита1392572

Составитель Л. Иванов

Редактор А.Маковская Техред И. Верес Корректор В. Бутяга

Заказ 1809/54 Тираж 704 Подл ясное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 ющим входом реверсивного счетчика и входом сброса пятого триггера, вход установки которого соединен с выходом положительного переполнения реверсивного счетчика, выход пятого триггера соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого триггера, выход второго элемента ИЛИ соединен с выходом сигнала запрещения записи данных устройства, вход установки четвертого триггера соединен с выходом заема реверсивного счетчика, выход четвертого триггера соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго триггера, выход первого элемента

ИЛИ является выходом сигнала запрещения считывания данных устройства, информационные выходы реверсивного счетчика соединены с вторыми входами элементов И третьей группы, первые входы которых соединены с входом сигнала считывания состояния загрузки устройства, выходы элементов И третьей группы соединены с входом/

/выходом данных устройства и информационным входом блока памяти, выход третьего элемента задержки соединен с выходом сигнала подтверждения записи данных устройства, выход четвертого элемента задержки является выходом сигнала сопровождения считываемых данных устройства.