Запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств ЭВМ и систем хранения информации . Целью изобретения является упрощение устройства за счет уменьшения емкости блока памяти данных . Устройство содержит блок 1 кодирования , блок 2 памяти данных, блок 3памяти контрольной информации,блок 4контроля и коррекции ошибок, блок 5формирования контрольных сигналов, первый 6 и второй 7 блоки свертки по модулю два контрольной информации и блок 8 сравнения. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9) (И) А1 (59 4 G 11 С 29/00

ФСВ-,,„. jQ т

ОПИСАНИЕ ИЗОБРЕТЕНИЯ l " y- t

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (54 ) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЙ ОШИБОК (21 ) 41 1 41 28/24-24 (22) 29.08.86 (46) 30.04.88,Бюл. N9 16 (72) Н.И.Вариес и А.К.Култыгин (53) 681.327 (088.8) (56) Каган B,Ì, Электронные вычислительные машины и системы. М.: Энергия, 1979, с.434.

Журавлев Ю,П., Котелюк Л.А., Циклинский Н.И. Надежность и контроль ЭВМ. М.: Советское радио, 1978, с. 153-166. (57) Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств ЭВМ и систем хранения информации. Целью изобретения является упрощение устройства за счет уменьшения емкости блока памяти данных. Устройство содержит блок 1 кодирования, блок 2 памяти данных, блок

3 памяти контрольной информации, блок

4 контроля и коррекции ошибок, блок

5 формирования контрольных сигналов, первый 6 и второй 7 блоки свертки

l по модулю два контрольной информации и блок 8 сравнения. 2 ил.

1392595

Изобретение относится к вычислительной технике и может быть исполь зовано при разработке запоминающих устройств ЭВМ и систем хранения информации.

Цель изобретения — упрощение устройства эа счет уменьшения емкости блока памяти данных.

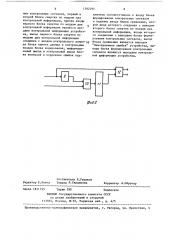

На фиг.1 приведена структурная 10 схема запоминающего устройства с коррекцией ошибок на фиг. 2 — структурная схема блока контроля и коррекции ошибок.

Устройство содержит (фиг.1) блок 1 15 кодирования, блок 2 памяти данных, блок 3 памяти контрольной информации, блок 4 контроля и коррекции ошибок, блок 5 формирования контрольных сигналов, первый 6 н второй 7 блоки 20 свертки по модулю два контрольной информации и блок 8 сравнения, Блок 4 содержит (фиг.2) блок 9 кодирования, формирователь 10 синдрома, блок 11 декодирования и блок 12 коррекции. 25

Устройство работает в двух режимах: записи и считывания.

В режиме записи на информационные входы устройства подается k-разряд- 30 ное информационное слово с соответствующими контрольными байтными разрядами. На выходе блока 6 формируется дополнительный контрольный разряд так, чтобы k-разрядное информационное слово с k/8 контрольными байтными и с дополнительным контрольным разрядами было нечетным, Слово, содержащее k информационных разрядов с дополнительным контрольным разрядом, контролируется корректирующим кодом. (k+1)-разрядное слово подается на информационные входы блока 2 и блока 1 кодирования, на выходе которого формируется r контрольных

45 разрядов путем подсчета четности сумм для определенных групп информационных k+1 разрядов, r-разрядное контрольное слово подается на информационный вход блока 3.

В режиме считывания (1+1)-разряд50 ное информационное слово и r-разрядное контрольное слово подаются на входы блока 4 контроля и коррекции ошибок, где производится выявление и коррекция ошибок в (k+1)-разрядном информационном слове. Скорректированное k-разрядное информационное слово с выхода блока 4 контроля и коррекции ошибок подается на выход устройства и на вход блока 5. Контрольные байтные разряды получают путем суммирования по модулю два сигнала байта, Контрольные байтные разряды подаются на выход устройства с выхода блока 5.

В предлагаемом устройстве корректирующие коды исправляют одиночные ошибки и обнаруживают двойные ошибки, но не выявляют полного пропадания слова на выходах блоков 2 и 3, При этом на выходах устройства формируется нулевое слово с правильными контрольными разрядами. Контрольные байтные разряды не контролируются корректирующими кодами, т.е. не выявляется неисправность блока 5. Все это выявляется путем сравнения дополнительного контрольного разряда> сформированного на выходе блока 7 с дополнительным контрольным разрядом, сформированным на выходе блока 4.При несравнении входных сигналов на выходе блока 8 формируется сигнал.

Формула изобретения

Запоминающее устройство с коррекцией ошибок, содержащее блок памяти данных, блок памяти контрольной информации, блок кодирования, блок контроля и коррекции ошибок, информационный выход которого является информационным выходом устройства, информационный и контрольный входы блока контроля и коррекции ошибок соединены соответственно с выходами блока памяти данных и блока памяти конт. рольной информации, информационный вход которого подключен к выходу блока кодирования, входы информационных разрядов блока памяти данных и информационные входы блока кодирования поразрядно объединены и являются информационными входами устройства, адресные входы, входы записи-чтения и входы выборки блока памяти данных и блока памяти контрольной информации соответственно объединены и являются адресным входом, входом разрешения записи-чтения и входом обращения устройства, о т л и ч а ю щ е ес я тем, что, с целью упрощения устройства за счет уменьшения емкос" ти блока памяти данных, в него введены блок сравнения, блок формирова1392595

ДОГ 2

Составитель В.Рудаков

Техред Л.Сердюкова

Корректор А.Обручар

Редактор Е.Копча

Заказ 1811/55

Тирам 590

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Укгород, ул. Проектная, 4 ния контрольных сигналов, первый и второй блоки свертки по модулю два контрольной информации, причем входЫ первого блока свертки по модулю два контрольной информации являются входами нонтрольной информации устройства, выход первого блока свертки по модулю два контрольной информации соединен с входом контрольного разря- 10 да блока памяти данных и контрольным входом блока кодирования, информационный выход и контрольный выход блока контроля и коррекции ошибок подключены соответственно к входу блока формирования контрольных сигналов и первому входу блока сравнения, второй вход которого соединен с выходом второго блока свертки по модулю два контрольной информации, входы которого соединены с выходами блока формирования контрольных сигналов, выход блока сравнения является выходом

"Неисправимая ошибка" устройства, выходы блока формирования контрольных сигналов являются выходами контрольной информации устройства.