Запоминающее устройство с коррекцией информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении управляющей памяти ЦВМ. Целью изобретения является расширение области применения устройства за счет коррекции массивов слов с программными адресами начала и конца и увеличения информационной емкости устройства без увеличения разрядности адресного кода. Запоминающее устройство содержит блок постоянной памяти, блок полупостоянной памяти (ППЗУ), блок начальных адресов, шифратор, коммутатор адреса, коммутатор данных, распределитель импульсов, элемент ИЛИ и триггер. Цель изобретения достигается тем, что в блоке начальных адресов набираются начальные адреса массивов , по каждому из которых в ППЗУ по соответствующим адресам заранее записаны 1 в дополнительном разряде и адрес следующего обращения к ППЗУ. В результате информация по следующему адресу будет скорректирована несмотря на то, что зтот адрес будет не совпадать с зафиксированными в блоке начальных адресов. Записанное в дополнительном разряде ППЗУ количество 1 определяется объемом корректируемого массива. 2 ил. § (Л

СОЮЗ СОВЕТСКИХ

C0LIHAЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) А1

GI) 4 С 11 С 29 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО делАм изОБРетений и ОткРытий

ФСР(.(,: -, (21) 4165026/24-24 (22) 22.12.86 (46) 30.04.88. Бюл. Ф 16 (72) В.И. Мхатришвили, А.М. Кибалов и Ю.И. Фокин (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

Ф 849304, кл. G 11 С 29/00, 1974.

Авторское свидетельство СССР

Ф 809400, кл. G ll С 29/00, 1974. личения разрядности адресного кода, Запоминающее устройство содержит блок постоянной памяти, блок полупостоянной памяти (ППЗУ), блок начальных адресов, шифратор, коммутатор адреса, коммутатор данных, распределитель импульсов, элемент ИЛИ и триггер, Цель изобретения достигается тем, что в блоке начальных адресов набираются начальные адреса массивов, по каждому иэ которых в ППЗУ по соответствуъ.дим адресам заранее записаны "1" в дополнительном разряде и адрес следующего обращения к

ППЗУ. В результате информация по следующему адресу будет скорректирована несмотря на то, что этот адрес будет не совпадать с зафиксированными в блоке начальных адресов. Записанное в дополнительном разряде ППЗУ количество "1" определяется объемом корректируемого массива. 2 ил.

1 (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано при построении управляющей памяти ЦВМ. Целью изобретения является расширение области применения устройства за счет коррекции массивов слов с программными адресами начала и конца и увеличения информационной емкости устройства беэ увеОПИСАНИЕ ИЗОБРЕТЕНИЯ;g(К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1392596

Изобретение относится к вычислительной технике и может быть исполь. эовано при построении управляющей па. мяти ЦВМ.

Целью изобретения является расширение области применения устройства эа счет коррекции массивов слов с произвольными адресами начала и конца и увеличения информационной емкос- 10 ти устройства без увеличения разрядности адресного кода.

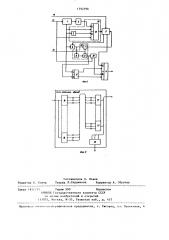

На фиг.l приведена схема запоминающего устройства; на фиг.2 — схема блока начальных адресов. !5

Запоминающее устройство (фиг.l) содержит. блок 1 начальных адресов, шифратор 2, первый элемент НЕ 3, коммутатор 4 данных, блок 5 полупостоянной памяти (ППЗУ), элемент ИЛИ 6, 20 первый элемент И 7, второй элемент

НЕ 8, второй элемент И 9, блок 10 постоянной памяти (ПЗУ), триггер 11, элемент И-ИЛИ 12, адресные входы 13, вход 14 запуска, вход 15 начальной 25 установки.

Блок 1 начальных адресов (фиг.2) содержит и дешифраторов 16, соединенных с адресными входами 13, m элементов И 17, элемент ИЛИ 18, причем один 30 иэ выходов каждого дешифратора 16 соединен с одним из входов элементов

И 17, выходы которых подключены к входу шифратора 2 и входам элемента

ИЛИ 18. Код адреса, поступающий на

35 блок начальных адресов, разбивается на п групп разрядов, каждая группа дешифрируется своим дешифратором 16, один из выходов каждого дешифратора в соответствии с кодом начального ад- 40 реса корректируемого массива соединяется с входом элементов И 17 (число этих элементов m равно максимально возможному числу начальных адресов) °

Элементы НЕ 3 и И-ИЛИ 12 (фиг.l) представляют собой коммутатор 19 адреса, а элементы 7 — 9 — распределитель 20 импульсов, Устройство в режиме коррекции работает следующим образом.

При корректировке одиночных слов в блоке I начальных адресов перемычками набираются коды адресов этих слов. До появления сигнала "Корр.1" на выходе элемента ИЛИ 18 устройство работает как обычное ПЗУ, т.е. на блок ПЗУ 10 поступают код адреса и сигналы запусKB, (..÷èòàííèå сигналы поступают на выход устройства. В случае обнаружения блоком начальных адресов одного из адресов корректируемых слов шифратор 2 преобразует этот адрес в новый адрес блока ППЗУ 5, по которому заранее записана скорректированная информация и, например, "0" в дополнительном разряде. По сигналу "Корр.1" на блок ППЗУ 5 поступает ширрированный адрес и сигнал запуска, считанная информация с ППЗУ 5 поступает на выход устрой ства.

При поступлении на устройство следующего адреса (отличающегося от адресов корректируемых слов) сигнал

"Корр.!" прекращается и выбор числа происходит опять из блока ПЗУ 10.

При корректировке массивов или при увеличении объема памяти запоминающего устройства в блоке 1 начальных адресов набираются начальные адреса массивов, по каждому из которых в блоке ПЧЗУ 5 по соответствующим шифрированным адресам заранее записанй адрес следующего обращения к ППЗУ 5 и "1" в дополнительном разряде (" Корр 2"), свидетельствующая при считывании о том, что следующий адрес, хотя код этого адреса и не набран в блоке 1 начальных адресов, должен быть скорректирован. При поступлении на адресный вход 13 устройства адреса, совпадающего с одним иэ набранных начальных адресов массивов, аналогично коррекции одиночного слова, происходит считывание из

ППЗУ 5. При этом сигнал "Корр.2" действует так же, как и сигнал "Корр.1", за исключением того, что код адреса на ППЗУ 5 поступает с шины 13 адреса, 11 1!

1 в дополнительном разряде корректированных чисел массива должна быть записана столько раэ, каков объем корректируемого массива, в последнем слове массива дополнительный разряд ППЗУ 5 содержит "0". После окончания сигнала "Корр.2" последующая выборка происходит из блока

ПЗУ IO, Увеличение объема запоминающего устройства в 2 раза происходит эа счет того, что одни и те же коды адресов испопьэуются дважды: как для ПЗУ

lO без признака вторичной коррекции, так и для ППЗУ 5 с признаком вторичной коррекции. При использовании нескольких (1) дополнительных разрядов

1392596 возможно увеличение объема памяти в

21 раз.

Устройство работает следующим образом.

Сначала по входу 15 на вход блока

ППЗУ 5 приходит сигнал начальной установки, который обнуляет его регистр числа и поэтому с первого выхода этого блока на второй вход элемен- 10 та ИЛИ 6 поступает сигнал "О" (отсутствие признака вторичной коррекции), Далее устройство работает до появления на выходе блока I начальных адресов сигнала "Корр ° 1" как обычное

ПЗУ, т.е. коды адреса поступают на блок ПЗУ 1О по входам 13 адреса, а импульс на вход 14 запуска — через открытый элемент И 9. Коды чисел с выхода блока ПЗУ 10 через коммутатор 20

4 данных поступают на выход устройст" ва (триггер 11 предварительно устанавливается в "О" импульсом запуска).

В случае обнаружения блоком 1 начальных адресов одного из начальных 25 адресов сигнал "Корр.1" открывает первый элемнт И элементов И-ИЛИ 12, закрывает через элемент НЕ 3 второй элемент И элементов И-ИЛИ 12, через элемент ИЛИ 6 открывает элемент И 7 и через элементы ИЛИ 6 и HE 8 закры1 вает элемент И 9 и устанавливает триггер 11 в положение "1" °

Таким образом, на блок ППЗУ 5 пос" тупает импульс на вход 14 запуска через открытый элемент И 7 и шифрованный код адреса с выхода шифратора 2 через элемент И-ИЛИ 12 ° Считываемая из ППЗУ информация поступает через коммутатор 4 на выход устройства °

Если необходимо скорректировать и следующее слово, то в специальном дополнительном разряде ППЗУ 5 записывается, например, l" свидетельствующая при считывании о том, что сле- 45 дующий адрес, хотя код этого адреса и не набран в блоке начальных адресов, должен быть скорректирован. Эта

"1" образует сигнал "Корр.2", который действует так же, как и сигнал

"Корр.1", за исключением того, что код адреса на ППЗУ 5 поступает с входов 13 адреса. Таким образом, "1" должна быть записана столько раз, каков объем корректируемого массива. В последнем слове массива в дополнительный разряд ППЗУ 5. записывается

"0", и следующий импульс на вход 14 запуска поступает на ПЗУ 10 и сбрасывает триггер 11 в "0". При этом вновь считывается информация из ПЗУ и через коммутатор 4 данных поступает на выход. формул а изобретения

Запоминающее устройство с коррекцией информации, содержащее блок постоянной памяти, адресные входы которого являются одноименными входами блока устройства и соединены с входами начальных адресов, выходы кода совпарения которого подключены к входам шифратора, блок полупостоянной памяти и коммутатор данных, выходы которого являются информационными выходами устройства, о т л и ч а ю— щ е е с я тем, что, с целью расширения области применения устройства засчет коррекции массивов слов с произвольными адресами начала и конца и увеличения информационной емкости устройства без увеличения разрядности адресного кода, в устройство введены коммутатор адреса, элемент ИЛИ, распределитель импульсов и триггер, причем информационные входы первой и второй групп коммутатора адреса соединены соответственно с выходами шифратора и адресными входами устройства, выход признака совпадения блока начальных адресов подключен к S-входу триггера, первому входу элемента ИЛИ и

1 управляющему входу коммутатора адреса, выходы которого соединены с ад ресными входами блока полупостоянной . памяти, выход дополнительного Разряда и вход выборки которого подключены соответственно к второму входу элемента ИЛИ и к первому выходу распределителя импульсов, импульсный вход которого является входом запуска устройства, а управляющий вход и второй выход соединены соответственно с выходом элемента ИЛИ и R-входом триггера, прямой и инверсный выходы которого подключены к управляющим входам коммутатора данных, информационные входы первой и второй групп которого соединены соответственно с выходами основных разрядов блока полупостоянной памяти и выходами блока постоянной памяти, вход выборки которого подключен к второму выходу распределителя импульсов, вход начальной установки блока полупостоянной памяти является одноименным входом устройства.

1392596

Составитель О. Исаев

Редактор Е. Копча Техред Л.Сердюкова Корректор А. Обручар

Закаэ I 81 1! 55 Тиралс 590 Подписное

В11ИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Проиэвол< нелло-по 1пграфическое предприятие, г. Упгород, у». Проектная, 4