Дельта-декодер

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи информации с дельта-модуляцией позволяет - повысить точность декодирования за счет расширения динамического диапазона . Дельта-декодер содержит регистр сдвига, цифровой детектор 2, амплитудно-импульсный модулятор 3, интегратор 4, фильтр 5 нижних частот, компандер 6 и слоговый фильтр 7. Благодаря введению регистра 8 сдвига, блока 9 коррекции и управляемого усилителя 10 обеспечиваются минимальные искажения, что позволяет повысить качество передаваемого речевого сигнала . з.п.ф-лы, 3 ил.

СООЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 Н 03 М 3 02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

gCF-.-„„.„. "4д

ollHcAHHE изоБретения /,"

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ п (54) ДЕЛЬТА-ДЕКОДЕР (57) Изобретение относится к автоматике и вычислительной технике. Его искажения, что позволяет повысить качество передаваемого речевого сигнала. 1 з.п.ф-лы, 3 ил. (2) ). 41 ) 84 7 8/24-24 (22) )7.09.86 (46) 30.04.88. Бюл. М 16 (72) В.М.Дорофеев, Ю.Ф.Коновалов и С.Н.Дерюгин (53) 621.376.56(088.8) (56) ТИИЭР,1967,т.55,11 З,с.64,фиг.5.

Труды НИИР, 1985, У 1, с.65, рис.1.

Труды НИИР, 1985в У 4, с.83, рис.2.

„„SU„, 1392619 А1 использование в системах передачи информации с дельта-модуляцией позволяет .повысить точность декодирования за счет расширения динамического диапазона. Дельта-декодер содержит регистр ) сдвига, цифровой детектор 2, амплитудно-импульсный модулятор 3, интегратор 4, фильтр 5 нижних частот, компандер 6 и слоговый фильтр 7. Благодаря введению регистра 8 сдвига, блока 9 коррекции и управляемого усилителя 10 обеспечиваются минимальные!

39?619

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи информации с применением дельта5 мод уляции.

Цель изобретения - повышение точности декодирования за счет расширения динамического диапазона.

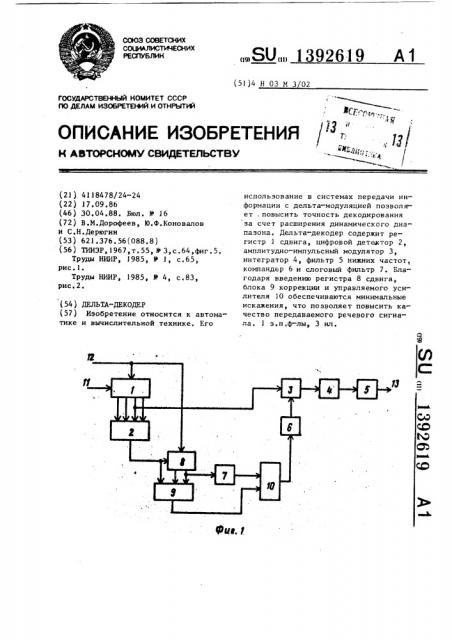

На фиг.1 изображена функциональная схема дельта-декодера; на фиг.2схема блока коррекции для случая k=

3; на фиг.З - временные диаграммы, поясняющие работу дельта"декодера.

Дельта-декодер содержит первый регистр 1 сдвига, цифровой детектор 2, амплитудно-импульсный модулятор 3, интегратор 4, фильтр 5 нижних частот, компандер 6, слоговый фильтр 7, второй регистр 8 сдвига, блок, 9 кор- 2п рекции и управляемый усилитель 10.

На фиг.l изображены информационный ll и тактовый 12 входы, а также выход 13.

Первый регистр 1 сдвига имеет и разрядов, оптимальной величиной явля- 25 ется п 4, Второй регистр 8 сдвига имеет k-1 разрядов, оптимальной величиной является k.= 3.

Цифровой детектор 2 задан функ- . цией вида — hх3лхф /vs%,n x,nХ3n x4!ф где х,,... х — входы цифрового детектора 2; у — выход цифрового детектора 2.

Компандер 6 представляет собой 35 (как и усилитель 10) операционный усилитель с отрицательной обратной связью. Блок 9 коррекции выполнен (фиг.2)на k ключах 14 (например, транзисторных) и k резисторах 15.

Дельта-декодер работает следующим образом.

Входной дельта-модулированный (ДМ) сигнал (фиг.За ) поступает с входа 11 дельта-декодера на регистр 1, так- 45 тируемый с входа 12 (фиг. Зб), С выхода цифрового детектора 2, реагирующего на и разряд одинаковых символов

ДМ-сигнала, на вход регистра 8 поступает импульс(фиг.Зв), На выходах регистра 8 формируются сигналы (фиг.Зг,д). Одновременно на вход амплитудно-импульсного модулятора 3 поступает сдвинутый сигнал с выхода

k-ro разряда регистра 1 (фиг.3e), Сигнал на выходе блока 9 коррекции зависит от того, на скольких его входах (и на каких именно ) присутствуют сигналы. Кроме того, сигнал с выхода регистра S через слоговый фильтр 7 поступает на вход усилителя 10. При этом на выходе управляемого усилителя 10 сигнал меняется по величине (фиг.Зж) и через компандер 6 поступает на управляющий вход модулятора 3.

Следовательно, задержка выходного сигнала с регистра 1 необходима для компенсации задержки в регистре 8.

С модулятора 3 сигнал интегрируется (фиг. Зз ), и аппроксимирующее напряжение у (t,) через фильтр 5 поступает на выход 13.

Таким образом, предлагаемый дельта-декодер обеспечивает минимальные искажения эа счет коррекции напряжения на выходе компандера 6, а следовательно, аппроксимирующего напряжения на выходе интегратора 4. В результате увеличивается отношение сигнал/шум при передаче аналоговых сигналов и расширяется динамический диапазон дельта-декодера, что позволяет повысить или качество передачи сигналов, или уменьшить скорость передачи при сохранении качества речи.

Фо рм ул а и э о б р е тени я

1, Дельта-декодер, содержащий перBblH регистр сдвига, информационный и тактовый входы которого являются одноименными входами дельта-декодера, выходы первого - n-ro разрядов первого регистра сдвига (п ), 4)) подключены к одноименным входам цифрового детектора, слоговый фильтр, компандер, выход которого соединен с управляющим входом амплитудно-импульсного модулятора., выход которого через интегратор соединен с входом фильтра нижних частот, выход которого является выходом дельта-декодера, о т л и— ч а ю шийся тем, что, с целью повышения точности декодирования эа счет расширения динамического диапазона, в дельта-декодер введены управляемый усилитель, блок коррекции и второй регистр сдвига, тактовый вход которого подключен к тактовому входу дельта-декодера, выход цифрового детектора подключен к первому входу блока коррекции и информационному входР второго регистра сдвига, выходы первого - .(k-2)-ro разрядов которого (14k (и-1) соединены соответственно с вторым — (k-1)-м входами блока коррекции, выход которого подклк

l:3 )(19 чен к управляюшему входу управляемого усилителя, выход (k-1)-го разряда второго регистра сдвига соединен непосредственно с k-м входом блока кор5 рекции и через слоговый фильтр - с информационным входом управляемого усилнтеля, выход которого соединен с входом компандера, информационный вход амплитудно-импульсного модулятора подключен к выходу k-го разряда первого регистра сдвига.

2. Дельта-декодер по п.1, о т л ич а ю ш и и с я тем, что блок коррекции выполнен на k резисторах, шине нулевого потенциала и 1 ключах, информационные входы которых подключены к шине нулевого потенциала, управляющие Входы первого — k-го ключей являются соответственно первым—

k-м входами блока, выходы первого—

k-го ключей через одноименные резисторы подключены к выходу блока.

1392619

y+(c) х(г)

0) Составитель О.Ревинский

Техред М.Дидык Корректор С.Шекмар

Редактор Е.Копча

Заказ 1889/ 56 Тирад 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Уигород, ул. Проектная, 4