Устройство для адресации блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти. Целью изобрет ения является расширение области применения за счет построения схемы устройства в виде регулярной структуры . Положительный эффект от использования изобретения достигается в максимальной степени при микроэлектронной реализации устройства для адресации блоков памяти. Поскольку большая часть схемы устройства вьтолнена в виде регулярной структуры, значи- Q тельно упрощаются изготовление и конт роль комплекта фотошаблонов, 1 ил. - « (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 С 06 Г 12/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4149071/24-24 (22) 17.11.86 (46) 07.05.88. Бюл. В 17 (71) Таганрогский радиотехнический институт им. В.Д. Калмыкова (72) А. П. Купровский, В. !0. Лоэбе" нев и Н. Г. Пархоменко (53) 681.325(088.8) (56) Авторское свидетельство СССР

9 936035, кл. G 06 F 13/00, 1982.

Авторское свидетельство СССР

11 1024926, кл. G 06 F 13/00, 1983.

„„SU„„1394217 А 1 (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ БЛОКОВ

ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти. Целью изобретения является расширение области применения за счет построения схемы устройства в виде регулярной структуры. Положительный эффект от использования изобретения достигается в максимальной степени при микроэлектронной реализации устройства для адресации блоков памяти. Поскольку большая часть схемы устройства выполнена в виде регулярной структуры, значительно упрощаются изготовление и конт-роль комплекта фотошаблонов. 1 ил.

1394217

Изобретение относится к вычислительной технике и может быть исполь- зовано для адресации блоков памяти о в системе памяти, Целью изобретения является расширение области применения за счет построения схемы устройства в виде ре-; гулярной структуры„

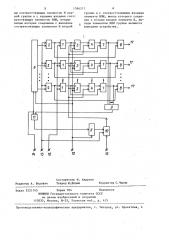

На чертеже представлена функциональная схема устройства.

Устройство содержит группу I переключателей, первую группу 2 элементов И, группу 3 регистров, группу

4 схем сравнения, счетчик 5, регистр

6 сдвига, вторую группу 7 элементов

И, группу 8 элементов ИЛИ, злемен г

ИЛИ 9, коммутатор 10, элемент И 11 и имеет вход 12 сброса устройства, вход

13 режима работы устройства, тактовый вход 14 устройства, адресный вход

15 устройства, вход 16 установки флага годности устройства, группу 17 выходов устройства.

Устройство работает следующим образом.

Принцип работы устройства основан на присвоении неотключенным блокам памяти последовательно-непрерывных адресов в общей системе адресации.па- 0 мяти.

Устройство может работать в режиме присвоения условных непрерывных адре сов неотключенным блокам памяти и в режиме выбора блока при обращении к памяти.

Режим присвоения условных непрерывных адресов неотключенным блокам памяти осуществляется следующим образом.

Производится отключение блоков путем установки соответствующих переключателей 1 в нулевое положение.

Сигналом Сброс произвОдится ус 45 тановка в нулевое положение счетчика 5, регистров 3 условных адресов и регистра 6 сдвига.

На вход 13 режима работы устройсТаа подается сигHasr "Контроль", торый поступает на первые входы элементов И 2 первой группы и подготавливает их к включению. Кроме этого, сигнал "Контроль" поступает на управляющий вход коммутатора 10, который отключает адресный вход 15 устройст55 ва и подключает выход счетчика 5, на котором установлен нулевой адрес, который поступает через коммутатор

l0 на информационные входы регистров

3 условных адресов.

На тактовый вход 14 устройства поступает первый синхроимпульс, по заднему фронту которого на первом выходе регистра 6 сдвига появляется единичный сигнал, который поступает на второй -axep подготовленного к включению первого элемента И 2 первой группы и проходит через него на второй вход первого элемента ИЛИ 8 и на выход устройства, возбуждая первый блок памяти.

После проведения контроля первого блока, в случае его годности, на входе 16 устройства появляется сигнал "Флаг годности", который устанавливает переключатель 1 первого блока в единичное состояние. Регистр

3 условного адреса первого блока памяти с инверсным управляющим входом блокируется и запоминает нулевой адрес счетчика.

В момент установки переключателя

1 первого блока в единичное состояние единичный сигнал с его выхода разрешает прохождение единичного сигнала с выхода схемы 4 сравнения первого блока, который является результатом совпадения адресов, поступающих с регистра б условного адреса первого блока и со счетчика 5. Далее он проходит через многовходовой элемент ИЛИ и поступает на второй вход входного элемента И 11 и разрешает прохождение второго синхроимпульса на счетчик 5. Если первый блок негоден, на вход 16 устройства сигнал

"Флаг годности" не подается и переключатель 1, соответствующий первому блоку, остается в нулевом состоянии.

Вследствие этого элемент И 7 второй группы первого блока остается закрытым и на втором входе входного элемента И 11 находится сигнал низкого .уровня, который запрещает переключение счетчика 5 по второму синхроимпульсу, После прихода второго синхроимпульса логическая "I сдвигается с первого выхода регистра 6 сдвига на

Ф второй, а переключение счетчика не происходит.

Аналогично происходит присвоение последовательно-непрерывных адресов остальным неотключенным блокам памяти.

1394217

Таким образом, счетчик 5, хранящий адрес последнего годного блока, увеличивает свое состояние на единицу только после установления факта годности очередного проверяемого бло" ка (т.е. после установки в единичное состояние переключателя 1 проверяемого флока) .

Одновременно с этим в регистре 6 условных адресов записываются адреса, являющиеся номерами годных блоков.

Так происходит установка непрерывного поля адресов годным блокам памя- 15 ти. После этого устройство готово работать в режиме выбора блока при ббращении к памяти.

С входа 16 режима работы устройства выбирается единичный сигнал 20

"Контроль". Устройство возвращается в первоначальное состояние: коммутатор 5 отключает выход счетчика 5 и подключает входные адресные шины для. обращения к памяти. Возникший нулевой 25 потенциал на первых входах элементов И 2 запрещает изменять состояние соответствующих им переключателей I отключения блоков памяти.

Режим выбора блока памяти при обращении к памяти осуществляется пу" тем сравнения на схемах 4 сравнения условных кодов, установленных на регистрах 3, с кодом адреса, установленном на адресных шинах устройства.

В случае совпадения данных кодов на выходе i-й схемы 4 сравнения вырабатывается сигнал, который поступает на первый вход 1 го элемента И 7 второй группы. Если на втором входе присутствует "Флаг готовности" i-ro блока памяти, поступающего с i-го переключателя I, то на i"é выход 17 устройства с выхода i-ro элемента И 7 второй группы поступает сигнал воз- 45 буждения i-ro блока.

Использование регистра сдвига, входного элемента И выгодно отличает предлагаемое устройство от известного, так как первое обладает однородной структурой — каждому разряду регистра сдвига соответствует одинаковый набор логических элементов и связей между ними, что значительно упрощает изготовление фотошаблонов при микроэлектронной реализации устройства.

Кроме этого, использование коммутатора позволяет сократить количество шин и использовать одни и те же шины в режиме присвоения непрерывных адресов и в режиме внешних обращений..

Введение элементов И второй группы позволяет устройству вырабатывать сигнал возбуждения i-ro блока только в случае его годности, что исключает ложное срабатывание схем сравнения .в случае совпадения кодов.

Формула изобретения

Устройство для адресации блоков памяти,.содержащее группу переключателей, первую группу элементов И, группу регистров, группу схем сравнения, счетчик, причем входы сброса регистров группы и счетчика соединены с входом сброса устройства, выходы регистров группы соединены с первыми входами соответствующих схем сравнения группы, о т л и ч а ю— щ е е с я тем, что, с целью расширения области применения за счет построения схемы устройства в виде регулярной структуры, в него введены регистр сдвига, вторая группа элементов И, группа элементов ИЛИ, эле мент ИЛИ, коммутатор, элемент И, причем пеРвые входы элементов И первой группы соединены с управляющими входами коммутатора и с входом режима работы устройства, вторые входы элементов И первой группы соединены с соответствующими выходами регистра сдвига, вход сброса которого соединен с входом сброса устройства, тактовый вход регистра сдвига соединен с первым входом элемента И и с тактовым входом устройства, выход элемента И соединен со счетным входом счетчика, выход которого соединен с первым информацион" ным входом коммутатора, второй информационный вход которого соединен с адресным входом устройства, выход коммутатора соединен с информационными входами регистров группы и с вторыми входами, схем сравнения группы, выходы которых соединены с первыми входами соответствующих элементов И второй группы, вторые входы которых соединены с инверсными. управляющими входами регистров группы и с выходами соответствующих переключателей группы, первые входы которых соединены с входом установки флага годности устройства, вторые входы переключателей группы соединены с выхода"

1394217

Ф Q 16

Составитель И. Андреев

Техред М.Дидык Корректор С.Черни

Редактор А. Ворович

Заказ 2221/45 Тираж 704 Подписное

ВНИИПИ .Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 ми соответствующих элементов И первой группы и с первыми входами соответствующих элементов ИЛИ, вторые входы которых соединены с выходами соответствующих элементов И второй группы и с соответствующими входами .элемента ИЛИ, выход которого соединен с вторым входом элемента И, выходы элементов ИЛИ группы являются выходами устройства.