Устройство для обучения основам вычислительной техники

Иллюстрации

Показать всеРеферат

Изобретение относится к учебнолабораторному оборудованию и может быть использовано в учебном процессе, а также в конструкторских бюро для моделирования и отладки дискретных устройств, построенных на интегральных микросхемах Цель изобретения - расширение дидактических возможноетей устройства, Устройство содержит пульт 1 оператора, блок 2 индикации, i

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (. д) 4 G 09 В 23/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4035087/24-24 (22) 1).03.86 (46) 07.05.88. Бюл. У 17 (72) В.А.Несмелов, С.Ф.Тюрин, Т.И.Коган и М.Е.Буймов (53) 681.3.07) (088.8) ,(56) Авторское свидетельство СССР

У 1005156, кл. G 09 В 9/00, 1981.

Устройство обработки информации.

Руководство к лабораторным работам,/

Под ред. А.Е.Амбросова, Харьков:

ХВВКИКУ, 1977.

„;SU„, 1394222 А1 (54) УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ

ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ (57) Изобретение относится к учебнолабораторному оборудованию и может быть использовано в учебном процессе, а также в конструкторских бюро для моделирования и отладки дискретных устройств, построенных на интегральных микросхемах. Цель изобретения расширение дидактических возможностей устройства. Устройство содержит пульт 1 оператора, блок 2 индикации, . ющим входам и выходам элемента 18 и к входу светодиода 22. Сущность изобретения основана на осуществлении прогнозирования последующего состояния триггера, что сокращает количество экспериментов для построения математической модели синтезированного автомата. 2 ил, 13942?2 коммутатор 3 входных сигналов, наборное поле 4, модули 5 логических элементов, модули 6 триггеров. Каждый модуль 6 состоит из коммутатора 17, элемента 18 памяти, коммутатора 19, светодиода 20, подсоединенного к прямому выходу элемента 18, блока 21 прогнозирования (последующего состояния), подсоединенного к соответствуИзобретение относится к учебнолабораторному оборудованию и может быть использовано в учебном процессе, а также в конструкторских бюро для моделирования и отладки дискретных устройств, построенных на интегральных микросхемах.

Целью изобретения является расширение дидактических возможностей уст- 10 ройства путем прогнозирования последующего состояния триггеров в моделируемых схемах.

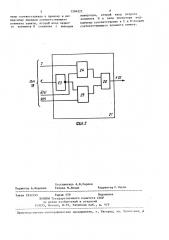

На фиг.1 представлена структура устройства; на фиг,2 -.функциональ- 15 ная схема блока прогнозирования.

Устройство для обучения основам вычислительной техники содержит (фиг,1) пульт 1 оператора, блок 2 индикации, коммутатор 3, наборное 20 поле 4, модули 5 логических элементов и модули б триггеров. Пульт 1 оператора содержит генератор 7 одиночных импульсов у генератор 8 непрерывной последовательности, переключатель 9 рода работ, генератор 10 нуля, управляющую клавиатуру 11 и блок 12 триггеров.

Модуль 5 содержит коммутатор 13, логический элемент 14, блок 15 инди- 30 кации, коммутатор 16, Модуль 6 содержит коммутатор 17, элемент 18 памяти, коммутатор 19, светодиод 20, блок 21 прогнозирования, светодиод

22. Каждый блок 21 (фиг.2) содержит инвертор 23, элементы И 24 и 25, элемент ИЛИ 26.

Генератор 7 представляет собой кнопку без фиксации, подключенную 40 входным контактом к шине "-", а выходными контактами - к входам триггера 6.

Генератор 8 представляет собой генератор прямоугольных импульсов амплитудой, равной напряжению логической

ll ) tl о

Генератор 10 представляет собой ограничительный резистор, подсоединенный одним концом к шине "-", а другим — к выходу пульта 1 оператора, Управляющая клавиатура 11 представляет собой регистр кнопок с фиксацией, необходиьых для задания входного сигнала.

Блок 12 содержит триггеры по числу разрядов управляющей клавиатуры и предназначен для устранения дребезга контактов клавиатуры.

Модули 5 и б конструктивно выполнены в ниде пластикового корпуса, снабженного кроме контактов входного и выходного полей клеммами подачи питания, с помощью которых и производится установка их на наборное поле, имеющее специальные гнезда. На верхней крьппке модулей 5 и 6 изображено условно-графическое обозначение микросхемы, Светодиоды 20 и 22 обьединены в блок 27 индикации.

Соединения ".осуществляются соединительными проводами (не показаны), Устройство работает следующим образом.

Обучаемый, решив задачу логического синтеза функциональной схемы по заданным условиям работы, набирает ее на наборном поле 4 из модулей 5 и 6 с помощью соединительных проводов (не показаны), соединяющих комз 13942 мутаторы 3, 13, 17, 16 и 19 в "оответствии с полученной функциональной схемой. Для построения математической модели синтезированного автома5 та обучаемый при помощи генератора

10 устанавливает элементы 18 по входам н состояние, соответствующее коду первой строки таблицы переходов выходов. Это состояние в двоичном коде отображается на светодиодах

20.

Затем обучаемый подает входные сигналы при помощи управляющей клавиатуры 11, при этом блок 12 устраняет 15 дребезг контактов клавиатуры и воздействует через блок 2, который отображает двоичный код входного сигнала, на внешние входы автомата, подключенные к коммутатору 3. При этом блоки

21 воспринимают входные и выходные .сигналы элементов 18. Инвертор 23 (фиг.2) инвертирует сигнал с входа элемента 18, элемент 25 производит операцию логического умножения над 25 сигналами, поступающими с выхода инвертора 23 и выхода элемента 18. Элемент 24 производит операцию логического умножения над сигналами элемента

18. Элемент 26 производит операцию З0 логического сложения сигналов, поступающих с выходов элементов 24 и 25.

Таким образом, блок 21 реализует функцию, соответствующую таблице нс»1 тинности состояний элемента 18. Полученная функция принимает значение логического нуля.в том. случае, если элемент 18 в последующем таите установится в нулевое состояние, при этом светодиод 22 не горит, и значе-;40 ние логической единицы — в противном: случае, при этом светодиод 22 горит.

Поэтому, считывая индикацию по све-. тодиодам 22, обучаемый получает двоичную информацию, отмечаемую в каждой клетке таблицы переходов выходов без дополнительных операций, только путем изменения комбинации входных сигналов, Это позволяет получить математическую модель синтезированного автомата, Во время построения математической модели обучаемый производит отладку автомата, используя дополнительно блоки 15, отображающие выходные состояния каждого из элементов

14. Затем производится проверка выполнения заданных условий работы сии тезированногб автомата в синхронном ручном и автоматическом режимах, ис», 22 пользуя генератор 7 одиночных импульсов, генератор 8 и переключатель

9 и подавая сигналы синхронизации на входы синхронизации элементов 18 с коммутатора 3.

Таким образом, введение блоков 21 прогнозирования {последующего состояния ) существенно расширяет дидактические возможности устройства при обучении основам дискретной техники и сокращает за счет этого количество экспериментов для построения матема" тической модели синтезированного автомата.

Ф о р м у л а и s о б р е т е н и я

Устройство для обучения основам вычислительной техники, содержащее пульт оператора, выходы которого подключены к соответстнующим входам блока индикации и коммутатора, вьжоды которого являются соответствующими выходами первой группы устройства, первую группу коммутаторов, входы которых являются входами первой группы устройства, а выходы соединены с соответствующими входами элементов памяти, прямые выходы которых соединены с первыми входами блоков индикации первой группы и с первыми входами коммутаторов второй группы, а инверсные выходы подключены к нторым входам коммутаторов второй группы, выходы которых являются соответству-ющими выходами второй группы устройства, третью группу коммутаторов, входы которых являются соответствующими входами второй группы устройства, а выходы соединены с соответствующими входами логических элементов, выходы которых подключены к входам соответствующих блоков индикации второй группы и коммутаторов четвертой группы, выходы которых являются соот" ветствующими ныходами третьей группы устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения дидактических возможностей устройства, в него введена группа блоков прогнозирования, каждый из которых содержит инвертор, первый и второй элементы И и элемент ИЛИ, выход которого соединен с вторым входом соответствующего блока индикации первой группы, а первый и второй входы — c выходами соответственно первого и второго элементов И первые входы которых подклю1394222

Составитель А.В.Карлов

Техред М.Дидык Корректор С. Черни

Редактор А.Ворович

Заказ 2222/45 Тираж 459 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Произволствеяно-полиграфическое предприятие, г, Ужгород, ул. Проектная, чены соответственно к прямому и инверсному выходам соответствующего элемента памяти, второй вход перво"

ro элемента И соединен с выходом инвертора, второй вход второго элемента И и вход инвертора подключены соответственно к I и К-входам соответствующего элемента памяти,