Устройство автоматического фазирования антенной решетки

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и повьшает точность фазирования . Каждый канал устр-ва содержит блок 1 сдвига фазы, активный модуль 2, излучатель 3, фазовый дискриминатор (ФД) 4, блок 5 суммирования, интегратор (и) 6, блок управления (БУ) 7,общий для всех канёлов. Введены блок 8 логич. управления, БУ 10 и блок 9 опорного сигнала, общий для всех каналов. В качестве И 6 исполь- -зован И со сбросом. По п. 2 ф-лы блок 1 содержит делитель мощности. два аттенюатора, сумматор мо1г;ности. По п. 3 БУ 10 содержит переключатель, два инвертора, два функциональных преобразователя. При равенстве фаз сигналов, поступающих на ФД 4, напряжение на его выходе равно нулю и система автоматич. фазирования, включающая блоки 1, 4, 5, 6, 8, 10, не влияет на работу устр-ва, т.к. с БУ 7 на один из входов блока 5 поступают нулевые сигналы. Если равенство фаз не выполняется, то на выходе ФД 4 вырабатывается сигнал ошибки в форме постоянного напряжения, пропорциональный разности фаз сигналов на выходе модуля 2 и блока 9. Сигнал. ошибки в блоке 5 дейс 1;вует на сигнальный вход БУ 10, к-рый формирует на управляюш х входах блока 1 сигналы управления. Под их действием блок 1, не изменяя амплитуды сигнала, поступающего на модуль 2, вносит фазовьй сдвиг, и фаза сигнала на выходе модуля 2 становится равной фазе сигнала блока 9. Блок 8 вырабатывает сигналы управления И 6 и БУ 10 на основании анализа уровня напряжения на выходе И 6. 2 з,.п. ф-лы, 2 ил. (Л со 4 Ю 00 00

СОЮЗ СОВЕТСНИК

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (gg 4 Н 01 3/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4037287/24-09 .(22) 18.03.86 (46) 07.05.88. Бюл. М -17 (71) Московский институт радиотехники, электроники и автоматики (72) С.В.Есин, В.И.Каганов и А.П.Пирхавка (53) 621.396.677(088.8) (56) Самойленко В.И., Шишов Ю.А. Управление фазированными антенными решетками — M. Радио и связь, 1983, с. 80, рис. 3.12. (54) УСТРОЙСТВО АВТОМАТИЧЕСКОГО ФАЗИРОВАНИЯ АНТЕННОЙ РЕШЕТКИ (57) Изобретение относится к радиотехнике и повышает точность фаэирования. Каждый канал устр-ва содержит блок 1 сдвига фазы, активный модуль

2, излучатель 3, фазовый дискриминатор (ФД) 4, блок 5 суммирования, интегратор (И) 6, блок управления (БУ)

7,общий для всех каналов. Введены блок 8 логич. управления, БУ 10 и блок 9 опорного сигнала, общий для всех каналов. В качестве И 6 исполь-зован И со сбросом. По и. 2 ф-лы блок 1 содержит делитель мощности, „„SU„„1394288 А 1 два аттенюатора, сумматор мощности.

По п. 3 БУ 10 содержит переключатель, два инвертора, два функциональных преобразователя. При равенстве фаз сигналов, поступающих на ФД 4, напряжение на его выходе равно нулю и система автоматич. фаэирования, включающая блоки 1, 4, 5, 6, 8, 10 не влияет на работу "устр-ва, т.к. с БУ

7 на один из входов блока 5 поступают нулевые сигналы. Если равенство фаз не выполняется, то на выходе ФД

4 вырабатывается сигнал ошибки в форме постоянного напряжения, пропорци" ональный разности фаз сигналов на выходе модуля 2 и блока 9. Сигнал. ошибки B блоке 5 действует на сиг- Ж нальный вход БУ 10, к-рый формирует на управляющих входах блока 1 сигналы управления. Пэд их действием ( блок 1, не изменяя амплитуды сигнала, Ю \ поступающего на модуль 2, вносит фазовый сдвиг, и фаза сигнала на выходе модуля 2 становится равной фазе > а сигнала блока 9. Блок 8 вырабатывает сигналы управления И 6 и БУ 10 на ос- 1 р новании анализа уровня напряжения на р выходе И 6. 2 s,.ï. ф-лы, 2 ил.

ОО

1394288

Изобретение относится к радиотехнике и предназначено для использования B антенных решетках с электрическим сканированием..

Цель изобретения — повышение точности фазирования.

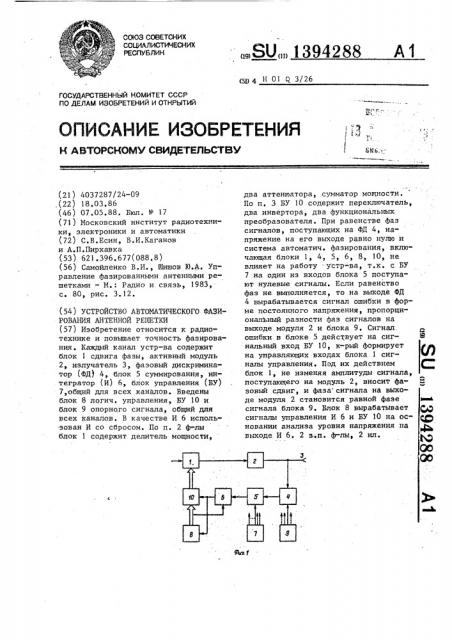

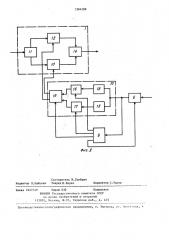

На фиг. 1 изображена структурная схема устройства автоматического фазирования антенной решетки (АР) для 10 одного кана9 на фиг.-2 - структурная схема блока сдвига фазы и второго блока управления.

Каждый канал устройства автомати ческого фазирования AP содержит блок

1 сдвига фазы, активный модуль 2, излучатель 3, фазовый дискриминатор

4, блок 5 суммирования, интегратор 6 со сбросом, первый блок 7 управле.ния общий для всех каналов, блок 8 логического управления, блок 9 опорного сигнала, общий для всех каналов, второй блок 10 управления. Блок 1 сдвига фазы содержит делитель 11 мощности, первый и второй аттенюаторы 25

12 и 13, сумматор 14 мощности."Второй блок 10 управления содержит переключа" тель 15, два инвертора 16 и 17, функциональные преобразойатели 18 и 19.

Устройство автоматического фазирования АР работает следующим образом.

Рассмотрим случай формирования на выходе канала сигнала с фазой, равной фазе опорного сигнала данного канала.

При этом, если выполняется условие равенства фаз сигналов, поступающих на входы фазового дискриминатора 4, то напряжение на его выходе равно нулю и система автоматического фазирования, включающая блоки 1, 4, 5, 6, 40

8, 10, не влияет на работу устройства, так как с первого блока 7 управления в этом случае на один из входов блока 5 суммирования поступают нулевые сигналы.

Если в результате действия любых дестабилизирующих факторов условие равенства фаз не выполняется, то на выходе фазового дискриминатора 4 вы- 50 рабатывается сигнал ошибки в форме постоянного напряжения, пропорциональный разности фаз сигналов на выходе активного модуля 2 и блока 9 опорного сигнала. Сигнал ошибки без изменения в блоке 5 суммирования действует на сигнальный вход второго блока 10 управления. Второй блок 10 управления с учетом сигнала, подаваемого с выхода интегратора 6 со сбросом, а также сигналов, поступающих с выхода блока 8 логического. управления на управляющий вход первого блока 10 управления, формирует на управляющих входах блока 1 сдвига фазы сигналы управления, под действием которых блок

1 сдвига фазы, не изменяя амплитуды сигнала, поступающего на вход активного модуля 2, вносит фазовый сдвиг такой величины, что фаза сигнала на выходе активного модуля 2 становится равной фазе сигнала блока 9 опорного сигнала. Блок 8 логического управления вырабатывает сигналы управления интегратором 6 со сбросом и вторым блоком 10 управления на основании анализа уровня напряжения на выходе интегратора 6 со сбросом. При достижении данным напряжением, подаваемым на вход блока 8 логического управления, некоторого предельного значения на управляющий вход интегратора 6 со сбросом поступает сигнал, обнуляющий

его выходное напряжение. Одновременно на управляющий вход второго блока

10 управления поступает сигнал, обеспечивающий в момент сброса напряжения на выходе интегратора 6 со сбросом неизменность фазового сдвига, вно-, ! симого блоком 1 сдвига фазы.

При формировании требуемого фазового распределения, отличного от равномерного, на один из входов блока 5 суммирования с второго блока 7 управ" ления поступает сигнал, равный по величине и обратный по знаку напряжению на выходе фазового дискриминатора 4, имеющему место при необходимой для получения требуемого фазового распределения разности фаз сигналов, поступающих на входы фазового дискриминатора 4.

Для поидержания постоянным затухания, вносимого блоком 1 сдвига фазы, напряжения U, и П„„, подаваемые на управляющие входы аттенюаторон 12 и

13, в случае линейной характеристики аттенюаторов должны изменяться по закону синуса и косинуса. Поэтому проходные характеристики функциональных преобразователей 18 и 19 задают следующими:

М" где 1Х,„„щ,, — выходные напряжения функциональных преобразователей;

1394288

Vì„ь,9 -- максимальные значения

<рп (6,19

U „, — выходной сигнал интегратора 6 со сбросом.

Блок 8 логического управления реализован на операционных усилителях и цифровых микросхемах либо с помощью микро ЭВМ и работает .следующим образом.

При подаче на управляющие входы инверторов 16 и 17 напряжения уровня логической единицы инверторы не инвертируют сигнал, поступающий на их сигнальные входы, а при подаче напря- 15 жения уровня логического нуля инвертируют этот сигнал. Кроме того, при поступлении на управляющий вход переключателя 15 напряжения уровня логической единицы выходы инверторов 16 и 17 подключены к управляющим входам аттенюаторов 13 и 12 соответственно, а при подаче напряжения уровня логического нуля — к управляющим входам аттенюаторов 12 и 13 соответственно. При подаче на управляющий вход интегратора 6 со сбросом напряжения уровня логической единицы его выходное напряжение обнуляется. Тогда при достижении J U„„,)=Ч„„„ на выходе блока 30

8 логического управления, соединенного с управляющим входом интегратора 6 со сбросом, вырабатывается логическая единица, а при /П„„„1 AhHgl логический ноль. . 35

Формула изобретения

1. Устройство автоматического фазирования антенной решетки, содержащее в каждом канале фазовый дискримина40 тор, выход которого подключен к первому входу сумматора, а первый входк выходу активного модуля, вход кото.рого соединен с выходом блока сдвига фазы, сигнальный вход которого является входом канала, выход сумматора подключен к сигнальному входу интегратора, второй вход сумматора подключен к соответствующему выходу первого блока управления, о т л и ч а ю щ е- 50 е с я тем, что, с целью повышения точности фаэирования, в каждый канал введен второй блок управления, выход которого через шину управления связан с управляющим входом блока сдвига фазы, первый вход второго блока управ" ления через шину данных связан с выходом введенного блока логического управления, в качестве интегратора использован интегратор со сбросом, управ ляющий вход которого подключен через шину данных к соответствующему выходу блока логического управления, выход интегратора со сбросом подключен к второму входу второго блока управления и к входу блока логического управления, второй вход фазового дискриминатора подключен к соответствующему выходу введенного блока опорного сигнала.

2. Устройство по п. 1, о т.л и— ч а ю щ е е с я тем, что блок сдвига фазы содержит делитель мощности, вход которого является сигнальным входом, первый выход подключен к входу первого аттенюатора, выход которого подключен к первому входу сумматора мощности, а второй выход делителя мощности подключен к входу второго аттенюатора, выход которого подключен к второму входу сумматора мощности, выход которого является выходом блока сдвига фазы, причем управляющие входы аттенюаторов являются управляющими входами блока сдвига фазы.

3. Устройство по п 1, о т л и ч аю щ е е с я тем, что второй блок управления содержит две цепочки, каждая из которых состоит из последовательно соединенных функционального преобразователя и управляемого.инвер- тора, выход каждого инвертора подключен к соответствующему входу переключателя, входы функциональных преобразователей объединены и являются вторьи входом второго блока управления, выходы переключателя — его выходами, при этом управляющие входы переключателя и инверторов являются первым входом второго блока управления.

1394288

Составитель И.Грубрин

Редактор Л.Зайцева Техред И.Верес Корректор С.Черни

Заказ 2227/49 Тираж 632 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4