Устройство для приема информации в частотном коде

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и телемеханике и может найти применение при построении систем приема информации в частотном коде в автоматизированных системах сбора, обработки и передачи информации с повышенными требованиями к скорости передачи и обработки информации. Цель изобретения - увеличение скорости приема за счет сокращения времени обработки сигналов. Устр-во содержит избирательные у-ли 1, нуль-органы 2, г-р 3 тактовых импульсов, счетчики 4, 6 и 7, коммутатор 5. В устр-во введены триггер 9, постоянное запоминающее устр-во (ПЗУ) 10 и дополнительный элемент И 11. В данном устр-ве резко сокращается область поиска двоичного кода информации, а следовательно, и время отработки принимаемых сигналов, 2 ил., 1 табл. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„13944 (5И 4 Н 04 L 27/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H ДBTOPCHGMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

{2 l ) 41545 l 81 24-09 (22) 02. 1 2. 86 (46) 07.0588. Бюл, Р 17 (7 t) Киевский политехнический инсти" тут им. 50"летия Великой Октябрьской социалистической революции (72) Ю. П. Жураковский, Л. И. Рай, В. П. Полторак и О. H Туранский (53) 621 .396.62(088.8) (56) Авторское свидетельство СССР

У 1185642, кл. Н 04 L 27/26, 1.5,10.85. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ В ЧАСТОТНОМ КОДЕ (57) Изобретение относится к электросвязи и телемеханике и может найти применение при построении систем приема информации в частотном коде в автоматизированных системах сбора, обработки и передачи информации с повышенными требованиями к скорости передачи и обработки информации, Цель изобретения — увеличение скорости приема за счет сокращения времени обработки сигналов. Устр-во содержит избирательные у-ли l, нуль-органы 2, г-р 3 тактовых импульсов, счетчики 4, 6 и 7, коммутатор 5. В устр-во введены триггер 9, постоянное запоминающее устр-во (ПЗУ) 10 и дополнительный элемент И 11. В данном устр-ве резко сокращается область поиска двоичного кода информации, а следовательно, н время отработки принимаемых сигналов.

2 ил., 1 табл.

1394458

Изобретение относится к электросвязи и телемеханике и может найти применение при построении систем прие. ма информации в частотном коде в ав5 томатизированных системах сбора, обработки и передачи информации с повышенными требованиями к скорости пе" редачи и обработки информации.

Цель изобретения — увеличение ско- 10 рости приема за счет сокращения времени обработки сигналов.

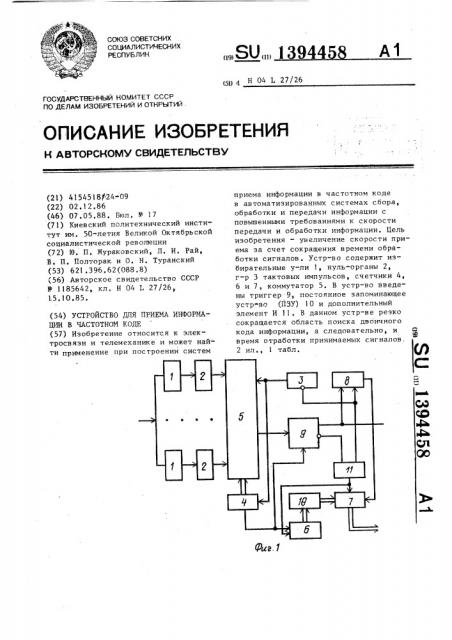

На фиг. 1 изображена структурная электрическая схема устройства для приема информации в частотном коде; 15 на фиг. 2 " временные диаграммы работы устройства.

В таблице представлены соответст" вия входных сигналов состояниям устройства и его отдельных блоков. 20

Устройство для приема информации в частотном коде содержит избирательные усилители 1, нуль-органы 2, генератор 3 тактовых импульсов (ГТИ), первый счетчик 4, коммутатор 5, вто- 25 рой 6 и третий 7 счетчики, элемент

И 8, триггер 9, постоянное запоминающее устройство (ПЗУ) 10 и дополнительный элемент И 11.

Устройство для приема информации в частотном коде работает следующим образом.

В исходном состоянии счетчики 4 и

6 и триггер 9 находятся в состоянии 35

"0", а счетчик 7 - в произвольном состоянии. Состояние других элементов схемы определяется состояниями названных блоков. Это исходное состояние устройства отражено в специаль- 40 ной строке таблицы соответствия состояний, где для примера выбрано ко- . личество частот и, применяемых в тракте передачи, равное пяти, Количество раз" решенных двухчастотных комбинаций 45 кода L равно числу сочетаний по два иэ и °

Так, например, для n = 5 L = 10, что и определяет число возможных состоящий устройства, а также число строк в таблице соответствия (колонка 1). Анализ входного многочастотно. го сигнала и принятие решения о наличии той или иной комбинации частот в ней осуществляют избирательными 55 усилителями 1, Дальнейшую обработку сигналов с выходов нуль-органов .2 проводят на высокой тактовой частоте, источником которой служит ГТИ 3.

Работу устройства можно разбить на два подцикла. В первом подцикле работы при помощи коммутатора 5 и первого счетчика 4 ведут поиск первой частоты принятой комбинации частот с целью установления подгруппы, к которой относится данная комбинация частот (колонки 3 и 4 таблицы), Во втором подцикле ведут поиск и идентификацию второй частоты внутри выбранной в первом подцикле подгруппы (колонки 3 - 5 таблицы). Во время обработки сигналов частотных комбинаций устройство меняет свои состояния, возможное число которых равно числу разрешенных частотных комбинаций, но устройство необязательно принимает эти все состояния. После появления на выходе коммутатора 5 второго сигнала логической "1", соответствующего обнаружению второй частоты из комбинации частот входного сигнала, сигналы информации снимают с выходов третьего счетчика 7. Очередной сигнал переполнения первого счетчика 4 с второго выхода возвращает устройство в исходное состдяние и подготавливает его к новому циклу работы, В колонке 3 таблицы перечислены сочетания частот входного сигнала с указанием на условно разбитые подгруппы частотных комбинаций. Каждое сочетание частот входного сигнала представляют в виде последовательности иэ а = 5 двоичных сигналов на выходе коммутатора 5 за время прохождения

n = 5 тактовых интервалов ГТИЗ (колонка 4 таблицы).

В колонке 5 таблицы представлены двоичные номера входных сигналов, соответствующие порядковым номерам

ВхОдных сигналов и Возможным сocтоя ниям устройства (колонка 2). В строках колонки 6 таблицы представлены

Ф коды, записанные в ячейках ПЗУ 10, где каждой подгруппе частотных комбинаций i (колонка 3) соответствует свой код D., Номера А; (адреса) ячеек ПЗУ 10, в которых записаны соответствующие коды D;, представлены в колонке 7. В строках колонки 8 представлены состояния S. второго счетчи1 ка 6 и совпадающие с ним адреса А .

I в соответствии с порядковбыи номерами подгрупп частотных комбинаций (колонка 3 таблицы), Входной сигнал с разрешенным сочетанием двух частот через избирательные усилители посту4

4458 з 139 пает на нуль-органы 2. При этом на выходах двух нуль-органов 2 появляются сигналы откликов на соответствующие частоты.

Сигналами генератора 3 переключают первый счетчик 4, изменяя значения сигналов на его выходах, и отпирают на часть каждого тактового периода выход коммутатора 5. Посредством этих сигналов выбирают текущий адрес входа коммутатора 5. Сигнал с соответствующего входа коммутатора 5 поступает на его выход, если на стробирующем входе присутствует "отпирающий" логический уровень ° Цикл анализа входного сигнала в устройстве состоит из п тактов. По окончании каждого цикла на втором выхбде первого счетчика 4 получают импульс переполнения, которым устанавливают

:триггер 9 и второй счетчик 6 в исход ные состояния. Таким образом к началу очередного цикла анализа первый 4 и второй 6 счетчики и триггер 9 находятся в состоянии логического "0".

При этом сигналом логического "0" на прямом выходе триггера 9 запирают элемент И 8.

Сигналом логической "1" с инверсного выхода триггера 9 отпирают дополнительный элемент И 11, при этом импульсы с выхода генератора.3 по" ступают на установочный вход третьего счетчика 7 и на счетный вход второго счетчика 6.

Сигналами с выходов второго счетчика 6 S. выбирают номер А ячейки !

ПЗУ 10 в которой хранится двоичный код D; равный первому коду В ., соответствующей подгруппы кодовых колебаний минус единица (колонки 5и 6 таблицы), В рассматриваемом примере в ячейке ПЗУ 10 с нулевым адресом (А = .= 000, колонка 7) записан код D равный 1-й кодовой комбинации В,=0000 (колонка 5) подгруппы "0" минус еди- ница, а именно 0 = 0000-0001=1111.

В ячейке ПЗУ 10 с 1-м адресом (А 001) записан код D. равный 1-й кодовой комбинации В„=0100 подгруппы "1" минус единица, а именно D,=0!00 -0001 =

= 0011 = В .

В последней ячейке ПЗУ, которых всего n-l, записан код l-й кодовой комбинации последней подгруппы минус единица. В рассматриваемом примере это будет код 0> равный первой и единственной кодовой комбинации В =!

001> подгруппы III минус единипа, а именно D = 1001 -0001=1000=8

Если при пошаговом (потактовом).

5 переключении коммутатора 5 на соответствующих его опрошенных входах обнаруживают сигналы логического "0", то триггер 9 остается в исходном состоянии. При этом сигналами с выхода открытого дополнительного элемента

И 11 осуществляют поочередную запись кодов D; из ячеек ПЗУ 10, где i=O, ...,(n-2) (колонка 6 таблицы), в третий счетчик 7, а также переключение

1б состояния второго счетчика 6 (колонка 8) и смену выбираемых адресов ПЗУ (колонка 7). Первым сигналом логической "1", обнаруженным на текущем опрошенном входе коммутатора 5 и пе2р реданным на его выход, переключают триггер 9. Таким образом происходит идентификация номера подгруппы, которой принадлежит сочетание частот входного сигнала (колонка 3 таблицы).

25 При этом сигналом логического "0" с инверсного выхода триггера 9 запрещают прохождение импульсов генератора 3 через дополнительный элемент

И 11 и прекращают переключение. второ1 го счетчика 6, а также фиксируют в третьем счетчике 7 последнюю записан-, ную из ячеек ПЗУ 10.кодовую комбинанацию D;, Сигнал логической "1" с прямого

ЗБ выхода триггера 9 разрешает прохождение импульсов генератора 3 через элементы И 8 на счетный вход третьего счетчика 7. После переключения триггера 9 и окончания текущего так40 тового импульса на выходе генератора

3 сигналом с его инверсного выхода, прошедшим через открытый элемент И 8, прибавляют единицу к содержимому тре"

"тьего счетчика 7. Полученный в тре4 тьем счетчике 7 код представляет со45 бой первую кодовую комбинацию в анализируемой подгруппе (таблица) и соответствует первому сочетанию частот входного сигнала в этой подгруппе. Поступление импульсов генератора 3 через открытый элемент И 8 на счетный вход третьего счетчика 7 продолжается до появления второй логической "1" на выходе коммутатора 5, соответству-..

55 ющей 2-й частоте из комбинации входного сигнала, Этим сигналом сбрасывают триггер 9 в состояние "0". На выходе третьего счетчика 7 присутствуют искомые сигналы информации в виде

1394458 двоичного кода, представляющие собой номер входного анализируемого сигнала (колонки 3 и 5 таблицы) и соответствующие анализируемому сочетанию частот входного сигнала. Считывание информации с выходов третьего счетчика 7 осуществляют посредством сигнала с выхода триггера 9.. Первый счетчик 4 продолжают переключать сигнала-10 ми с выхода генератора 3 до прохождения и-ro тактового импульса и появления сигнала на втором выходе ° Этим завершается цикл анализа и преобразования и начинается новый цикл ° 15

В предлагаемом устройстве резко сокращается область поиска двоичного кода информации, а следовательно, и время отработки принимаемых сигналов, Пусть, например, на вход устройст- 20 ва поступает сигнал с сочетанием частот 2 и 5 (колонка 3 таблицы и фиг . 2) .

Избирательными усилителями 1 выделяют сигналы с частотами f и f . Соответствующие нуль-органы 2 срабаты- 25 вают и на их выходах формируются сигналы логической "1" (фиг . 2а) . На выходах остальных нуль"органов 2 формируются сигналы логического "0", При этом на втором и пятом входах коммутатора 5 присутствуют сигналы логической "1", Очередной цикл анализа начинают после прохождения импульса переполнения с второго выхода первого счетчика 4 (фиг. 2б), Этим импульсом .устанавливают триггер 9 и второй

Р счетчик 6 в нулевое состояние (фиг. 2в и r соответственно). Выходными сигналами второго счетчика 6 выбирают адрес А,. ячейки ПЗУ 10 (фиг. 2д) . Сигналом логического "0" на прямом выходе триггера 9 (фиг, 2в) запирают элемент И 8, а сигналом логической "1" на инверсном выходе триггера 9 отпирают допол45 нительный элемент И 11. Импульсами с выхода генератора 3 (фиг, 2е) отпирают на половину тактового интервала выход коммутатора 5 (фиг, 2ж) и последовательно переключают состояния первого счетчика 4 (фиг. 2з) в течение всего цикла анализа. Состояния этого счетчика с соответствующими двоичными сигналами обозначены символа$ = 000» S = 001 S у= 010 $ =0!1у

$100. При этом в первом тактовом 55 интервале цикла анализа сигналами состояния S = 000 с выходов первого счетчика 4 подготавливают коммутатор 5 к опросу выхода первого нуль-органа 2, Первым в цикле тактовым импульсом (фиг. ?е) отпирают выход коммутатора

5. Сигнал логического "0", прошедший с первого входа коммутатора 5, че изменяет состояния триггера 9. Задним фронтом первого тактового импульса прибавляют единицу к содержимому первого счетчика 4, переводя его в состояние S, = 001 (фиг. 2з) и подготавливая тем самым коммутатор 5 к опросу выхода второго нуль-органа 2. Вторым тактовым импульсом (фиг. 2е) отпирают выход коммутатора 5 (фиг ° 2ж) и сигналом логической "1", прошедшим с второго его входа и соответствующим частоте fq во входном сигнале, устанавливают триггер 9 в состояние "1" (фиг, 2в).

Кроме того, в первом подцикле первым импульсом с инверсного выхода генератора 3 (фиг, 2и), прошедшим через открытый элемент И 8 (фиг. 2к), записывают в третий счетчик 7 из ячейки

ПЗУ 10 с адресом А „= 000 (фиг . 2д) сигналы кода А,= 000 (фиг, 2д) и кода D 1111 (фиг, 2л), По заднему фронту этого импульса фиксируют в третьем счетчик.е 7 код D = 111! и меняют состояние второго счетчика 6 на

$,= 001 (фиг . 2г), выбирая адрес

А,= S 001 ПЗУ .10 (фиг. 2д) выходными сигналами этого счетчика. Вторым импульсом с выхода дополнительного элемента И 11 (фиг. 2к) записывают в третий счетчик. 7 из ячейки ПЗУ 10 с адресом А,= 001 (фиг, 2д) сигналы кода D 0011 (фиг, 2л) . По заднему фронту этого импульса фиксируют в третьем счетчике 7 код D = 0011 (фиг. 2л) и прибавляют единицу к содержимому второго счетчика 6, меняя его состояние на $ =S + =001+001=010 (фиг. 2г) и выбирая адрес А S =0! 0 ячейки ПЗУ 10 (фиг. 2д) . На этом заканчивают Х подцикл анализа и начинают II подцикл.

Сигналом логической "1" с прямого выхода триггера 9 после его переключения (фиг. 2в) отпирают элемент

И 8 и запирают сигналом логического

"О" с инверсного выхода триггера 9 дополнительный элемент И l!. Палее каждым импульсом с выхода элемента

И 8 (фиг. 2м) прибавляют единицу к содержимому третьего счетчика 7 (фиг. 2л) да сброса в "0" григгepa (фиг, 2в) вторым импу.rs, ом r. выхопа

1394458

1О ия

Исходное состо яние

1 1 000 0000

1,2 коммутатора 5 (фиг. 2ж), соответствующим обнаруженной во входном сигнале частоте f . По заднему Фронту сигнала с прямого выхода триггера 9 (фиг. 2в) снимают сигналы В; информации с выходов третьего счетчика 7 в виде двоичной комбинации (колонка 5 таблицы и фиг. 2н), К содержимому третьего счетчика 7

D1= 0011 во.II подцикле три раза последовательно прибавляют единицу (фиг. 2л и м), получая сигналы В+=

= D, +1 = 0011 + 0001 = 0100 = 2 3; 15

— В + 1 — 0„+ 1 + 1 — 0100 + 00010101 = 2,4; В = В5+1 = Dq+1 +1 + 1

=0101+0001=0110 =>2,5, которые соответствуют сочетаниям частот 2,3; 2,4 и

2,5 (колонка 3 таблицы и фиг. 2о) . 20

Таким образом, в момент сброса триггера 9 вторым импульсом коммутатора 5, соответствующим второй обнаруженной частоте входного сигнала, 25 на выходах третьего счетчика 7 присутствуют сигналы информации В = 0110, соответствующие входному сочетанию частот 2,5.

Формула изобретения

Устройство для приема информации в. частотном коде, содержащее последовательно соединенные избирательные усилители и нуль-органы, последовательно соединенные генератор тактовых импульсов, первый счетчик и коммутатор, второй и третий счетчики и элемент И, причем входы всех избиратель:ных усилителей объединены и являются входом устройства, выходы нуль-органов соединены с вторыми входами коммутатора, первый выход генератора такто" вых импульсов подключен к третьему входу коммутатора, а первые входы второго и третьего счетчиков объединены, о т л и ч а ю щ е е с я тем, что, с целью увеличения скорости приема 5h счет сокращения времени обработки сигналов, в него введены триггер, постоянное запоминающее устройство и дополнительный элемент И, причем выход коммутатора соединен с первым входом триггера, прямой и инверсный выходы которого подключены к первым входам соответственно основного и дополнительного элементов И, второй выход генератора тактовых импульсов соединен с вторыми входами основного и дополнительного элементов И, выход которого подключен к первому входу третьего счетчика, второй выход церваго счетчика соединен с объединенными вторыми входами тригreра и второго счетчика, выходы которого соединены с входами постоянного запоминающего устройства, подключенного к вторым входам третьего счетчика, а выход основного элемента И соединен с третьим входом третьего счетчика.

Do l l l I Ao 000 Во!

1394458

1,3

10100 0001

Do!1 1 Аю=000 So=000

1,4

10110 0010

10001 0011

01100 0100

1,5

2,3

2,4 I 01010 0101 D, 0011

А =001 S 001

01001 0110

001!0 0111

2,5

3,4

П 1 0110 А =0!0 S 010

00101 000

3,5

4,5 III 00011 1001 D> 1000 Аз=01! Аз=О!1

1394458

Составитель И, Котиков

Техред Л.Сердюкова Корректор И.Николайчук

Редактор И. Дербак

Заказ 2240/57 Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4