Двухвходовое устройство приоритета

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет индикации номера канала, в котором время обслуживания запросов превышает наперед заданное , и отключения неисправного канала. Устройство обеспечивает последовательное обслуживание запро-. сов в порядке их поступления при условии, что время обслуживания не превышает наперед заданное. Контроль времени обслуживания запросов осуществляется таймерами 11, 12, реализованными , например, на двоично-десятичных счетчиках. При превышении времени обслуживания наперед заданного таймеры 11 и (или) 12 выдают сигналы , устанавливаклще соответственно триггеры 1б, 17 в единичное состояние , при этом на вцходных шинах 18, 19 индикации устанавливается потенциал логической единицы, указывающий на неисправность канала, а триггеры 1 и (или) 2 устанавливаются через, элементы И 14, 15 в исходное единичное состояние, тем самым отключают неисправилй канал и представляют возможность обслуживания запроса другого канала. 1 ил. с (Л со со со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„Л0„„1 9 143 Ai (su .1 С 06 F 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H д BTOPCXOMV СВИДЕТЕЛЬСТВУ

:В

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

fl0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4151902/24-24 (22) 25. 11.86 (46) 15.05.88. Бюл. 9 18 (71) Харьковский филиал Специального конструкторского бюро автоматизированных систем управления мясной и молочной промышленности (72) В.И. Прахов, Л.M. Пшисуха, А.П. Семиноженко и В.Ф. Кобец (53) 681.325 (088.8 ) (56) Электроника, 1983, 9 20, т. 56 (США), с. 81"83.

Авторское свидетельство СССР

Ф 1187166, кл. G 06 F 9/46, 1984. (54) ДВУХВХОДОВОЕ УСТРОЙСТВО ПРИОРИТЕТА (57) Изобретение относится к цифровой вычислительной технике. Цель изобретения — расширение функциональных возможностей за счет индикации номера канала, в котором время обслуживания запросов превышает наперед заданное, и отключения неисправного канала. Устройство обеспечивает последовательное обслуживание запросов в порядке их поступления при условии, что время обслуживания не превышает наперед заданное. Контроль времени обслуживания запросов осуществляется таймерами 11, 12, реализованными, например, на двоично-.десятичных счетчиках. При превышении времени обслуживания наперед заданного таймеры 11 и (или) 12 выдают сигналы, устанавливающие соответственно триггеры 16; 17 в единичное состояние, при этом на вцходных шинах 18, 19 индикации устанавливается потенциал логической единицы, указывающий на неисправность канала, а триггеры 1 и (или) 2 устанавливаются через. элементы И 14, 15 в исходное единичное состояние, тем самым отключают неисправный канал и представляют возможность обслуживания запроса другого канала. 1 ил.

1396143

Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках управления устройствами общего пользования, 5 например в блоках управления оперев тивиой памятью.

Целью изобретения является расширение функциональных возможностей за счет индикации номера канала, В котором время обслуживания запросов превышает наперед заданное, и Отключения неисправного канала.

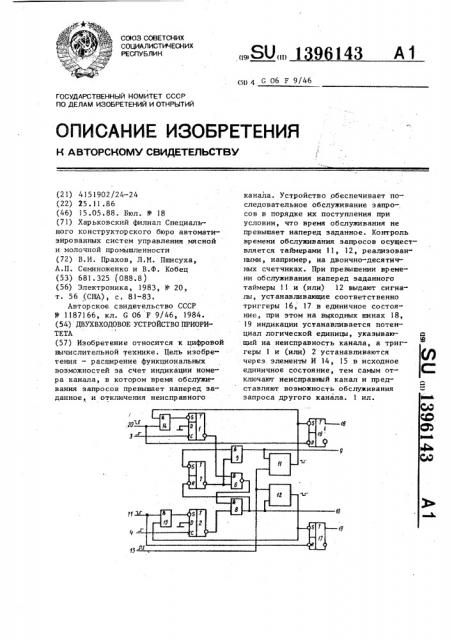

На чертеже представлена блок-схема двухвходового устройства приоритета.

Устройство содержит 13-триггеры

1 и 2, входы 3 и 4 - апро сов, элемен";: ы

N 5 „H-НЕ 6, RS-триггер 7, элемент

И 8, выходы 9 и 10 управления режимом, таймеры 11 и 12, вход .13 импульсов опорной частоты, элементы И 14 и

15, RS — триггеры 16 и 17 „выхопы ° 8 и 19 индикации и вхсды 20 и 2 1 с6роса. 25

Устройство работает слецующим . образом.

После включения питания и подачи импульсов сброса на Вхоцы 20 и 21. триггеры 1 и 2 уста..-..авливаются в еди- 30 яичное, а триггеры 16 и 17 — н нуле— вое состояния, при которых на выхо,цах 9, 10, 18 и 19 устройства фиксируется по-,åíöèàë логического нуля,а. таймеры 11 и 12 переводятся в исходное нулевое состояние с потенциалом логической единицы на в".»ходах, причем потенциал логического нуля с инверсных Выходов триггеров 1 и 2 воэ,цействует на входы триггера 7 и yqep- 40 живает последний в состоянии, соответствующем наличию потенциала логической единицы одновременно на прямом и инверсном выхоцах, Сигналы запросов на входах 3 и 4 своим фронтом устанавливают триггеры 1 и 2 в нулевое состояние °

При одновременном переключении триггеров 1 и 2 в нулевое состояние потенциал логической единицы с инверсных выходов триггеров 1 и 7 воздействует на входы элемента И-НЕ 6, с выхода которого потенциал логического нуля блокирует прохождение сигналов с инверсното выхода триггера

2 на ВыхОд 10 через элемент И8 и поддерживает в нулевом состоянии тригI ep 7 по R-входу, причем сигнал с инверсного выхода триггера 1 передается на выход 9 через элемент И5, что соответствует приоритетному обслуживанию запроса на входе 3.

Импульс сброса на входе 20 устанавливает триггер 1 в единичное состояние через элемент И14 и определяет момент окончания обслуживания запроса первого канала, при этом на выходе 9 фиксируется потенциал логическоro нуля, а потенциал логической единицы на выходе элемента И-НЕ

6 разрешает прохождение сигнала с инверсного выхода триггера 2 через элемент И8 на выход 10 что соответствует обслуживанию запроса на выходе 4, причeм триггер 7 переводится

В единичное состояние и потенциалом логического нуля на инверсном выходе блокирует прохождение сигналов с выхода триггера 1 через элемент И5 на выход 9 и поддерживает на выходе элемента И вЂ” НЕ 6 потенциал логической едипи д.

Импульс сброса на входе 21 устанавливает триггер 2 в единичное состояние через элемент И15 и определяет момент окончания обслужмвания запроса Второго канала, при этом на выходе 10 фиксируется потенциал логического нуля, а на инверсном выходе триггера 7 — потенциал логической единицы, разрешающий прохождение сигнала с инверсного выхода триггера 1 через элемент И5 на выход 9, что обеспечивает режим последовательного обслуживания запросов в порядке их поступления.

Время обслуживания запросов контролируется таймерами 11 и 12.

При обслуживании запросов потенциал логической единицы на выходах

9 и 10 воздействует на установочные входы таймеров 11 и 1? и переводит их в режим счета импульсов опорной частоты на входе 13. Если время обслуживания запросов превышает время, необходимое для заполнения таймеров

11 и 12, с выходов последних сигнал переполнения устанавливает соответственно триггеры 1 и 16 и триггеры

2 и 17 в единичное состояние, при-< чем установка в единичное состояние триггеров 16 и 17 соответствует появлению потенциала логической единицы соответственно на выходах 18 и

19 индикации номера неисправного

i 396143

Составитель Г. Пономарева

Редактор А. Лежнина Техред М.Дидык Корректор М. Шароши

Заказ 2496/50 тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 канала, а установка в единичное сос тояние одного из триггеров 1 или 2 обуславливает отключение этого канала и возможность обслуживания устройством запроса другого канала.

Сигналы сброса на входах 20 и 21 устанавливают соответственно триггеры

16 и 17 в исходное состояние.

Фор мула изобрет ения 10

Двухвходовое устройство приоритета, содержащее первый и второй триггеры, информационные входы которых соединены с шиной нулевого потенциа- 15 ла устройства, С-входы первого и второго триггеров подключены соответственно к первому и второму входам запросов устройства, S-входы первого и второго триггеров соединены с выхо- 20 дами соответственно первого и второго элементов И, инверсный выход первого триггера соединен с первыми входами третьего элемента Ии элемента

И-НЕ, выход элемента И-НЕ соединен с первым входом четвертого элемента

И, второй вход которого соединен с инверсным выходом второго триггера, первый вход первого элемента И подключен к первому входу сброса устрой- 30 ства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет индикации номера канала, в котором время обслуживания запросов превышает наперед заданное, и отключения неисправного канала, оно содержит три триггера, первый и второй таймеры, синхровходы которых подключены к входу импульсов опорной частоты устройства, установочные входы первого и второго таймеров соединены с выходами соответственно третьего и четвертого элементов И и подключены к первому и второму выходам управления режимом устройства соответственно, а выходы соединены с вторыми входами соответственно первого и второго элементов И и S-входами третьего и четвертого триггеров, прямые выходы которых подключены к первому и второму выходам индикации устройства соответственно, R-входы третьего и четвертого триггеров соединены с первыми входами соответственно первого и второго элементов И и подключены к первому и второму входам сброса устройства соответственно, S-вход пятого триггера соединен с инверсным выходом первого .триггера, R-вход пятого триггера

, соединен с выходом четвертого элемен,та И, а инверсный выход соединен с вторыми выходами элемента И-НЕ и третьего элемента И.