Преобразователь двоичного кода в двоично-десятичный код угловых единиц

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СО1.1ИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) Н 03 М 7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ДBTOPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 970354 (21) 3902355/24-24 (22) 05.06.85 (46) 15.05.88. Бюл. Р 18 (72) С. Б.Барсегян (53) 681.325 (088.8) (56) Авторское свидетельство СССР и 970354, кл. G 06 F 5/02, 1980, (54) (57) 1 .ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО

КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД УГЛОВЫХ

ЕДИНИЦ по авт. св. 9 970354, о т л и— ч ающий с я тем, что, с целью повышения быстродействия, в него введены третий элемент И, дополнительный двоичньп» счетчик и блок управления преобразованием старших разрядов входного кода причем первый выход блока управления преобразованием старших разрядов входного кода, соединен с суммирующим входом двоично.десятичного счетчика, второй выход—

Р с вычитающим входом старших разрядов двоичного счетчика и входом обнуления дополнительного двоичного счетчика, счетный вход которого и тактовый вход блока управления преобразованием старших разрядов входного кода подключены к выходу третьего элемента И, первый и второй входы которого соединены соответственно с выходом дешиф-

ÄÄSUÄÄ 1396280 А 2 ратора старших разрядов и выходом ге»»ератора импульсов, выход дополнительного двоичного счетчика подключен

K" информационному входу блока управления преобразованием старших разрядов входного кода.

2. Преобразователь по п.1, о т л и ч а ю шийся тем, что блок управления преобразованием старших разрядов. входного кода содержит дешифратор, два элемента ИЛИ и делитель частоты импульсов, состоящий из трехразрпдного двоичного счетчика и элемент И, причем стробирующий и информационньп» входы дешифратора подключены соответственно к тактовому и информационному входам блока, выходы первых четырех разрядов дешифратора соединены с входами первого элемента

ИЛИ, вьгходы пятого и шестого разрядов дешифратора подключены к входам второго элемента HJIH выходы первого и второго элементов, ИЛИ, седьмого и восьмого разрядов дешифратора и делителя частоты импульсов подключены к первому выходу блока, второй выход которого соединен с выходом десятого разряда дешифратора, выход девятого разряда которого подключен к входу делителя частоты импульсов, 1396280

Изобретение относится к автоматике и цифровой вычислительной технике, может быть использовано при пост оении преобразователей в измериP

5 тельных и управляющих системах и является дополнительным к авт. св.

Ф 970354.

Цель изобретения — повышение быстродействия преобразователя.

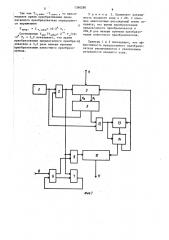

На фиг.l приведена. структурная. схема преобразователя; на фиг.2— ! пример исполнения Аукнциональных схем блоков 14 и 10.

Преобразователь содержит (фиг.l) генератор 1 импульсов, первый элемент И 2, двоичный счетчик 3, информационный вход 4, дешифратор 5, сумматор 6, регистр 7, вход 8 задания константы, второй элемент И 9, двоично-десятичный счетчик 10 выход 11, третий элемент И 12, дополнительный двоичный счетчик 13, блок 14 управ1 ления преобразованием старших разрядов входного кода. 25

Функциональные схемы блоков 14 и

l 0 для одного варианта исполнения (фиг.2) содержат дешифратор 15 им-. пульсов, двух- и четырех входовые элементы ИЛИ 16 и 17, делитель 18 частоты импульсов, содержащий элемент И 19 и трехразрядный двоичный счетчик 20, а также блок 10 — четыре двоично-десятичных 21, два двоичношестеричных 22 и один двоичный 23 счетчика импульсов и четыре двухвходовых элемента ИЛИ 24.

Преобразователь работает следующим образом.

В начале цикла преобразования производится обнуление регистра 7, дво40 ично-десятичного счетчика 10, дополнительного двоичного счетчика 13 (зти цепи не показаны) и по информационному входу 4 в двоичный счетчик-регистр 3 записывается входное число N 45 в виде и-разрядного двоичного кода угла. Старшие п, разрядов двоичного счетчика 3, имеющие преимущественно веса, соответствующие целым градусам, минутам и секундам части N,, входно 50 го кода N и младшие N > разрядов это.го же счетчика 3, имеющие веса с дробными частями секунд и образующие остальную часть N входного числа N, имеют раздельные счетные входы. При 55 этом 11 = 11 „+ Б и и = и, + и .

Если код младших п разрядов отличается от нуля, то с первого выхода дешифратора 5 поступает разрешающий потенциал на второй вход элемента И 2 и импульсы генератора I, поступающие на первый вход элемента И 2, пропускаются через элемент И 2 и поступают на вход вычитания младших разрядов двоичного счетчика 3, на первый вход элемента И 9 и на тактовый вход регистра 7.

Замкнутые в кольцо сумматор 6 и регистр 7 представляют собой накапливающийся сумматор, который на каждый тактовый импульс добавляет к записанному в регистре 7 двоичному числу целочисленную константу С, сформированную на входе 8. Значение константы С (двоичного эквивалента веса младшего разряда входного кода И ) выбрано из условия исключения набегающей ошибки и обеспечивает формирование переноса на выходе сумматора

6 в моменты времени, когда частичная сумма дробных частот кода N< равна целой угловой единице — весу младшего разряда кода выходного двоично-десятичного счетчика 10. Сигнал переноса, возникающий на выходе сумматора

6, через некоторое число тактов заполнения сумматора 6 разрешает прохождение импульсов через элемент И 9 на суммирующий вход двоично-десятичного счетчика 10.

В то же время с поступлением каждого импульса генератора с выхода элемента И 2 на вход вычитания младших разрядов двоичного счетчика 3 код на выходе младших разрядов счет- чика 3 уменьшается на единицу. После прохождения импульсов младшие разряды регистра-счетчика 3 приходят в нулевое состояние и первым выходом дешифратора 5 снимается разрешение на входе и элементе. И 2. Этим завершается преобразование кода младших разрядов входного числа в унитарный код — число импульсов N умножение его на константу С и преобразование целой части этого произведения в выходной двоично-десятичный код угла.

Время преобразования числа N< записанного в младших разрядах, определяется выражением

Т„ = 11 - Гг = 2 T (1) где Т . — период повторения импульсов генератора 1.

Одновременно с началом преобразования младших разрядов кода входного

280 4 ступает на счетный вход декады единиц секунд двоично-десятичного счетчика (0,25х4 = 1) ° Импульс десятого такта дешифратора с выхода блока 14 поступает на вход обнуления двоичного счетчика 13 и одновременно на вход вычитания старших и, разрядов двоичного счетчика 3. Таким образом, цикл работы блока 14 содержит десять тактов и за каждый цикл его работы код в старших разрядах двоичного счетчика 3 уменьшается на единицу. После

N, циклов работы блока 14 и, разря" дов счетчика-регистра 3 приходит в нулевое состояние и дешифратор 5 своим вторым выходом снимает разрешение на входе элемента И 12. Этим завершается преобразование старших п» разрядов входного ко а, Время преобразования числа N „ записанного в старших разрядах, определяется выражением ь = IОN Т = 102 Тгв (2) . где 10 - число тактов одного цикла работы блока 14.

1396

3 числа Nz начинается преобразование числа N, записанного в старших п разрядах двоичного счетчика 3, С появлением разрешающего потенциала на втором выходе дешифратора 5 импульсы генератора 1 через элемент И 12 начинают поступать на счетный вход дополнительного счетчика 13, выходы которого подключены к входам блока 14 уп10 равления преобразованием старших разрядов. При заданной разрядности п входного кода угла структура блока 14 зависит от разделения разрядов входного кода на старшие и, и младшие и >

2 15 и определяется количеством единиц в каждом десятичном представлении веса младшего разряда числа N,. Для простоты рассмотрения на фиг.2 приведена функциональная схема блока 14 для конкретного случая и, = 9 при кон20 кретной структуре двоично-десятичного счетчика 10, выполненного для выходного кода градусы — минуты — секунды. Весу младшего разряда числа Н1 при п „ = 9 соответствует десятичное представление угла 42, Р, 25, поэтому цикл работы блока 14 выбирается равнь»м десяти тактам (4+2+1+1 тактокругления + такт сброса) генератора импульсов. Основным элементом блока

14 (фиг.2) является дешифратор импульсов, на тактовый вход которого поступают импульсы генератора с выхода элемента И 12, а на информационные входы поступают выходы дополнительно- 35 го двоичного счетчика 13. Импульсы первых четырех тактов дешифратора с выхода четырехвходового элемента ИЛИ блока 14 через соответствукиций элемент ИЛИ блока 10 поступают на сум- 40 мирующий вход секстады десятков минут двоично-десятичного счетчика. Им- . пульсы двух следующих тактов поступают на счетный вход декады единиц минут двоично-десятичного счетчика. Им- 45 пульсы седьмого и восьмого тактов дешифратора через элементы ИЛИ блока 10 .поступают на счетные входы секстады десятков секунд и декады секунд двоично-десятичного счетчика. Импульс 50 девятого такта, которому приписано значение 0,25, поступает на вход делителя частоты импульсов, состоящего из трехразрядного двоичного счетчика и элемента И. После каждого четверто-,55 го цикла работы дешифратора на выходе элемента И появляется тактовый импульс, который обнуляет трехразрядный двоичный счетчик и одновременно поТак как процесс преобразования старших п, и младших п разрядов входного кода осуществляется параллельно, то общее время преобразова- ния Т> входного числа определяется не суммой Т и Т „, а большим значе» г нием одного из них.

Оценим для двух значений разрядности входного кода п = 14 и п = 20 отношение времени преобразования известного и предлагаемого преобразователей.

Пример 1. Максимальное время преобразования известного преобразователя при разрядности входного двоичного кода угла n = 14 определяется выражением

Максимальное время преобразования старших п разрядов предлагаемого преобразователя для данного случая построения его схемы при n = 9 определяется выражением (2)

Т„„, „,= IO 2 .Т = 10 -2 Т„.

При этом максимальное время преобразования младших п =п=п; — 14-9 5 разрядов определяется выражением (1) » г

Т"г макс 2 т„= 2 тг

1396280

Так как Т „„„„, Т, „, то макси,мальное время преобразования пред лагаемого преобразователя определяется выражением

Т дррд Т к мфкс 10 2 Т °

Соотношение Т„ /Т„, „ 2 . Т /1О»

14

«2 Тг 3,2. показывает, что время преобразования предлагаемого преобра-10 зователя в 3,2 раза меньше времени преобразования известного преобразо: вателя.

Л р и м е р 2. Принимает разрядность входного кода и = 20. С помощью аналогичных рассуждений можно показать, что время преобразования предлагаемого преобразователя в

204,8 раз меньше времени преобразования известного преобразователя.

Примеры 1 и 2 показывают, что эффективность предлагаемого преобразователя увеличивается с увеличением разрядности входного кода.

1396280

Корректор М. Поко

Техред Л.Сердюкова

Редактор Е.Копча

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 1 3035 у Москва, Ж-35, Раушская наб., д. 4/5

Заказ 2504/57

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная, 4