Вероятностный мажоритарный декодер

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Его использование в системах передачи и обработки информации , организованной в пакеты, позволяет повысить достоверность декодирования при приеме дискретных сигналов из канала связи с переменными параметрами . Вероятностный мажоритарный декодер содержит коммутаторы 1, 2, регистры 4, 5, Лормирователь 7 проверок и сумматор 9. Введение коммутатора 3, регистра 6, формирователя 8 проверок, сумматора 10, генератора 11 постоянного кода, компаратора 12, блока 13 сумматоров, блока 14 элементов НЕ, вычислителей 15, 16 оценки вероятности,вычислителя 17 веса проверок, элемента 18 неравнозначности , элемента НЕ 19, элементов И 20,. 21 и счетчиков 22, 23 обеспечивает декодирование с учетом вычисляемых надежностей символов, а также определение состояния канала связи и использование этой оценки для взвешенного декодирования. 3 ип. S сл

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51)4 Н 03 И 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4169573/24-24 (22) 17.1),86 (46) 15.05.88. Вюл. В 18 (72) С.Л.Нортной, В.В.Овчинников, А.С.Данилин и А.В.Филимонов (53) 621.391.25:681.325 (088.8) .(56) Зарубежная радиоэлектроника, 1986, 9 7, с. 3-36.

Зарубежная радиоэлектроника, 1985, Р 7, с. 16, рис. 6. (54) ВЕРОЯТНОСТНЬП ИАНОРИТАРНЫЙ ДЕ-.

КОДЕР (57) Изобретение относится к вычислительной технике. его использование в системах передачи и обработки информации, организованной в пакеты, позволяет повысить достоверность декодирования при приеме дискретных сигна„„SU„„1396282 A 1 лов из канала связи с переменными параметрами, Вероятностный мажоритарный декодер содержит коммутаторы 1, 2, регистры 4, 5, Формирователь 7 проверок и сумматор 9. Введение коммутатора 3, регистра 6, Формирователя 8 проверок, сумматора 10, генератора 11 постоянного кода, компаратора 12, блока 13 сумматоров, блока 14 элементов НЕ, вычислителей 15, 16 оценки вероятности, вычислителя 17 веса проверок, элемента 18 неравнозначности, элемента НЕ 19, элементов И 20, .

21 и счетчиков 22, 23 обеспечивает декодирование с учетом вычисляемых надежностей символов, а также опредее0 ление состояния канала связи и использование этой оценки для взвешенного декодирования. 3 im.

1396282

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки информации, органиэованной в пакеты. Эта информация обрабатывается с учетом вероятностных характеристик каналов передачи информации, в частности каналов, свойства которых меняются во времени. В первом приближе- 10 нии такой канал может быть охарактеризован двумя состояниями — хорошее (х) и плохое (и) и называется соответственно х-каналом и п-каналом.

Цель изобретения — повышение достоверности декодирования при приеме дискретных сигналов из канала связи с переменными параметрами.

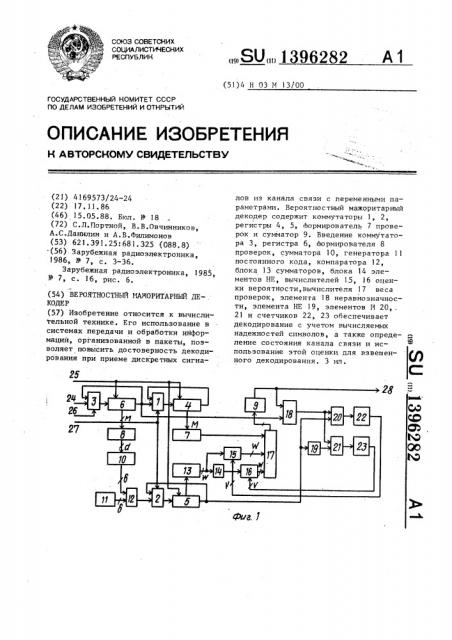

На фиг. 1 изображена функциональная схема вероятностного мажоритарного декодера; на фиг. 2 — временные диаграммы, поясняющие его работу; на фиг. 3 — модель канала передачи с переменными параметрами.

Вероятностный мажоритарный декодер 25 содержит первый 1, второй 2 и третий

3 коммутаторы, первый 4, второй 5 и третий 6 регистры, первый 7 и второй

8 формирователи проверок, первый 9 и второй 10 сумматоры, генератор 11 постоянного кода, компаратор 12, блок 13 сумматоров, блок 14 элементов НЕ, nepahN 15 и второй 16 вычислители оценки вероятности, вычислитель 17 веса проверок, элемент 18 не35 равнозначности, элемент НЕ 19, первый 20 и второй 21 элементы И, первый 22 и второй 23 счетчики. На фиг. 1 обозначены информационный 24 и тактовый 25 входы, первый 26 и вто- 40 рой 27 управляющие входы и выход 28. . Вероятностный мажоритарный декодер предназначен для обработки информации, закодированной циклическим кодом {и, k, d) с параметрами: и — длина кода; k — количество информационных символов; d — - число разделенных проверок (расстояние Хемминга).

Формирователь 7(8) проверок служит для формирования "жестких" значений проверок и выполнен на d (m;)-входа- 50 вых сумматорах по модулю два, причем

K. m = И, m — число символов, вхо<

1=1 дящих в i-ю разделенную проверку {на фиг. 1 указаны размерности входов и выходов сооветствующих блоков).

Первый сумматор 9 является сумматором по модулю два. Второй сумматор

10 является двоичным сумматором, число выходов которого Ю= 11 1og d Г, где

) Х I — наименьшее большее целое, т.е. целовая часть числа У. плюс I.

Генератор 11 постоянного кода— это генератор -разрядного числа 2 (значение порога в двоичной форме), содержащий генератор логической I" и генератор логического "0", выходы которых соединены с соответствующими выходами генератора 11 число которых

dl (jogged.

Блок 13 сумматоров служит для определения числа надежных символов во всех d проверках и выполнен íà d (m«)-входовых полных сумматорах, Число выходов i-го сумматора W;= Ilog m.Ã, общее число выходов блока 13 И =

Ы

=; W„..

> t

Каждый из вычислителей 15-17 выполнен íà d программируемых постоянных запоминающих устройствах (ППЗУ).

В каждом -м ППЗУ первого вычислителя 15 по сигналу 1 . E (0,2 -1 ) с бло%; ка 13 и сигналу Р „ co счетчика 22 вычисляется оценка и п

Я (1 2Р )

В каждом i-м ППЗУ второго вычислителя 16 по сигналу 1,. с блока 14 и сигналу Р„ со счетчика 23 вычисляется оценка — 2гп) где m — число символов в i-й проверке;

1 — число символов в i-й провер1 ке, соответствующей Х-каналу °

По этим оценкам в каждом i-м ППЗУ вычислителя 17 вычисляется .вес Q i-й проверки и и

+ х П =11 — — —-х р где N = +I или -1 — сигнал на первом (знаковом) входе

i-ro ППЗУ вычислителя 17 (с . формирователя 7).

Вероятностный мажоритарный декодер работает следующим образом.

На вход 24 декодера поступает блок информации из и бит, где n — длина укаэанного кода (и, а, d). Коммутатор 3 по команде первого управляющего сигнала (фиг.2а) переписывает эту

1396282 информацию в течение и тактов (первый цикл) в регистр 6 длиной п. После ,чего коммутатор 3 прекращает поступление информационного потока в декодер и переключается на циркуляцию в

5 течение следующих п тактов информации, записанной в регистре 6. Из циркулирующих символов для каждого символа во втором формирователе 8 форми-10 руется d разделенных проверок по m символов в i-й проверке, i = l d.

Затем эти d проверок складываются во втором сумматоре 10 и результат сло--. жения (значение суммы проверки для

i-ro символа) сравнивается в компараторе 12 с заданным значением 2 порога из генератора 1) постоянного кода.

Если результат сравнения меньше Z то считается, что в данном тактовом интервале канал находится в х-состоянии, в противном случае канал находится в п-состоянии. Этот результат сравнения является оценкой качества канала (х или и). Далее эти символы будут называться символами надежности.

В следующие п тактов (2п+1,...,3n)— второй цикл — первоначальная информация из регистра 6 по второму управляющему сигналу (фиг.2б) на первом

30 коммутаторе 1 переписывается в первый регистр 4, а символы надежности через второй коммутатор 2 заполняют второй регистр 5.

Далее в тактах (Зп+1,...,4п) — тре-З5 тий цикл — осуществляется одновременно циркуляция соответствующей инфор мации в регистрах 4 и 5, где формируются те же жесткие значения проверок в первом формирователе 7 и определен- 40 ные числа 1 надежных символов. В вычислителе 17 получается значение веса каждой проверки. Эти значения складываются в первом сумматоре 9, с выхода которого получаются декодированные символы, поступающие на выход

28 декодера (фиг.3в). Эти декодированные символы сравниваются с символами поступающей информации (с выхода. третьего регистра 6), в результа- 50 те чего на выходе элемента 18 появляются значения о»пибок декодирования-.

Полученные значения ошибок и надежности символов (с выхода второго регистра 5) используются для оценки 55 вероятности состояния канала. Для того, чтобы определить, в каком состоянии находится канал (x — хорошем или и — плохом) в течение прохождения через него N блоков декодированной информации, счетчики 22 и 23 подсчитывают числа исправленных декодером ошибок за зто время ° Число разрядов в каждом счетчике равно 4 =Ъоц «(пМ)Г

; перед декодированием счетчики обнуляются. Полученные оценки значения вероятности того, что канал находится в хорошем (Р ) или плохом (Р „) состоянии, используются в вычислителях 15 и 16 для дальнейшего определения веса проверок, Покажем, что в рассматриваемом декодере обеспечивается повышение достоверности декодирования при приеме дискретных сигналов из канала связи с переменными параметрами.

Для определенности примем модель канала Гильберта-Эллиота (фиг.3), которьп» имеет два состояния: хорошее (х) и плохое (п). Последовательность состояний канала образует простую марковскую цепь с вероятностями пе- реходов Р„„ и P „„ и вероятностями того, что канал останется в данном состоянии, равном l — Р„„и 1 — Р„„. В каждом из состояний канал является двоичным симметричнь»м объектом с вероятностями ошибки Р„ и Р „. Реальные каналы, например, с медленными зами- раниями, близки по своим свойствам к модели Гильберта-Эллиота. Многочисленными расчетами показано, что при известном состоянии канала путем взвешивания проверок, как в предлагаемом декодере, обеспечивается энергетический выигрьпп кодирования (ЭВК) около 5 дБ для канала с медленными замираниями. Кроме того, этот алгоритм является алгоритмом декодирования по максимуму правдоподобия .

Предлагаемь»й вероятностньп» мажоритарньп» декодер позволяет извлечь информацию о состоянии канала из самого процесса,цекодирования. Расчеты моделирования на ЭВМ показывают, что для релеевого канала ЭВК составляет около 4 дБ, что эквивалентно уменьшению ошибки декодирования. Уменьшение выигрыша с 5 до 4 дБ обуславливается потерями в оценке состояния канала, однако данньп» декодер не требует дополнительного очень сложного блока оценки канала.

Таким образом, предлагаемый вероятностный мажоритарный декодер обеспечивает для канала связи с перемен1396282 ными параметрами увеличение энергети ческого выигрыша кодирования. формула изобретения

Вероятностный мажоритарный декодер, содержащий первый сумматор, первый и второй коммутаторы, выход каждого из которых соединен с информа- g ционным входом одноименно го ре гис тра, .параллельные выходы первого регистра подключены к соответствующим входам, первого формирователя проверок, отличающийся тем, что, с це1 ! лью повышения достоверности декодирования при приеме дискретных сигналов из канала связи с переменными па раметрами, в декодер введены второй сумматор, второй формирователь прове- 2О ок, генератор постоянного кода, комраратор блок сумматоров, блок элементов НЕ, первый и второй вычислители оценки вероятности, вычислитель еса проверок, первый и второй счетики, элемент неравнозначности, элемент НЕ, первый и второй элементы И, гре ий регистр и третий коммутатор, первый информационный и управляющий фходы которого являются соответственно информационным и первым управЛяющим входами декодера, выход третьего коммутатора соединен с информационным входом третьего регистра, последовательный выход которого подключен к первому входу элемента неравно- З5 значности, второму информационному цходу третьего коммутатора и первому информационному входу первого коммутатора, управляющий вход которого дбъединен с управляющим входом вто40 рого коммутатора и является. вторым управляющим входом декодера, тактовые входы первого — третьего регистров объединены и являются тактовым входом декодера, параллельные выходы третьего регистра подключены к входам второго формирователя проверок, выходы которого соединены с входами второго сумматора, выходы которого и выходы генератора постоянного кода подключены соответственно к первым и вторым входам компаратора, выход которого соединен с первым информационным входом второго коммутатора, последовательный выход первого регистра соединен с вторым информационным входом первого коммутатора, последовательный выход второго регистра подключен к второму информационному входу второго коммутатора, первому входу первого элемента И и через элемент HE к первому входу второго элемента И, параллельные выходы второго регистра соединены с соответствующими входами блока сумматоров, выходы которого подключены к первым входам первого вычислителя оценки вероятности и входам блока элементов НЕ, выходы которого соединены с первыми входами второго вычислителя оценки вероятности, выходы первого формирователя проверок, первого и второго вычислителей оценки вероятности подключены соответственно к первым — третьим входам вычислителя веса проверок, выходы которого соединены с входами первого сумматора, выход которого соединен с вторым входом элемента неравнозначности и является выходом декодера, выход элемента неравнозначности подключен к вторым входам первого и второго элементов И, выходы которых соединены с входами одноименных счетчиков, выходы которых подключены к вторым входам одноименных вычислителей оценки вероятности.

1396282

- Pnx пх

Р- Рп

-Pn

Составитель О.Ревинский

Техред Л.Сердюкова Корректор И. Иуска

Редактор Е.Копча

Заказ 2504/57

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4