Многоканальное устройство для программного управления

Иллюстрации

Показать всеРеферат

СОЮЗ COBE TCHHX

СО!.!ИАЛИС1 ИЧЕСНИ Х

РЕСПУБЛИН

„„SU„„1397877 А1 (б!) y G 05 В 19/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

4 6

СЮ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 410!628/24-24 (22) 30.05.86 (46) 23.05.88 Бюл. М 19 (72) Ю,А.Воробьев, В.Н.Кодяева и В.А.Федоров (53) 62!.396(088,8) (56} Авторское свидетельство СССР

11> 542113> кл. G 05 В 19/00, 1977.

Авторское свидетельство СССР

1!> 627447, кл. G 05 19/00> 1978

Авторское свидетельство СССР

Н 1231486, кл, G 05 В 19/18, 1984. (54) МНОГОКАНАЛЬНОЕ УСТРОИСТВО ДЛЯ

ПРОГРАММНОГО УПРАВЛЕНИЯ (57) Изобретение относится к автоматическому управлению и мокет быть использовано для программного управления технологическими процессами.

Цель иэобретення — повышение качества управления путем устранения потерь управляющих команд. Устройство содержит объектные датчики 1, блок 2 управления объектом, дешифратор 5, элемент ИЛИ 6, группу одинаковых каналов 7 управления, ключ 14 и блок управления 23 входными сигналами.

Устройство поэволяет исключить влияние случайности во время поступления входных сигналов, которая может привести к сбою работы, и предотвратить потери входной информации. 2 э.п. ф-лы, 2 ил, 1397877

Изобретение относится к автоматическому управлению и может использоваться для программного управления различными технологическими процесса5 ми и объектами при выполнении групп технологических операций.

Целью изобретения является повьппение качества работы устройства путем устранения потерь управляющих команд.

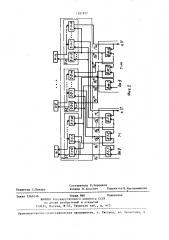

На фиг.l представлена блок-схема устройства; на фиг.2 — схема узла сборки.

Устройство содержит объектные датчики 1, блок 2 управления объектом, 15 содержащий узел 3 сборки, который состоит иэ и (по числу исполнительных элементов) блоков сборки 3-i (i

1, n), каждый иэ которых включает элемент ИЛИ 3-i-0 (i = 1, и) и m 20 элементов И З-i-,1 (i = 1, n;,1 =l,m), и исполнительны. элементы 4-1,..., 4-п, дешифратор 5 сигналов от объектных датчиков, элемент ИЛИ 6, каналы

7-1,...,7-п управления, содержащие для каждого i-го канала {i = l,m)

К управляющих триггеров 8-i-К, первый элемент И 9, второй элемент И 10, первый элемент ИЛИ ll элемент НЕ

12, триггер 13 памяти, ключ 14, ин- 30 формационные входы 15 и выходы 16 и

17 блока 2, управляющие входы 18 каналов управления, управляющие выходы

19 каналов управления, вход 20 записи команд, установочный вход 21, счетный вход 22 триггера памяти, блок

23 управления входными сигналами, содержащий первый элемент И 24, элемент

НЕ 25, второй 26 и третий 27 элементы И и первый 28 и второй 29 тригге- 40 ры.

Устройство работает следующим образом.

В исходном состоянии, в которое переводится устройство с помощью 45 ключа 14, все триггеры находятся в состоянии логической "1", При этом элемент И 10 канала управления и элемент И 24 блока 23 могут пропускать входные сигналы. Все остальные элементы И для прохождения сигналов закрыты. Сигналы с дешифратора через элемент ИЛИ 6 поступают на входы элемента И 24 и триггера 13 соответствующих каналов управления, перево- 55 дя последние в положение логического "0", что в свою очередь открывает элемент И 9 и закрывает элемент И 10.

Задний фронт сигнала на выходе элемента И 24 переводит триггер 28 в положение логического "0" и поступает на вход 18 канала 7-1 управления.

Сигнал с триггера 28 через элемент

НЕ 25 закрывает элемент И 24, препятствуя прохождению последуюпих сигналов в каналы управления.

Последующий сигнал с дешифратора

5, если сигнала на выходе 19 последнего канала управления не было, через открытый элемент И ?6 переводит триггер 29 в положение логического

"0". Сигнал с триггера ?9 открывает элемент И 27; тем самым запоминается наличие входного сигнала. Это состояние сохраняется до поступления сигнала с выхода 19 последнего канала управления, а входная информация с дешифратора сохраняется в триггерах 13 каналов управления. Сигнал с выхода последнего канала управления проходит открытый элемент И 27 и через элемент ИПИ 6 и открытый элемент И 24 поступает на вход первого канала управления и одновременно на входы триггеров 28 и 29, переводя их соответственно в положение

"0" и "1" ° Далее блок 23 работает аналогично описанному. Таким образом, блок 23, открывая канал управления первым сигналом с дешифратора, закрывает его для всех последующих входных сигналов до того момента времени, пока не закончится цикл управления и не поступит сигнал с выхода последнего канала управления об окончании . цикла.

На выходе элемента И 9 канала управления формируется сигнал на включение первого триггера 8-1-1 этого канала управления. С выхода данного триггера 8-1-1 первого канала 7-1 управления управляющий сигнал поступает на элемент ИЛИ 3-1-0 первого блока 3-1 сборки и одновременно открывает элемент И 3-1-1 ° После исполнения команды исполнительный элемент

4-1, запускаемый сигналом с выхода схемы ИЛИ 3-1-0, посылает сигнал на элементы И блока 3-1 сборки, который проходит открытый элемент И 3-1-1 и запускает второй триггер 8-1-2 первого канала управления, управляющий сигнал с выхода которого сбрасывает предыдущий триггер 8-1-1 и запускает через блок 3-2 сборки второй исполнительный элемент 4-2 и т.д. Сигнал об окончании работы последнего исполни1397877 тельного элемента 4-r> через блок 3-п сборки сбрасывает последний триггер

8-1-п первого канала управления и через элемент ИЛИ 11 запускает следую.

5 щий канал управления. Сигнал подается на вход триггера 13 памяти, нозвращая его в положение логической "1" и тем самым подготавливая к приему с дешифратора нового входного сигна- !О ла. Если программа управления не содержала, например, первой подпрограммы, то триггер 13 канала 7-1 управления будет находиться в состоянии

Н !!

1, с выхода элемента HF. 12 на вход !5 элемента И 10 подается сигнал, открывая его, в результате чего сигнал, поступивший на нход 18 запуска первого канала 7-1 управления, через открытый элемент И 10 и элемент ИЛИ ll 20 поступит на вход 18 следующего канала управления. По окончании пг-й подпрограммы либо после трансляции сигнала запуска через элементы И 10 и

ИЛИ 11 канала 7-(m-1) с ныхода 19 канала 7-m управления сигнал поступает иа вход своего триггера 13 памяти, как и в предыдущем канале, а также на вход триггера 28, переводя его в положение логической "1", и элемен- 30 та И 27 блока 23.

Формула изобретения

1,Многоканальное 7 стрОйство для 35 программного управления, содержащее объектные датчики, блок управления объектом, дешифратор, элемент ИЛИ, группу идентичных каналов управления и ключ, один из выводов которого яв- 40 ляется входом установки устройства в исходное положение, второй вывод

1 соединен с установочными входами

1 всех каналон управления, управляющий .вход каждого из которых, кроме перво" 45 го, связан с управляющим выходом предыдущего канала управления, информационные входы-выходы всех каналов управления подключены соответственно к информационным выходам и входам 50 блока управления объектом, входы записи команд всех каналов управления и входы элемента ИЛИ соединены с выходами дешифратора, входы которого связаны с выходами объектных датчиков, входы которых являются информационными входами устройства, о т л и ч а ющ е е с я тем, что, с целью повышения качества управления путем устранения потерь управляющих команд, н устройство введен блок управления входными сигналами, первый вход которого соединен с выходом элемента ИЛИ, второй вход — с вторым выводом ключа, третий вход — с управляющим выходом последнего канала управления, первый выход — с дополнительным входом элемента ИЛИ, а второй выход — с управляющим входом первого канала управления.

2.Устройство по п.l, о т л и— ч а ю щ е е с я тем, что блок управления входными сигналами содержит первый и второй триггеры, первый, второй и третий элементы Й и элемент

НЕ, выход которого соединен с первым нходом первого элемента И, а вход и первый вход второго элемента И вЂ” с инверсным выходом первого триггера, нулевой вход которого и единичный вход второго триггера связаны с выхо дом первого элемента И, являющимся вторым выходом блока, первый вход блока подключен к вторым входам первого и второго элементов И, первый вход третьего элемента И и единичный ьход первого триггера служат третьим входом блока, выход второго элемента

И соединен с нулевым входом третьего триггера, инверсный ныход которого связан с вторым входом третьего элемента И, выход которого является первым выходом блока, второй вход которого подключен к единичным входам первого и второго триггеров.

3.Устройство по пп.! и ?, о т л и ° ч а ю щ е е с я тем, что в каждом канале управления выход элемента ИЛИ соединен с единичным входом триггера памяти.

1397877

Составитель В,Воронков

Техред M.Ходанич Корректор М.Максимишинец

Редактор С.Пекарь

Подписное

Тирах 866

ВНИИ11И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Закаэ 2269/46

Проиэводственно-полиграфическое предприятие, r. Ужгород, ул, Проектная, 4