Устройство для умножения на коэффициенты

Иллюстрации

Показать всеРеферат

Изобретение относится к вычисли- I тельной технике и может быть использовано при построении устройств цифровой обработки сигналов. Цель изобретения - расширение области применения за счет возможности обработки множимого в дополнительном коде при получении результата умножения в дополнительном коде. Предлагаемое устройство для умножения на коэффициенты содержит последовательный сумматор-вычитатель 1, сдвиговые регистры 2-4, регистр 5 множимого, регистры 6,7 коэффициента, коммутаторы 8,9, счетчик 10 по модулю 2К, регистр 11 знака множимого, регистр 12 знака коэффициента, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 13,14 и элемент И 15 с соответствуницими связями. В устройстве осуществляется суммирование (вычитание) множимого к (из) сумме частных произведений , задержанной на С тактов в зависимости от кода преобразованного коэффициента 1 ил., 4 табл. (Л

А1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (51) 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ га

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3988240/24-24 (22) 06.12.85 (46) 23.05.88. Бюл. )) - 19 (72) С.Л.Титов, Е.Н.Титова, Ю.Ф.Рощинский и С.А.Волков (53) 628.325 (088.8) (56) Авторское свидетельство СССР

У 824197, кл. G 06 F 7/49, 1979.

Авторское свидетельство СССР

1305663, кл. G 06 F 7/49, 1985. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ НА КОЭФФИЦИЕНТЫЫ (57) Изобретение относится к вычислительной технике и может быть использовано при построении устройств цифровой обработки сигналов. Цель изобретения — расширение области применения за счет возможности обработки множимого в дополнительном коде при

I получении результата умножения в дополнительном коде. Предлагаемое устройство для умножения на коэффициенты содержит последовательный сумма» тор-вычитатель 1, сдвиговые регистры

2-4, регистр 5 множимого, регистры

6,7 коэффициента, коммутаторы 8,9, счетчик 10 по модулю 2К, регистр 11 знака множимого, регистр 12 знака коэффициента, элементы ИСКЛЮЧАЮЩЕЕ

ИЛИ 13, 14 и элемент И 15 с соответствуннцими связями. В устройстве осуществляется суммирование (вычитание) множимого к (из) сумме частных произведений, задержанной на С тактов в «с зависимости от кода преобразованного .коэффициента. 1 ил., 4 табл.

1397901

Изобретение относится к вычислительной технике и может быть использовано при построении устройств цифровой обработки сигналов.

Цель изобретения — расширение области применения за счет возможности обработки множимого в дополнительном коде при получении результата умножения в дополнительном коде.

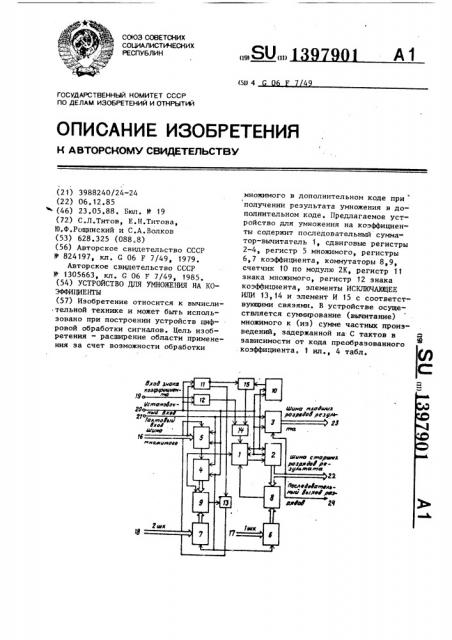

На чертеже представлена функциональная схема устройства.

Устройство для умножения на коэффициенты содержит последовательный сумматор-вычитатель 1, первый 2, второй 3 и третий 4 сдвиговые регистры, регистр 5 множимого, первый 6 и второй 7 регистры коэффициента, первый

8 и второй 9 коммутаторы, счетчик 10 по модулю 2К (К вЂ” разрядность множимого и коэффициента), регистр 11 знака множимого, регистр 12 знака коэф-, фициента, первый 13 и второй 14 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И

15, шину 16 множимого, первую 17 и вторую 18 шины коэффициента, вход 19 знака коэффициента, установочный вход

20, тактовый вход 2 1, шину 22 старших разрядов результата, шину 23 мпадших разрядов результата и последовательный выход 24 разрядов результата, причем вход 19 знака коэффициента соединен с информационным входом регистра 12 знака коэффициента, установочный вход 20 устройства соединен с входами установки в ноль первого 2, второго 3 и третьего 4 сдвиговых регистров, .счетчика 10 по модулю 2К, последовательного сумматора-вычитателя 1 и с входами разрешения записи регистра 5 множимого, регистра 11 знака множимого, регистра

12 знака коэффициента и первого 6 и второго 7 регистров коэффициента, тактовый вход 2 1 устройства соединен с тактовыми входами счетчика 10 по модулю 2К, последовательного сумматора-вычитателя 1, первого 2, второго 3 и третьего 4 сдвиговых регистров и регистра 5 множимого, установочные входы которого соединены соответственно с разрядами шины 16 мно" жимого устройства, информационные входы первого 6 и второго 7 регистров коэффициента соединены соответственно с разрядами первой 17 и второй

18 шин коэффициента устройства, разрядные выходы первого 6 и второго 7 регистров коэффициента соединены соционным входом второго сдвигового регистра 3, разрядные выходы которого соединены соответственно с шиной 23

50 младших разрядов результата устройства.

Устройство работает следующим образом.

В начале каждого цикла вычисления на вход 20 установки устройства поступает импульс, который производит обнуление последовательного сумматора-вычитателя 1, счетчика 1О и перво55 ответственно с управляющими входами первого 8 и второго 9 коммутаторов, выход первого коммутатора 8 соединен с первым входом последовательного

5 сумматора-вычитателя 1, выход которого соединен с информационным входом первого сдвигового регистра 2, разрядные выходы которого соединены соответственно с информационными входами первого коммутатора 8 и шиной

22 старших разрядов результата устройства, выход регистра 5 множимого соединен с вторым входом последовательного сумматора-вычитателя 1, информационным входом третьего сдвигового регистра 4 и первым информационным входом второго коммутатора 9, каждый (i+1)-й вход которого, начи20 ная с второго, соединен с х-м разрядным выходом третьего сдвигового регистра 4, начиная с первого разряда, прямой выход регистра 11 знака множимого соединен с первым входом

25 первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, второй вход которого соединен с выходом второго коммутатора 9, а выход " с информационным входом регистра 5 множимого, выход регистра 12 знака

30 коэффициента соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

14, второй вход которого соединен с выходом элемента И 15, а выход— с вторым входом последовательного сумматора-вычитателя 1, инверсный выход регистра 11 знака множимого соединен с первым входом элемента И 15, второй вход которого соединен с выходом счетчика 10 по модулю 2К, стар40 ший разряд шины 16 множимого устройства соединен с информационным входом регистра 11 знака множимого, выход младшего разряда первого сдвигового регистра 2 соединен с последовательным выходом 24 разрядов результата, выход старшего разряда первого сдвигового регистра 2 соединен с информа97901

3 13 го 2, второго 3 и третьего 4 сдвиговых регистров. Этим же импульсом производится запись множимого с шины 16 множимого в регистр 5 множимого, первой и второй частей преобразованного коэффициента соответственно с первой

17 и второй 18 шин коэффициента соотвественно в первый 6 и второй 7 регистры коэффициента, знака множимого со старшего (энакового) разряда шины

16 множимого в регистр 11 множимого и знака коэффициента с входа 19 знака коэффициента в регистр 12 знака коэффициента. Затем на тактовый вход

2 1 устройства начинают поступать тактовые импульсы, причем их количество в каждом цикле умножения равно 2К.

С началом поступления тактовых импульсов в регистре 5 множимого производится IIQTBKTQBblA сдвиг множимого, которое, начиная с младшего разряда, поступает на второй вход последовательного сумматора-вычитателя 1 и, в зависимости от значения управляющего сигнала, поступающего на вход последнего с выхода второго элемента HCKIIIOЧАЮЩЕЕ ИЛИ 14, суммируется или вычитается из значения суммы частичных произведений, которая поступает на первый вход последовательного сумматора-вычитателя 1 с его же выхода, но задержанная на С тактов в первом сдвиговом регистре 2 и первом коммутаторе 8.

По мере выхода из регистра 5 множимого младших разрядов множимого, в регистр 5 множимого на освободившееся место вновь с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 записывается значение множимого или число, ему инверсное, что определяется состоянием регистра 11 знака множимого.

Причем в связи с тем, что в начале каждого цикла умножения третий сдвиговый регистр 4 обнуляется, между старшим разрядом множимого, первоначально записанного в регистр 5множимого, и младшим разрядом вновь записываемого множимого формируется

В (В О) нулей (единиц), В результате после К тактов вычисления в регистре 5 множимого формируется число, состоящее из В нулей и К вЂ” В младших разрядов множимого, или число, инверсное указанному. Это число в течение последних К тактов вычисления поступает на второй вход последовательного сумматора-вычитателя 1.

В течение 2К тактов вычисления с выхода младшего разряда первого сдвигового регистра 2 на последовательный выход 24 результата устройства последовательно поступают 2К бит результата умножения с удвоенной точностью.

В последние К тактов вычисления с выхода старшего разряда первого сдвигового регистра 2 во второй сдвиговый регистр 3 переписывается К младших разрядов произведения. В результате в конце каждого цикла умножения во втором сдвиговом регистре 3 оказываются сформированные К младших разря" дов произведения, которые поступают на шину 23 младших разрядов результата устройства, а в первом сдвиговом регистре 2 — К старших разрядов произведения, которые поступают на шину

22 старших разрядов результата устройства.

В табл. 1-4 приведены примеры умножения множимого 01101011 на коэффициент 01001001 для четырех возможных . случаев комбинаций знаков множимого и коэффициента. Для данного варианта

К=8, С=2, В=1. В первых строках таблиц обозначена операция, выполняемая последовательным сумматором-вычитателем

1, во вторых строках — число, поступающее на первый вход, в третьих строках — число, поступающее на второй вход последовательного сумматоравычитателя 1, в четвертых и пятых строках — значение триггеров соответственно переноса и заема последовательного сумматора-вычитателя 1, в шестых строках — результат умножения.

Как видно из таблиц, в случае одинаковых знаков множимого и коэффициента (табл. 1 и 4) результат умножения получается в дополнительном (прямом) коде положительного числа, а в случае разноименных знаков — в дополнительном коде отрицательного числа.

Таким образом, предлагаемое устройство позволяет производить перемножение коэффициента со знаком на множимое в дополнительном коде при получении результата умножения в дополнительном коде, что имеет место в большинстве вычислительных устройств. формула изобретения

Устройство для умножения на коэффициенты, содержащее последовательный сумматор-вычитатель, первый, 1397901

Таблица 1

Множимое — положительное, коэффициент — отрицательный

1. СЛОЖЕНИЕ ВЫЧИТАНИЕ

2.0001100000101111

3.1101011001101011

01 1 1 1000

4, 00001 1 1 1

5. 00000000

6. 1 1000001 второй и третий сдвиговые регистры, регистр множимого, первый и второй регистры коэффициента, первый и вто-. рой коммутаторы, счетчик по модулю

2К (К вЂ” разрядность множимого и коэф5 фициента), регистр знака множимого, регистр знака коэффициента и первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вход знака коэффициента устройства соединен с информационным входом регистра знака коэффициента, установочный вход устройства соединен с входами установки в "0" первого, второго и третьего сдвиговых регистров, счетчика по модулю 2К, последовательного сумматора-вычитателя и с входами разрешения записи регистра множимого, регистра знака множимого, регистра знака коэффициента и первого 20 и второго регистров коэффициента, тактовый вход устройства соединен с тактовыми входами счетчика по модулю

2К, последовательного сумматора-вычитателя, первого, второго и третьего сдвиговых регистров и регистра множимого, установочные входы которого соединены соответственно с разрядами шины множимого устройства, информационные входы первого и второго регистров коэффициента соединены соответственно с разрядами первой и второй шин коэффициента устройства, разрядные выходы первого и второго регистров коэффициента соединены соответственно с управляющими входами первого и второго коммутаторов, выход первого коммутатора соединен с первым информационным входом последовательного сумматора-вычитателя, выход которого соединен с информационным входом первого сдвигового регистра, разрядные выходы которого соединены соответственно с информационными входами первого коммутатора и с шиной старших разрядов результата устройства, выход регистра множимого соединен с вторым информационным входом последовательного сумматора-вычитателя, информационным входом третьего сдвигового регистра и первым информационным входом второго коммутатора, каждый информационный вход которого, начиная с второго, соединен с i-м разрядным выходом третьего сдвигового регистра, начиная с первого разряда, прямой выход регистра знака множимого соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом последовательного сумматора-вычитателя, выход младшего разряда первого сдвигового регистра соединен с последовательным выходом разрядов результата устройства, выход старшего разряда первого сдвигового регистра соединен с информационным входом второго сдвигового регистра, разрядные выходы которого соединены соответственно с шиной младших разрядов результата устройства, отличающееся тем, что, с целью расширения области применения эа счет возможности обработки множимого в дополнительном коде при получении результата умножения в дополнительном коде, в него введен элемент И, причем вход старшего разряда регистра множимого соединен с информационным входом регистра знака множимого, инверсный выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом счетчика по модулю 2К, выход элемента И соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом регистра знака коэффициента, выход второго коммутатора соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информационным входом регистра множимого.

1397901

Таблица2

Множимое — положительное, коэффициент — отрицательный

ВЫЧИТАНИЕ

Таблица3

Множимое — отрицательное, коэффициент — положительный

1. СЛОЖЕНИЕ

СЛОЖЕНИЕ

2.000101111010000

10101011

00000000

10000111

Таблица 4

Множимое — отрицательное, коэффициент — отрицательный

1, ВЫЧИТАНИЕ

2.00011000

3.10101001

4. 00000000

5 ° 01110000

6. 1 1000001

11111100

01 1 1 1000

Составитель В.Гусев

Техред Jl.Олийнык Корректор M.Пожо

Редактор И.Николайчук

Заказ 2271/47

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д . 4/5

Производственно-полиграфическое предприятие, г. Ужгород, уп. Проектная, 4

2,00010111

3.11010110

4. 00000000

5. 01111111

6. 10111110

3. 1 0 1 0 1 О 0 1

4. 00000000

5. 00000000

6.10111110

СЛОЖЕНИЕ

01101011

10000111

ВЫЧИТАНИЕ

00101111

10101011

00000000