Устройство для отладки программ

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1397921 А1 (51) 4 С 06 F 11/28 в

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3901255/24-24 (22) 12.05.85 (46) ?3.05.88. Бюл. Ф 19 (7 1) Специяльное конструкторское бюро "Кибернетика" с опытным производством Института кибернетики АН АЗССР (72) С.A. Бакалец, Н.В. Головин, H.H, Насруллаев и Б.Ф. Файсканов (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 980086, кл. G 06 F 11/26, 1982.

Авторское свидетельство СССР

Ф 1030885, кл. С 06 F 11/22, 1983. (54) (57) УСТРОЙСТВО ДЛЯ ОТЛАДКИ

IIP0IPAMM, содержащее, первый и второй блоки памяти, первый элемент ИЛИ, первый блок сравнения, счетчик и элемент

И, причем первый выход первого блока памяти соединен с первым входом первого блока сравнения, выход счетчика соединен с адресным входом второго блока памяти, о т л и ч а ю щ е е с я тем, что, с целью ускорения процесса отладки, в устройство введены третий блок памяти, блок индикации, второй элемент ИЛИ и второй блок сравнения.

1f причем выход счетчика соединен с информационным входом блока индикации, с адресными входами первого и третьего блоков памяти, второй выход первого блока памяти, первый, второй выходы второго блока памяти и выход третьего блока памяти соединены соответственно с первым входом элемента

ИЕИ, с первым входом второго блока сравнения, со вторым входом элемента

ИЛИ и с информационным входом счетчика, информационньп» вход устройства соединен с вторыми входами первого и второго блоков сравнения, выход равенства первого блока сравнения соединен с первым входом второго элемен- а та ИЛИ и со счетным входом счетчика, выход равенства второго блока сравнения соединен со входом записи сче1чика и вторым входом второго влемевта ИЦИ, выход которого соединен с первым входом элемента И, выход первого элемента ИЛИ соединен со вторым входом элемента И, выход которого является выходом прерывания отлаживаемой програм»ы.

13979 1

Изобретение относится к вычислительной технике и может быть использовано при отладке программ вычислительной системы в реальном масштабе времени и построении специализированных систем для отладки программ.

Целью изобретения является ускорение проце сса отладки.

1О

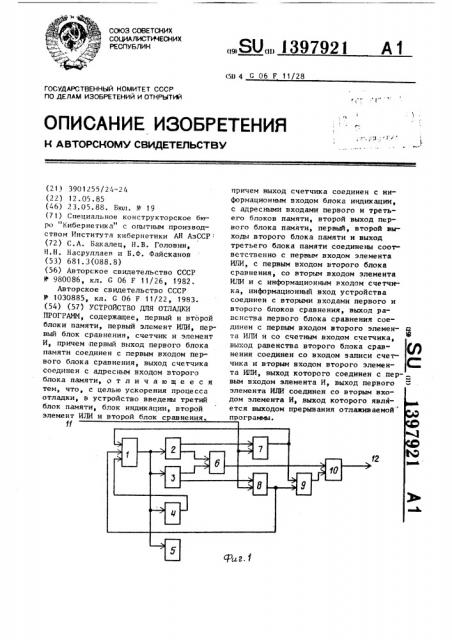

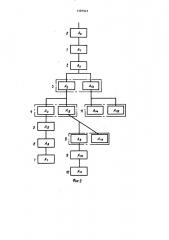

На фиг. 1 представлена блок-схема устройства для отладки программ; на фиг.2 — пример задания трассы про= грамм в виде графа; на фиг.3 — пример задания трассы программ в блоках памяти.

Устройство для отладки программ (фиг.1) содержит счетчик 1, первый 2, втор. и 3 и третий 4 блоки памяти, блок 5 индикации, первый элемент ИЛИ б, первый 7 и второй 8 блоки сравнения, второй элемент ИЛИ 9, элемент

И 10, информационный вход 11 устройства н управлякиций выход 12 прерывания отлаживаемой программы, Счетчик 1 предназначен для формирования адресов ячеек, выбираемых в первом 2, втором 3 и третьем 4 блоках памятИ.

Первый блок 2 памяти предназначен для хранения задаваемых адресов трасснруемой программы, второй блок 3 памяти — для хранения, задаваемых адре" сов возможных переходов трассируемой программы, третий блок 4 памяти — для 35 хранения адреса перехода, заносимого в счет ик 1.

Блок 5 индикации используется для визуального контроля за адресом ячеек первого 2, второго 3 и третьего 4 40 блоков памяти, по которым можно определить место останова трассируемой программы.

Первый 7 и второй 8 блоки сравнения предназначены для сравнения адРесов 45 трассируемой программы, поступакицих на информационный вход 1 1 устройства с заданными адресами трассы, считываемыми из первого 2 и второго 3 бло" ков памяти.

Первый 6 и второй 9 элементы HJIH и элемент И 10 предназначены для формирования управляющего сигнала, поступакицего на выход 12 устройства. Этот сигнал может использоваться для прерывания отлаживаемой программы или для ее останова.

Предлагаемая трасса отлаживаемой программы задается в виде графа.

Пример такого задания irpeдставле н на фиг.2, где А„- А „, — адреса команд или констант, записанных в ячейки с 0-11, к которым может быть обращено в процессе выполнения программы.

8 первом 2, втором 3 и третьем 4 блоках памяти сформирована информация, показанная на фиг.3 при этом информация для сравнения может быть считана с выходов первого 2 и второго

3 блоков памяти, а признак останова— с соответствующих выходов первого 2 и второго 3 блоков (+ (х) — состояние признака может быть 1 или О, ** (-)— состояние безразлично).

Устройство работает следущим образом.

Перед запуском устройства содержимое счетчика 1 обнуляется (сигнал обнуления не показан).

На информационный вход 11 устройства поступают сигналы с адресной магистрали отлаживаемого устройства, которые подаются на входы первого 7 и второго 8 блоков сравнения.

С информационных выходов первого 2 и второго 3 блоков памяти на другие входы первого 7 и второго 8 блоков сравнения подаются сигналы, соответствующие информации, хранящейся в этих блоках памяти по нулевому адресу (так как содержимое счетчика 1 равно нулю); на информационный вход первого блока 7 сравнения подается код А, (фиг.3), на информационный вход второго блока 8 сравнения — код н.А (несуществующего адреса, такого, по которому обращение отлаживаемой программы независимо).

Когда выполнение отлаживаемой программы дойдет до адреса Ао (фиг. 1), первый блок 7 сравнения вырабатывает сигнал сравнения, который проходит через второй элемент ИЛИ 9 на вход элемента И 10. Если с другого информационного выхода первого блока 2 памяти считан единичный сигнал, который поступает через первый элемент ИЛИ 6 на другой вход элемента И 10, то на выходе элемента И 10 формируется сигнал прерывания отлаживаемой программы или ее останова. Если с другого информационного вьчхода первого блока

2 памяти считывается нулевой сигнал, то останова или прерывания отлаживаемой программы не происходит. ,!

Сигнал с выхода первого блока 7 сравнения одновременно поступает на

21 з 13979 счетный вход счетчика 1, работающий в режиме сложения.

По этому сигналу содержимое счетчика 1 увеличивается на единицу. ПоЬ сле увеличения содержимого счетчика 1 с его выхода на адресные входы первого 2, второго 3 и третьего 4 блоков памяти устройства подается адрес их следующей ячейки, т.е. с информацион-1р ного выхода первого блока 2 памяти считывается код А1 (фиг.3), с информационного выхода второго блока 3 памяти — код н.А, состояние информационного выхода третьего блока 4 памяти1 безразлично.

После дальнейшего запуска отлажив аемой программы (после прерывания или останова, если они были) процесс сравнения повторяется аналогично опи- 2р санному.

После прохождения отлаживаемой программы адреса А (фиг.2) возможно ветвление программы на адрес А или

3 адрес А 1>. После прохождения отлаживаемой программы адреса А содержимое счетчика 1 равно "3". Этот код с выхода счетчика 1, поступая на адресные входы блоков 2 — 4 памяти, производит считывание информации по адресу "3" . С информационного выхода перво го блок а 2 памяти у стр ой с тв а считывается код А> с информационного выхода второго блока 3 памяти — код

А,, с информационного выхода третье- з го блока 4 памяти на информационный вход счетчика 1 поступает число "11".

Если отлаживаемая программа пойдет по ветке, содержащей адрес А1, то устройство срабатывает так же как в опи- 4р санйых случаях. Если произойдет срав нение с адресом А,, то второй блок

8 сравнения вырабатывает сигнал, который поступает на второй вход элемента И 10 через элемент ИЛИ 9, определяя момент прерывания или останова выполняемой программы, если этот режим был задан единичным сигналом, поступающим с другого информационного выхода второго блока 3 памяти на вход элемента И 10 через элемент ИЛИ 6.

Сигнал с выхода второго блока 8 сравнения одновременно поступает на вход записи счетчика 1 и производит запись в счетчик 1 поступающего на его информационный вход числа, т.е.

"11".

По этому адресу, поступающему с выходов счетчика 1 на адресные входы блоков 2 — 4 памяти, выбирают ячейки, соответствующие дальнейшей проверке отлаживаемой программы после прохождения адреса А, (фиг.2 и 3).

Для останова выполнения отлаживаемой программы по конечным адресам (B данном примере А, Л „, А,, А 1

А q) в соответственных ячейках первого 2 и второго 3 блоков памяти (в данном примере 7, 8, 10 и 11 ячейки) имеются установленные в единицу признаки останова.

Прохождение программ можно также контролировать по состоянию счетчика 1, сигналы с выхода которого поступают на вход блока 5 индикации и преобразуются в визуальную форму.

Таким образом, использование изобретения позволяет существенно сократить время отладки программ.

1397921

1397921

Составитель И. Сигалов

Техред M.Ходянич КорректоР М. Максимишинец

Редактор И. Николайчук

Заказ 2272/48 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4