Устройство для моделирования упругого гистерезиса

Иллюстрации

Показать всеРеферат

Изобретение относится к аналоговой вычислительной технике. Цель изобретения - повышение точности моделирования упругого гистерезиса при циклических деформациях за счет устранения неидентичности воспроизведения нисходящей и восходящей ветвей петли гистерезиса. Для этого в устройство дополнительно введены, блок вьеделеиия модуля, инвертор, блок выделения знака входного сигнала и ключ. Введение блока .выделения модуля позволяет настраивать блок нелинейности только на воспроизведение положительной ветви экспериментальной функции. В зависимости от знака входного сигнала напряжение с выхода блока нелинейности с помощью ключа подается на вход сумматора с запоминанием либо со своим знаком, либо через инвертор с противоположным знаком. Управление работой ключа осуществляется от блока выделения знака входного сигнала. 1 ил. i СЛ

СОЮЗ СОЕЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (191 (И) (51) 4 С 06 G 7/48

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTVM (21) 4142772/24-24 (22) 05. 11. 86 (46) 23.05.88. Бюл. У 19 (71) Куйбышевский авиационный институт им. акад. С.П.Королева (72) В.А,Вьниканин, Е.И.Давыдов и А.К.Мартынов (53) 681.335(088.8) (56) Авторское свидетельство СССР

NI 860091, кл. G 06 G 7/48, 1979.

Авторское свидетельство СССР

9 996666770088, кл. С 06 G 7/48, 1980. (54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ

)ЧТРУГОГО ГИСТЕРЕЗИСА (57) Изобретение оТНосНТсН к аналоговой вычислительной технике. Цель изобретения — повышение точности моделирования упругого гистереэиса при циклических деформациях за счет устранения неидентичности воспроизведения нисходящей и восходящей ветвей петли гистереэиса. Для этого в устройство дополнительно введены блок выделения

1 модуля, инвертор, блок выделения знака входного сигнала и ключ. Введение блока .выделения модуля позволяет настраивать блок нелинейности только на воспроизведение положительной ветви экспериментальной функции. В зависимости от знака входного сигнала напряжение с выхода блока нелинейности с помощью ключа подается на вход сумматора с запоминанием либо со своим знаком, либо через инвертор с противоположным знаком. Управление работой ключа осуществляется от блока вы- ур деления знака входного сигнала. 1 нл.

1397946

20 (f 1 ) sign E., С (t,; („) + 2f (1/2 Е ) . sign E., Изобретение относится к аналоговой вычислительной технике.

Цель изобретения — повьппение точности моделирования.

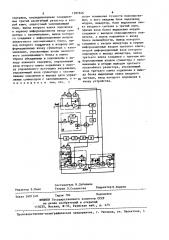

На чертеже представлена функциональная схема устройства для моделирования упругого гистерезиса.

Устройство содержит операционный усилитель (ОУ) 1, первый ключ 2, 1 ключ 3 сброса, второй ключ 4, первый масштабный резистор 5, интегрирующий конденсатор 6, блок 7 нелинейности, сумматор 8 с запоминанием, аналоговый запоминающий блок 9, второй и третий масштабные резисторы 10 и 11, блок 12 фиксации нуля, управляемый источник 13 напряжения, цепь 14 управления сумматором с запоминанием, элемент 15 задержки.

Сумматор 8 с запоминанием содержит ОУ 16, конденсатор 17, масштабгде Е 1 — модуль приращения деформации конструкции.

Весь процесс моделирования петли гистерезиса состоит из трех основных этапов: моделирование начального участка петли, моделирование нисходящей ветви, моделирование восходящей ветви. 35

Устройство работает следующим образом.

Исходное состояние схемы устройства соответствует этапу моделирования начального участка петли. 40

В исходном положении ключи 2,3 и

27 разомкнуты, а ключи 4 и 19 замкнуты. При этом коэффициент передачи интегратора 31 и коэффициент передачи по первому входу сумматора 8 с sano- 45 минанием равны единице. Напряжение на выходе ОУ 36 блока 35 вьщеления знака входного сигнала равно нулю и реле 38 обесточено, а его контакты (ключ 34) нормально замкнуты. Настройка элемента 37 ограничения в цепи обратной связи ОУ 36 обеспечивает появление напряжения на выходе усилителя только при отрицательном входном сигнале. 55

Напряжение, пропорциональное скорости деформации, поступает на вход ОУ 1 через масштабный резистор

5 в блок 12 фиксации нуля и в блок ный резистор 18, ключ 19, два форсирующих звена 20 и 21, каждое из которых содержит параллельно включенные резистор 22 и конденсатор 23. Аналоговый запоминающий блок 9 содержит

ОУ 24, конденсатор 25, масштабный резистор 26, ключ 27, форсирующее звено 28, состоящее из параллельно соединенных резистора 29 и конденсатора

30. Элементы 1,5 и 6 представляют собой интегратор 31. Кроме того, устройство содержит блок 32 вьщеления модуля, инвертор 33, ключ 34 и блок

35 вьщеления знака входного сигнала, состоящий из ОУ 36, элемейта 37 ограничения, реле 38 и масштабного резистора 39.

Устройство реализует аналоговую модель упругого гистерезиса в виде

35 вьщеления знака входного сигнала.

Напряжение, отражающее изменение деформации, с выхода интегратора 31 поступает в блок 32 вьщеления модуля, с выхода которого модуль приращения деформации !Е! подается на вход блока 7 нелинейности. Блок нелинейности настраивается на воспроизведение только положительной ветви функции

f(). С выхода блока нелинейности снимается напряжение, пропорциональное f (!Я ) . Это напряжение всегда бу— дет положительным. Так как начальный участок воспроизводится при E > О, напряжение с выхода блока 7 нелинейности, знак которого совпадает со знаком входного сигнала, через нормально замкнутый ключ 34 поступает на первый информационный вход сумматора 8 с запоминанием. На третий вход сумматора 8 подается напряжение с выхода блока 9. В начальный момент времени на выходе аналогового запоминающего блока 9 напряжение равно нулю, поэтому выходное напряжение сумматора пропорционально значению функции f(1E! ). Первый этап моделирования заканчивается в момент t когда

E.= О.

Для перехода от моделирования начального участка петли к моделированию нисходящей ветви необходимо в сумматор 8 переводится в режим запоминания сигнала, который находился

3 139794 определенной последовательности с помощью цепей управления произвести переключения в схеме устройства.

В момент t = t по сигналу цепи

5

14 управления сумматором ключ 19 размыкается. При этом вход ОУ 16 сумматора с запоминанием отключается от его входных цепей, в результате чего

6 4 ления знака входного сигнала появляется напряжение, которым залитывается реле 38. Контакты реле 38 (ключ 34) размыкаются. При этом первый информа-, ционный вход сумматора 8 подключается к выходу инвертора 33, назначение которого изменять знак сигнала, поступающего с выхода блока 7 нелинейности.

Этап моделирования нисходящей ветна выходе усилителя по окончанию предыдущего этапа моделирования. По сигналу с выхода элемента 15 задержки замыкается ключ 3, и напряжение на выходе интегратора 31 становится равным нулю. Одновременно замыкается ключ 27. При этом вход ОУ 24 соединяется с его выходной цепью, превращая блок 9 в масштабное звено. На выходе

ОУ 24 появляется напряжение, равное напряжению на выходе ОУ 16. Одновременно с этими переключениями происходит перестройка входных цепей интегратора 31 и сумматора 8 с запомина- 25 нием. По сигналу от управляемого источника 13 напряжения ключ 2 переключает коэффициент передачи интегратора 31, устанавливая его равным 1/2, а ключ 4 устанавливает коэффициент передачи по первому входу сумматора

8 с запоминанием, равным двум. Эти новые значения коэффициентов передаМи сохраняются в течение. всех последующих этапов моделирования. Синхронизация работы всех цепей управления осуществляется по сигналам с блока

12 фиксации нуля.

В момент времени t ) t, по сигналу

35

E г-О производится возврат схемы в ра- 40 бочее состояние для моделирования нисходящей ветви петли. Эти обратные переключения в схеме устройства также производятся в определенной последовательности. Сначала размыкаются ключи 3 и 27. При этом в исходное состояние возвращаются интегратор 31 и блок 9, на выходе которого теперь хранится конечный результат предыду- щего этапа моделирования. После это50

ro замыкается ключ 19, и в исходное состояние — режим суммирования — возвращается сумматор 8 с запоминанием.

Так как моделирование этого этапа происходит при Е (О, необходимо изме55 нить знак сигнала, поступающего с выхода блока 7 нелинейности на первый информационный вход сумматора 8.

При E (0 на выходе ОУ 36 блока выдеви длится до момента времени С а С, когда снова Е = 1.

При t = t происходит переход от моделирования нисходящей ветви к моделированию восходящей ветви петли, который проводится в той же последовательности, что и переход к предыдущему этапу. Поскольку моделирование восходящей ветви проводится при Е 0, напряжение на выходе ОУ 36 блока 35 выделения знака вновь становится равным нулю, реле 38 обесточивается и ключ 34 замыкается. Снова выход блока 7 нелинейности подключается непосредственно к первому информационному входу сумматора 8 с запоминанием.

Заключительный этап — моделирование восходящей ветви — длится до момента t = t, при котором вновь E.= =О. формула изобретения

Устройство для моделирования упругого гистерезиса, содержащее операционный усилитель, в цель обратной связи которого включены параллельно соединенные интегрирующий конденсатор и ключ сброса, первый и второй масштабные резисторы, первые выводы которых объединены и являются входом устройства, первый ключ, информационный вход которого подключен к второму выводу первого масштабного резистора, выход первого ключа и второй вывод второго масштабного резистора объединены и подключены к входу операционного усилителя, последовательно соединенные блок фиксации нуля и и управляемый источник напряжения, выход которого подключен к управляющему входу первого ключа, вход блока фиксации нуля подключен к входу устройства, блок нелинейности, сумматор с запоминанием, выход которого является выходом устройства, последовательно соединенные цепь управления сумматором с запоминанием и элемент

Составитель И.Дубинина

Техред Л.Сердюкова Корректор Н.Король

Редактор Е.Папп

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35 ° Раушская наб., д. 4/5

Заказ 260I/49

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5 13979 задержки, последовательно соединенные третий масштабный резистор и второй ключ, аналоговый запоминающий блок, выход второго ключа подключен к первому информационному входу сум5 матора с запоминанием, выход которого соединен с информационным входом аналогового запоминающего блока, выход которого подключен к второму ин1 формационному входу сумматора с sanoминанием, управляющие входы аналогового запоминающего блока и ключа сброса объединены и подключены к выходу элемента задержки, управляющий вход второго ключа подключен к выходу управляемого источника напряжения, управляющий вход сумматора с запоминанием подключен к выходу цепи управления сумматором с запоминанием, о т- 2р л и ч а ю щ е е с я тем, что, с целью повышения точности моделирования, в него введены блок вьщеления модуля, инвертор, блок вьщеления знака входного сигнала и третий ключ, причем вход блока вьщеления модуля соединен с выходом операционного усилителя, а выход подключен к входу блока нелинейности, выход которого соединен с входом инвертора и первым информационным входом третьего ключа, второй информационный вход которого подключен к выходу инвертора, выход третьего ключа соединен с третьим информационным входом сумматора с запоминанием и вторым выводом третьего масштабного резистора, управлямиций вход третьего ключа подключен к выходу блока выделения знака входного сигнала, вход которого подключен к входу устройства.