Устройство аналого-цифрового преобразования

Иллюстрации

Показать всеРеферат

Изобретение относится к электроизмерительной технике и может быть J /x , 0 ,, , Л использовано при построении точных быстродействующих аналого-цифровых преобразователей, Б устройство, содержащее АЦПср 1, регистр 2.памяти,. АДУ3, выходной регистр 4, элемент 5 задержки , усилитель 6 разности5 АЦПд;, 7, ЦАП 8, ПЗУ 9, блок 10 управления с, целью повьшения точности и быстродействия введены цифровой сумматор 11, ОЗУ 12, переключатель 13,.элемент ИЛИ 14 и блок 15 формирования образцовых сигналов. Повьшение точности достигается коррекцией дополнительной погрешности преобразования с введением поправки в цифровом виде, период дискретизации сокращаетсяблагодаря исключению ряда узлов, следовательно, и задержек, вносимых ими. в процессе преобразования. Функциональные возможности расширяются за счет введения узлов, обеспечивающих режим самокоррекции устройства, 2 з,п, ф-лы, 2 шт., 2 табл. я о со 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСГ1УБЛИН (191 (11) А1 (gp 4 Н 03 M 1/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2 1 ) 4078 738/2 4-24 (22) 11.05,86 (46) 23.05.88, Бюл. у 19 (71) Пензенский политехнический институт (72} А.А. Солодимов, Ю.В. Полубабкин, В.М. Шляндин и Л.Ю. Равер (53) 681.325(088,8) (56) Шляндин В.N. Цифровые измерительные устройства. — М,: Высшая школа, 1981 с ° 166 рис. 2.27.

Грешищев Ю.М., Гудинов А.Г. АЦП-10, БИТ/13,5 МГц для кодирования телевизионных сигналов. Проблемы создания преобразователей формы информации.

Тезисы докладов 5-го Всесоюзного симпозиума. — Киев: Наукова думка, 1984, с. 116-119. (54) УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО

ПРЕОБРАЗОВАНИЯ (57) Изобретение относится к электроизмерительной технике и может быть использовано при построении точкых быстродействующих аналого-цифровых. преобразователей, В устройство, содержащее АПП, 1, регистр 2,.памяти,. АЛУЗ, выходной регистр 4, элемент 5 задерж- . ки, усилитель 6 разности, .Щ1 7, ЦАП 8, ПЗУ 9, блок 10 управления, с. целью повышения точности и быстродействия введены цифровой сумматор 11, ОЗУ 12, переключатель 13,.элемент

ИЛИ 14 и блок 15 формирования образцовых сигналов, Повышение точности достигается коррекцией дополнительной погрешности преобразования с введением поправки в цифровом виде, период дискретизации сокращается- благодаря 3 исключению ряда узлов, следовательно, и задержек, вносимых ими.в процессе 3вФУ преобразования. Функциональные воз- С можности расширяются за счет введения узлов, обеспечивающих режим са" Д мокоррекции устройства, 2 з,п, ф-лы, 2 ил., 2 табл. л

1398093

Изобретение относится к электроизмерительной технике и может быть использовано для построения быстродействуюших аналого-цифровых преоб5 разователей (АЦП) повышенной точностиа

Цель изобретения - повышение точности и увеличение быстродействия.

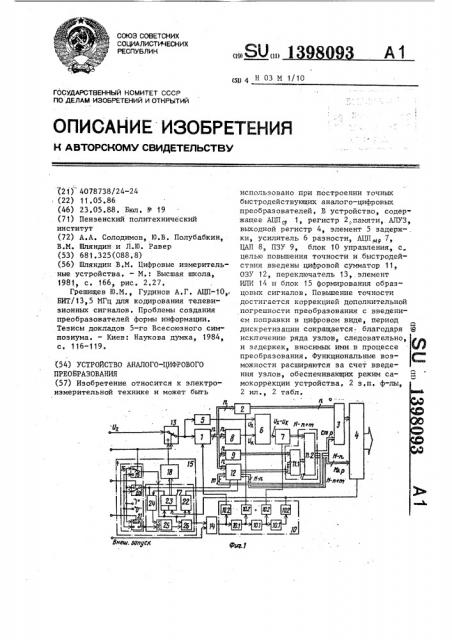

На фиг. 1 приведена функциональная схема устройства аналого-цифрового преобразования; на фиг.. 2— функциональная схема ярифметико-логи-3еского устройства (АЛУ), Устройство аналого"цифрового пре- 15 образования содержит АЦП tп старших ра".ðÿäîâ, регистр 2 памяти, АПУ->, выходной И-разрядный регистр 4, элемент 5 задержки, усилитель 6 раэнои у Agti 7 млад311их р Яэ рядОв у цифр о 20

;.налогавьп преобразователь 8 (ЦАП), постоянное запэминающее устройство 9 (ПЗУ)р блОк i0 упрЯвления„ цифрОвой

oóìì2òîp 11, оперативное запоминаюшее устройство 12 (СЗУ), переключа- 25 тель 13, элемент ИЛИ 14, блок i5 формировЯния Обра3цо!Зых сигнЯлОВ s b3bIполыенный на узле i6 задания рккимо33-„ блок 17 и источник 18 Опорного напряуе ния, 30

Узел 16 зядяния режимов выполнен

-.я .:ервом 19, втором 20, и третьем переключятелях„

Блок 17 выполнен на элементе ИЛИ

22. счетчике 23 импульсов, элементе

И 24, триггере 25 и -.енераторе 26 киульсов.

Блок 10 управления состоит иэ трех последовательно соединенных элементов задержки выхОды котopbE,10

--;: вход первого из ыих через формирователи импульсов подключены к:выходам устройства 10 управления.

АЛУ 3 выполнено на элементе ИЛИ 27, элементе И 28 и цифровом сумматоревычитятеле 29.

Устройство работает в режиме I

В первом режиме участвуют все узлы устройства. во--втором — все, за исключением блока 15 формирования образцовых сигналов, причем переключатель 13 устаыагливается B положение И,„

5 при котором О„ подается на вход АЦП 1, с 3гналы "Запись" и "Внутр,. запуск" с генератора 26 импульсов не формиру1! ются а с помощью сигнала Обнуление" обнуляется содержимое ячеек ОЗУ

12.

Рассмотрим работу устройства в режиме непосредственного преобразования входного сигнала на конкретном примере. Допустим, что число разрядов всего устройства, включая знаковый разряд, N = 11, число разрядов АЦП 1 и = 4, АЦПм 7 N - п + m = 8(m = 1, где m — число разрядов коррекции, см. известное устройство), а диапазон U„ = (-1,024В) — (+1,024В). Так же, как и в известном устройстве, здесь в качестве узла 8 используется

"грубый" быстродействующий интегральный ЦАП (к примеру 1118 ПА1). Инструментальная погрешность такого ЦАП значительна и в несколько раз превышает требования, предъявляемые к узлу

8 в составе устройства аналого-цифрового преобразования, Допустим, что значения разрядных уровней ЦАП 8 с учетом их инструментальных погрешностей равны: 0,= 1283 = 125 мВ; U 256 + 2 = 258 мВ; — 512 — 4 = 508 мВ; Од = -1024 +

+ 4 = -1020 мВ, значения всех остальных уровней ЦАП 8 определяются линейной комбинацией разрядных уровней (смещение нуля усилителя 6 разности считаем равным нулю).

На этапе изготовления и настройки устройства, как и известного устройства, инструментальные погрешности IIjGI 8, присущие каждому выходному уровню, определяются экспериментально при нормальных условиях и записываются в цифровой форме с учетом знаКЯ в ячейки ПЗУ 9. Адресом каждой ячейки ПЗУ 9 является соответствующий код АЦП, 1 (табл. 1 составлена для положйтельного входного сигнала i3„).

Пусть „= 640 мВ. После стробирования АЦП, 1 сформируется код +101, который преобразуется с помощью ЦАП 8 ср в компенсирующее напряжение, равное и + u, = 125 + 508 = 633 мВ. Разноgf Ъ стный сигнал U - LI = 640 — 633 =

= 7 мВ, установившийся на выходе усилителя 6 разности, после стробирования АЦП„ 7 преобразуется в код

+0000111 (+7 мВ). По коду +101 из ячейки ПЗУ 9 с этим адресом производится выборка кода основной погрешности (см. табл. 1), равного — 111 (-7 мВ), который складывается в циз 1398093 а фровом сумматоре 11 с кодом AIJII > положение К. После этого с выхода

7; -111 + 0000111 = +000000. При этом блока 15 формирования образцовых выходной код всего устройства соот- сигналов на вход АЦП 1 поступаветствует входному сигналу 640 мВ, ет ступенчатое напряжение (значения т.е, +101000000.

5 образцовых уровней напряжения выбиОднако, при работе устройства раются равными значениям уровней (и известного устройства) в реальных "идеального" ЦАП8, а их количество условиях (отличных от нормальных) зависит от вида корректируемой погпоявляется дополнительная составляю" 10 решности и задается конструкцией щая инструментальной погрешности блока 17 например, для коррекции

ЦАП 8 и усилителя 6 разности. Поэ- погрешности смещения нуля устройсттому коррекция с помощью ПЗУ 9 теря- ва необходимо всего лишь одно образет эффективность, т,е. не полная цовое напряжение, равное нулю, для компенсация погрешности и в резуль- . 15 коррекции дифференциальной нелинейтате значительно (в несколько раз) ности — большее количество уровней). возрастает общая погрешность анало- Установка очередного уровня образ" го-цифрового преобразования. цового напряжения сопровождается раДля коррекции дополнительной сос- зовым запуском устройства аналоготавляющей инструментальной погреш- 2р цифрового преобразования (сигнал ности в устройство введено ОЗУ 12, "Внутр. запуск"), формированием кода в ячейки которого в режиме коррек- на выходе цифрового сумматора 11, чиции нелинейности характеристики кван- сленно равного значению дополнительтования заносятся коды этой погреш- ной погрешности, и записью его (сигности. В рамках условий рассмотрен- 25 нал "запись") в ячейку ОЗУ 12, адрес ного выше примера можно допустить, которой соответствует коду АЦП 1 что разрядные уровни ЦАП 8 0к, Ок, ; в данном такте коррекции. При постуи 0 при наличии дополнитель- плении сигнала "Конец преобр." счеткз k4 ной погрешности изменились и стали - вертого выхода блока 10 управления равны: М „ = 125 — 2 = 123 мВ; Ик = З0 разрешается установление следующего

258 — 4 = 254 мВ; 0 = 508 — 8— уровня образцового напряжения. После — 500 мВ U = -1020 + 16 = -1004 мВ формирования последнего образцового к (изменение исходного значения смещения напряжения происходит остановка рануля усилителя 6 разности положим боты блока 15. равным нулю). В ячейках ОЗУ 12 при Р р и м е р, Считаем, что на вход

35 этом должны храниться коды дополни- устройства подано не входное, à i-e о тельной погрешности в соответствии значение образцового напряжения 0; = с табл. 2. = 640 мВ, тогда в условиях влияния

При преобразовании входного сиг- дополнительной погрешности на выходе нала = 640 мВ получаются соответ- 4 цифрового сумматора 11 получим код, к ственно коды: АЦП 1: +101 АЦП равный сумме кодов АЦП,„р 7, ПЗУ 9 ср ° 4 мр

7: +0010001 (соответствующие разност- и ОЗУ 12 (код ОЗУ 12 равен нулю, так ному сигналу М -(У + И ) = 640 — как предварительно дно обнуляется), к, кз

-(123 + 500) = 17 MB) . код ПЗУ9: т.е. +0010001-111+0 = +0001010. Этот

-111 (см. табл. 1) и код ОЗУ 12: 45 код соответствует с противоположным

-1010 (табл. 2), После сложения ко- знаком дополнительной погрешности дов АЦП 7 ПЗУ 9 и ОЗУ 12 в цифро- 10 мВ (табл. 2), инверсию знака ковом сумматоре 11 получим код млад- да +1010 погрешности можно произвоших разрядов +00.10001-111-1010 = дить, например, при выполнении опера= +0000000 а полный код аналого-ци- ции сложения в рабочем режиме или

Э 50 фрового преобразования при этом ра-. . непосредственно при записи кода в вен +1010000000, что соответствует ОЗУ 12. Затем полученный код погрешц = 640 мВ, ности (+1011) записывается в ячейку к

Определение и запись в ячейки ОЗУ 12 с адресом +101, что соответОЗУ 12 кодов дополнительной погреш- ствует коду АЦП р 1.

55 ности производятся в режиме коррек- Блок 15 формирования, образцовых ции нелинейности характеристики кван- сигналов работает следующим образом. тования. В этот режим устройство пере- Переключатели 19-21 в узле 16 заводится установкой переключателя 13 в дания режимов устанавливаются в ис10Формула изобретения

5 139 хоцное положение. При переходе в режим коррекции переключатель 20 переводится в противоположное положение, при этом прекращается процесс обнуления ОЗУ 12 и через элемент И 24 триггер 25 устанавливается в едини.:— ное состояние. При этом дублируется сигнал запрета на первом управляющем генераторе 26 импульсов. Далее одновременно с переключателем 13 переключается переключатель 19, тем самым обеспечивается обнуление двоичного счетчика 23 и подается сигнал разрешения (логический "0") на первый вход элемента ИЛИ 22 и второй управляющий вход генератора 26 в блоке 17. На выходе блока 15 устанавливается первое значение уровня образцового напряжения О, . После такой подготовки блок 15 формирования образцовых сигналов готов к. работе, При нажатии переключателя 2 1 триггер 25 запускает генератор 26, которьп обеспечивает периодический запуск устройства аналого- цифрового преобра" зования. В каждом такте коррекции сигналом "Конец преобразования" с чет вертого выхода блока 10 через элемент

ИЛИ 22 производится запись кода до". полнительной погрешности (кода АЦП,„

7) в ОЗУ. 12, а. затем изменяется состояние двоичного счетчика 23 на единицу и устанавливается следующее значение образцового уровня Ц(,.формиру" емое источником 18 опорных напряжений. Сигнал переполнения счетчика 23 через элемент И 24 переводит триггер

25 в единичное состояние, останавливая тем самым генератор 26. На этом заканчивается процесс коррекции и после перевода переключателей 13 и 19 в исходное состояние устройство аналого-цифрового преобразования готово к работе в реальных условиях.

Возможны другие варианты построения блока 17, обеспечивающего иные алгоритмы получения образцовых напряжео ний 0; .

Предлагаемое устройство выгодно отличается от известного устройства по точности. Известное устройство обеспечивает преобразования входного сигнала с заданной точностью лишь в рамках тех услов пл, при которых инструментальные погрешности ЦАП 8 и усилителя 6 разности постоянны (как правило, нормальные или лабораторные условия) . Предлагаемое уст8093

6 ройство обеспечивает заданную точность при любых условиях окружающей среды, так как имеется возможность подстраиваться к их изменениям. Это преимущество проявляется тем сильнее, чем больше число разрядов аналого-цифрового преобразования.

1. Устройство аналого"цифрового преобразования, содержащее аналогоцифровой преобразователь и старших

15 разрядов, информационный вход которого объединен с входом элемента задержки, а управляющий вход соединен: с первым выходом блока управления,второй выход которого подключен к

20 управляющему входу регистра памяти, выходы которого соединены с соответствующими входами первой группы входов арифметико-логического устройства, а информационные входы объеди25 иены с соответствующими входами цифроаналогового преобразователя, постоянного запоминающего устройства и подключены к соответствующим выходам аналого- цифрового преобразователя

Э0 и старших разрядов, выход элемента задержки соединен с первым входом усилителя разности, выход которого соединен с информационным входом аналого-цифрового преобразователя млад- "

35 щих разрядов, управляющий .вход которого подключен к третьему выходу блока управления, четвертый выход которого соединен с управляющим входом

N-разрядного выходного регистра, 40 входы старших и разрядов которого подключены к соответствующим выходам арифметико-логического устройства, а выходы являются выходными шинами, о т л и ч а ю щ е е с я тем, что, 45 с целью повышения точности и увеличения быстродействия, в него введены цифровой сумматор, оперативное запоминающее устройство, переключатель, элемент ИЛИ и блок формирования образцовых сигналов, первый выход которого соединен с первым информационным входом переключателя, второй информационный вход которого является входной шиной, а управляющий вход объединен с первым входом блока фор5Б мирования образцовых сигналов и является первой управлякщей шиной, вхо ды обнуления и записи оперативного эапоминаницего устройства подключены

7 1398093 соответственно к второму и третьему выход источника опорного напряжения, выходам блока формирования образцо- входы которого соединены с соответвых сигналов, второй и третий входы - ствующими информационными выходами которого являются соответственно вто- счетчика импульсов, вход обнуления

5 рой и третьей управляют и шинами, которого объединен с первым управа четвертый вход соединен с четвер- ляющим входом генератора импульсов, тым выходом блока управления, вход первым входом элемента ИЛИ и подкоторого подключен к выходу элемен- ключен к выходу первого переключата ИЛИ, первый вход которого соеди- 1р теля, первый и второй входы которого нен с четвертым выходом блока форми- объединены соответственно с первыми рования образцовых сигналов, а вто- и вторыми входами второго и третьего рой вход яВляется шиной "Внешний sa- переключателей и являются соответпуск", входы N — Il младших разрядов ственно шинами логического нуля и выходного N-разрядного регистра объе- 15 единицы, выход второго ключа соедидинены с первыми информационными нен с первым входом элемента И и яввходами оперативного запоминающего ляется вторым выходом блока, третьим . устройства и подключены к соответ- выходом которого является выход элествующим N-n выходам младших разря- мента ИЛИ, второй вход которого oRдов цифрового сумматора, m входов 2р единен со счетным входом счетчика второй группы входов арифметико-логи- импульсов и является четвертым вхоческого устройства объединены с соот- дом блока, выход переполнения счетчиветствующими вторыми информационны- ка импульсов соединей с вторым вхоми входами оперативного запоминающе- дом элемента И, выход которого подво ° тт г о устройства. и подключены к соответ- 25 ключен к входу установки в 1 тригствующим выходам ш старших разрядов гера, прямой выход которого соедицифрового сумматора, первые N-и+ш нен с вторым управляющим входом гене!!ПИ входов которого подключены к соответ- ратора, а вход установки в 0 подствующим выходам аналого-цифрового ключен к выходу третьего переключатепреобразователя младших разрядов, 30 ля, выход генератора является четвервторые входы соединены с соответству- тым выходом блока. ющими выходами постоянного эапоминаю- 3. Устройство по п. 1, о т л ищего устройства, а третьи входы под- ч а ю щ е е с я тем, что арифметикоключены к соответствующим выходам логическое устройство выполнено на оперативного запоминающего устройства, „ элементе И, элементе ИЛИ и цифровом адресные входы которого подключены к сумматоре-вычитателе, первые инфорсоответствующим выходам аналого-ци- мационные входы которого являются фрового преобразователя и старших соответствующими входами первой групразрядов, второй вход усилителя раз- пы входов арифметико-логического устности соединен с выходом цифроанало- 4О ройства, вход первого разряда втор гового преобразователя, выход пере- информационных входов цифрового сумключателя соединен с входом линии матора-вычитателя объединен с первым входом элемента ИЛЬФ и является первым

2. Устройство по п. 1, о т л и входом второй группы входов арифметич а ю щ е е с я тем, что блок форми- 45 ко-логического устройства, вход вторования образцовых сигналов выполнен рого разряда вторых информационных на источнике опорного напряжения,. входов цифрового сумматора-вычитатепервом, втором и третьем переключа- ля соединен с выходом элемента И, телях, элементе ИЛИ, счетчике импуль- первый вход которого объединен с втосов, элементе ИУ триггере и генерато- 50 р входом элемента ИЛИЭ с упраюре импульсов, выход которого являет- щим входом цифрового сумматора-вычитася четвертым выходом блока, первым, теля и является входом второго разрявторым и третьим входами которого яв- да второй группы входов арифметиколяются соответственно управляющие логического устройства, выходами ковходы первого, второго и третьего торого являются соответствующие выхо55 а-вычитателя. переключателей, а первым выходом— ды цифрового сумматора-вычитат

1398093

Таблица1

Адресные Коды основ Аналоговые эквиваленты коды нык погреш погрешностей, мВ костей

Соответствие идеальному уровню

ЦЛП8, мв

-011

+001

128

+010

+010

256

-001 +011

-3+2=-1

128+256=384

-100

+100

512

+101

-3+(-4)=-7

+2+(-4)=-2

-3+2+ (-4) =--5

-010

-101

+111

Таблица 2 т Аналоговые эквиваленты по Соответстви грешностей, мВ му уровню

4 ресные Коды дополнитель е идеальнокоды ных,погрешностей ЦАП 8, мВ

128

-0010

Ф001

Ф010

256

" -01 00 е

-0110

-2+(-4)=-6

128+256=384

1011 100

512

Ф101

-2+ (-8) =-10

128+512=640

-4+(-8)=-12

-2+(-4)+(-8)=14

256+512=768

+110

128+256+512=896

-1000

-1010

-11GG

-111G

128+512=640

256+512=768

128+256+512=896

1398093

Составитель Ю, Спиридонов

Техред М.дидык Корректор Л. Пилипенко

Ф»

Редактор П, Гереши

Заказ 3768

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4