Цифроаналоговый преобразователь с самоконтролем

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 10 А1 (5D 4 H 03 М 1/6 6

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М ABTOPCXOIVl Y CBNQETFJlbCTBV.(21) 4123547/24-24 (22) 26.06.86 (46) 23.05.88. Бюл. Р 19

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (72) Г.Ф.Фролов, В.В.Замчевский, С.И.Золотарев и А.Д.Кутафьев (53). 681.325 (088.8) (56) Авторское свидетельство СССР

В 1112547, кл. Н 03 М 1/66, 1981.

Авторское свидетельство СССР

11 809541, кл. Н 03 M 1/66, 1977. (54) ЦИФРОАНАЛОГОВЫИ ПРЕОБРАЗОВАТЕЛЬ

С САМОКОНТРОЛЕМ.(57) Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые. Цель — повышение достоверности и точности метрологического контроля. Устройство содержит элемент 1 допускового контроля, сумматор 2, блок 3 коммутации эталонных величин, первый и второй переключатели 4 и 5, шину 6 "Режим работы", блок 7 развертки кодов, входные шины 8 преобразуемого кода, входную шину 9 сигнала развертки, элемент

НЕ IQ. Цель достигается локализацией источника погрешности с точностью до разряда и обнаружением всех возможных отклонений весов разрядов от их идеальных значений эа счет испольlO зования избыточных измерительных кодов с отрицательным основанием. 1 ил. ФР

ЧФ 1

1398100

Изобретение относится к вычислиз ельной технике и цифровой измерительной технике и может быть исполь- ! зовано для преобразования цифровых величин в аналоговые.

Цель изобретения — повышение достоверности и. точности метрологичес" ного контроля.

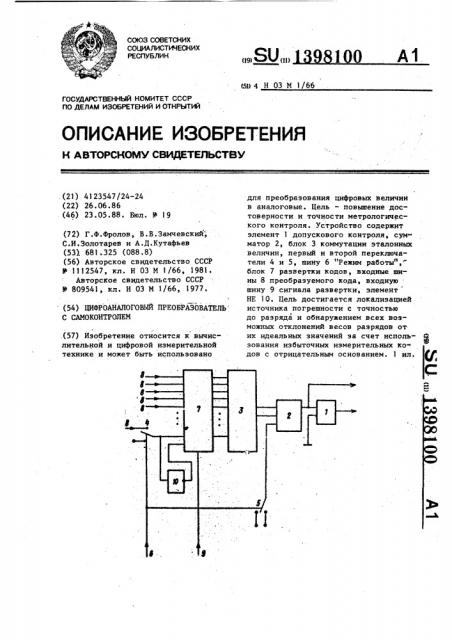

На чертеже приведена функциональная схема цифроаналогового йреобраэо" вателя (ЦАП) с самоконтролем, ЦАП с самоконтролем содержит элеь1ент i допускового контроля, сумма". тор 2, блок 3 коммутации эталонных величин, первый 4 и второй 5 переключатели, шину б "Режим работы", блок 7 развертки кодов, входные шины

8 преобразуемого кода, входную шину

9 сигнала развертки и элемент НЕ 10» 2р

Устройство работает следующим образом.

Преобразуемый код является известным измерительным кодом с отрицательнЬпк иррациональным основанием, веса 25 разрядов которого задаются рекурентным соотношением

О, при Х à О;

1, при Ж = О; 30

1, при Й = 1;

М (Х-р-1) ф (2-1), при 2 1. где р = 0,1,3,5.. ., — параметр избыточного измерительного кода. 35

При р=1 веса р-чисел Фиббоначи порождают следующий ряд:...,13,-8,5, -3,2-1,1,0.

Получение различных форм представления р-чисел Фиббоначи производится 40 путем последовательного применения сПецифических операций, называемых сверткой и разверткой, являющихся взаимно инверсными.

Различие в результатах данных операций для р-чисел Фиббоначи с положительными и отрицательными основаниями заключается в том, что при выполнении операции свертки в первом случае происходит процесс замены двух единиц в (1-1) -м и (1-р-1)-м разрядах на единицу в 1-м разряде и раз-. вертки в обратном порядке, а во вто.", poì случае выполнение свертки заклю чается в замене единиц (1+1)-го и ((+р+1)-ro разрядов на единицу в

1 -м разряде, развертка происходит в обратном порядке, что определяет инверсное включение блока развертки . кода в данном устройстве.

Устройство работает в двух режимах — цифроаналогового преобразования и метрологического контроля.

В режиме цифроаналогового преобразования переключатели 4 и 5 находятся в положении, укаэанном на чертеже. Преобразуемый избыточный измерительный код с отрицательным основанием поступает по входным шинам на информационные входы блока 7 развертки кодов, который включен инверсно и работает в режиме регистра памяти.. Инверсное включение блока 7 заключается в том, что п-й старший разряд преобразуемого кода поступает на информационный вход первого, младшего разряда блока 7, (п-1)-й разряд преобразуемого кода поступает на ин— формационный вход второго разряда блока 7 и т.д. Младший разряд преобразуемого кода поступает через первый переключатель на информационный вход п-ro разряда блока 7.

Выход первого разряда блока 7 подключен к входу старшего n-ro pasряда блока 3, выход второго разряда блока 7 подключен к входу (n-1)-го разряда блока 3 и т.д. Выход (п+1)ro дополнительного разряда блока 7 не задействован. На первом выходе блока 3 формируется сигнал, равный сумме тех весов разрядов с положительными весами, которые соответствуют единичному состоянию соответствующих разрядов преобразуемого кода.

На втором выходе блока 3 формируется сигнал той же полярности, равный сумме тех весов разрядов с отрицательными весами, которые соответствуют единичному состоянию соответствующих разрядов преобразуемого кода;

Сигнал с первого выхода блока 3 поступает на вход суммирования сумма»тора 2, а сигнал с второго выхода блоблока 3 — на первый вход вычитания сумматора 2> на второй вход вычитания которого в режиме цифроаналогового преобразования через второй переключатель 5 поступает нулевой сиг" нал. На выходе сумматора 2 формируется аналоговый сигнал, соответствующий преобразуемому коду.

В режиме метрологического контроля по входным шинам 8 поступает нулевой код. Переключатели 4 и 5 находятся на первом этапе контроля в положе"

3 139810 нии, указанном на чертеже. На информационный вход (n+1)-ro разряда блока 7 с выхода элемента НЕ 10 поступает логическая единица. Сигнал развертки кода, поступающий по шине

9, приводит к появлению логических единиц на выходах n-ro и (п-1)-го разрядов блока 7 которым вследствии инверсного включения соответствуют 10 веса +1 и -1 и соответствующие величины сигналов на первом и втором выходах блока 3. На выходе сумматора 2 и на входе элемента 1 допускового контроля должен при этом сохраниться 16 нулевой сигнал.

При отклонении реальных весов одного или обоих разрядов от эталонных величин, превышающем допустимое; на выходе элемента 1 допускового 20 контроля появляется сигнал логической единицы. После подачи по шине 9 следующего импульса происходит развертка (n-1)-ro разряда и в этом состоянии еще раз проверяют нахождение 25 выходного сигнала сумматора 2 в заданном диапазоне допустимых отклонений от нулевой величины и т.д,,пока не будут выполнены все возможные операции развертки. Теоретически суще- 30 ствуют отклонения весов разрядов, которые не будут обнаружены на первом этапе контроля, HagpHMep, при выполнении условий !4 х/ Ih i+1, где .111 — отклонение (погрешность) i-ro разряда, i+1 - отклонение (х+1)-го, разряда.

Для обнаружения всех возможных отклонений разрядов необходимо, чтот бы каждый разряд участвовал, как ми-. 4п нимум, в двух операциях развертки s качестве i-ro и (i+2)-ro разрядов.

Это позволяет локализовать отклонив- шийся разряд с точностью до одного разряда, что повышает эффективность 45 контроля всего устройства. Поэтому после первого этапа контроля, заключающегося в последовательной развертке кода числа, соответствующего нулевой выходной величине логические единицы только в (n+1)- ì не задействованном разряде блока 7),осуществляется второй этап контроля, на котором по шине 6 подается сигнал, пе-. реводящий переключатели 4 и 5 в полбжение, противоположное укаэанному на чертеже. При этом на информационный вход и-го разряда блока 7 через переключатель 4 подается логическая

4 единица, а на остальных информационных входах блока 7, включая (n+1)-й, присутствует сигнал логического нуля, Через переключатель 5 на второй вход вычитания сумматора 2 подается сигнал, равный весу младшего разряда. По сигналам развертки, поступающим по шине 9, осуществляется полная развертка исходного кода, соответствующего числу ")". При соответст-. вии весов разрядов их идеальным значением на выходе сумматора 2 и в этом случае должен быть нулевой сигнал вследствие наличия указанного дополнительного сигнала на втором вычитающем входе сумматора 2.

Таким образом, при использовании двух кодовых комбинаций, соответствующих числам "0" и "1", производится контроль линейности выходной характеристики ЦАП и локализация "неверных" весов разрядов. При этом одновременно возможен и контроль дрейфа нуля при подаче на вход ЦАП кодо" вой комбинации, эквивалентной числу

"0", на первом этапе контроля до подачи первой команды на развертку кода.

Формула изобретения

Цифроаналоговый преобразователь с самоконтролем, содержащий блок развертки кодов, управляющий вход которого является входной шиной сигнала развертки, блок коммутации эталонных величин, первый выход эталонных ве-, личин нечетных, начиная с младшего, разрядов которого подключен к входу суммирования сумматора, выход которого является выходной шиной, о тл и ч а ю шийся тем, что, с целью повышения достоверности и точности метрологического контроля, введены элемент допускового контроля, первый и второй переключатели, элемент НЕ, а блок развертки кодов выполнен (и+1)-разрядным, где и— число разрядов преобразуемого кода, прн этом информационный вход старmего (и+1)-ro разряда блока развертки кодов подключен к выходу инвертора, и-й информационный вход блока развертки кодов объединен с входом инвертора и. подключен к выходу первого переключателя, первый информа" ционный вход которого является шиной первого младшего разряда преобраэуе! 398I

Составитель В,Першиков

Редактор П.Гереши 7ехред А.Кравчук Корректор С.Черни

Заказ 2608/57 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 мого кода, второй информационный вход подключен к шине потенциала логической единицы, управляющий вход объединен с управляющим входом вто5 рого переключателя и является шиной

"Режим работы", информационные входы блока развертки кодов с первого по (n-lf""й являются входными шинами преобразуемого кода соответственно с и-го старшего разряда по второй, выходы блока развертки кодов с первого по и-й подключены к входам блока коммутации эталонных величин с n-ro входа эталонной величины старшего разря; В

00 6 да по первый соответственно, выход эталонных величин четных разрядов подключен к первому входу вычитания сумматора, второй вход вычитания которого подключен .к выходу второго переключателя, первый информационный . вход которого подключен к шине эталонного сигнала, соответствующего весу младшего разряда, при этом выход сумматора подключен к первому входу элемента допускового контррля, второй вход которого подключен к шине нулевого потенциала, выход является контрольной . выходной шиной.