Преобразователь код-временной интервал

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано для одновременного формирования нескольких различных по скважности сигналов с широтноимпульсной модуляцией, необходимых для управления многоприводным устройством, например роботом, с большим числом степеней свободы. Цель изобретения - расширение функциональных возможностей устройства - достигается путем увеличения числа одновременно преобразуемых различных кодов в соответствующие временные интервалы . Для этого в устройство дополнительно введены дешифратор 8 и триггеры 9 по числу каналов преобразования с функциональными связями, показанными на чертеже. Кроме того, устройство содержит генератор 1 импульсов, счетчик 2 импульсов, задатчик 3 кода, запоминающий блок 4, элементы 2И-ИЛИ 5, второй счетчик 6 импульсов, блок 7 сравнения кодов. Введение новых элементов и связей позволяет одновременно преобразовывать несколько различных кодов в соответствующие временные интервалы без увеличения по числу каналов преобразования всех содержащихся в устройстве элементов . 2 3. п. ф-лы, 4 ил. SS (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5g 4 Н 03 К 7/08, 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

A(àнаох

Выход

Канал

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4050558/24-21 (22) 07.04.86 (46) 07.06.88. Бюл. № 21 (72) Э. В. Ахмадеев, Д. В. Беляев и В. П. Симонов (53) 621.374 (088.8) (56) Авторское свидетельство СССР № 1168061, кл. Н 03 К 7/08, 18.04.83.

Авторское свидетельство СССР № 738143, кл. Н 03 К 11/00, 1977. (54) ПРЕОБРАЗОВАТЕЛЬ КОД вЂ” ВРЕМЕННОЙ ИНТЕРВАЛ (57) Изобретение относится к импульсной технике и может быть использовано для одновременного формирования нескольких различных по скважности сигналов с широтноимпульсной модуляцией, необходимых для управления многоприводным устройством, например роботом, с большим числом степе„„SU„„1401589 A 1 ней свободы. Цель изобретения — расширение функциональных возможностей устройства — достигается путем увеличения числа одновременно преобразуемых различных кодов в соответствующие временные интервалы. Для этого в устройство дополнительно введены дешифратор 8 и триггеры 9 по числу каналов преобразования с функциональными связями, показанными на чертеже.

Кроме того, устройство содержит генератор 1 импульсов, счетчик 2 импульсов, задатчик 3 кода, запоминающий блок 4, элементы

2И-ИЛИ 5, второй счетчик 6 импульсов, блок 7 сравнения кодов. Введение новых элементов и связей позволяет одновременно преобразовывать несколько различных кодов в соответствующие временные интервалы без увеличения по числу каналов преобразования всех содержащихся в устройстве элементов. 2 з. п. ф-лы, 4 ил.!

40!589

Изобретение относится к импульсной технике и может быть использовано для одноир мои ного формирования нескольких различных по скважности сигналов с широтноим иульсной модуляцией, необходимых для управления многоприводным устройством, например роботом, с большим числом степеней свободы.

Целью изобретения является расширение функциональных возм ож ностей устройства путем увеличения числа одновременно преобразуемых различных кодов в соответствующие временные интервалы.

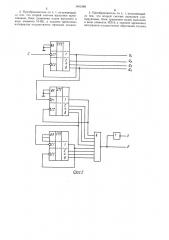

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — схема счетчика импульсов; на фиг. 3 — 4 временные диаграммы работы преобразователя.

Преобразователь код — временной интервал содержит генератор 1 импульсов, счетчик 2 импульсов, задатчик 3 кодов, запоминающий блок 4, элементы 2И-ИЛИ 5, счетчик 6 импульсов, блок 7 сравнения кодов, дешифратор 8, триггеры 9, при этом выход генератора импульсов соединен со счетными входами счетчиков 2 и 6, младшие разряды счетчика 2 соединены с адресными входами дешифратора 8, запоминающего блока 4 и задатчика 3 кодов, информационные входы которого соединены с входными шинами, а выходы — с первыми входами элементов 2И-ИЛИ 5, вторые входы которых соединены с прямым выходом старшего разряда счетчика 2, соответствующий инверсный выход которого соединен с третьими входами элементов 2И-ИЛИ 5, четвертые входы которых соединены с выходами запоминающего блока 4, а выходы — с информационными входами счетчика 6, выходы которого соединены с информационными входами запоминающего блока 4 и входами блока 7 сравнения кодов, выход которого соединен с входом запрета записи запоминающего блока 4 и информационными входами триггеров 9, счетные входы которых соединены с соответствующими выходами дешифратора 8, а выходы — с выходными шинами.

Генератор импульсов может быть выполнен на основе инверторов с резистивно-емкостными связями или с кварцевой стабилизацией, например, на микросхеме

К 155ЛН1.

Счетчик 2 импульсов выполнен суммирующим и может быть выполнен на микросхемах К 155ИЕ5, К 155ЛА2 и К 155ЛН1, например по схеме, приведенной на фиг. 2.

Задатчик 3 кодов и запоминающий блок 4 выполнены многорегистровыми, с числом регистров, соответствующим количеству одновременно преобразуемых различных кодов, а разрядностью регистров, равной разрядности входных кодов, например, на микросхемах запоминающих устройств К 155РУ2, выходы которых подключены через нагрузочные резисторы к источнику питания, а

2 к информационным входам подключены дополнительные инверторы, например, на микросхемах К 561ЛН2 для компенсации инвертирования ими выходного сигнала.

Элементы "И-ИЛИ могут быть выполнены на микросхемах К 599ЛКЗ и их количество определяется разрядностью входных кодов.

Счетчик 6 может быть выполнен на основе микросхемы К 155ИЕ7, блок 7 сравнения кодов может быть выполнен на основе микросхем К 155ЛА2 или К 155ЛЛ1, в зависимости от представления входной информации прямыми или инверсными кодами.

Дешифратор 8 может быть выполнен на основе микросхемы К 155ИДЗ, а триггеры 9— на основе микросхем К 155ТМ2.

При использовании в устройстве элементов, выполненных на других типах микросхем, для сохранения работоспособности устройства необходимо соблюдать следующие временные соотношения. Сигнал с выхода блока 7 должен поступать на вход запрета записи запоминающего блока 4 раньше изменения информации на его информационных входах, а на информационные входы триггеров — позже изменения сигналов на выходах дешифратора 8, в противном случае в устройстве нарушится соответствие выходных сигналов входным.

Преобразователь код — временной интервал работает следующим образом.

Генератор 1 импульсов вырабатывает импульсы, поступающие на вход суммирующего счетчика 2, младшие разряды Q ..., 0 которого с тактовой частотой генератора 1 импульсов осуществляют последовательный перебор 2 адресов многорегистрового задатчика 3 кодов, многорегистрового запоминающего блока 4 и дешифратора 8. На выходах Q„, ..., Я,„задатчика 3 кода и запоминающего блока 4 в каждый такт частоты устанавливается информационный код того канала преобразования, адрес которого в данный такт определяется значениями младших разрядов Q„, ..., Я,„счетчика 2. На одном из выходов Q„, ..., Я„дешифратора 8, соответствующем каналу преобразования, адрес которого в данный такт установлен на его адресных входах А„, ..., A, появляется импульс отрицательной полярности, который устанавливает соответствующий триггер 9 в состояние, определяемое уровнем сигнала на его информационном входе. С прямого P и инверсного Р выходов старшего разряда счетчика 2, подключенных к вторым и третьим входам N элементов 2И-ИЛИ 5, в течение первых 2 тактов генератора 1 импульсов поступают соответственно единичный и нулевой уровни сигналов. Поэтому в течение указанных тактов на выходы элементов 2И-ИЛИ 5, т. е. на входы D,, ..., Р„ предварительной установки счетчика 6, поступают информационные коды с выходов

1401589

20

Формула изобретения

3

Q,..., Q< задатчика 3 кодов и не проходят коды с выходов (,)„, ..., (,)„запоминающего блока 4. Счетчик 6 изменяет значение поступающего на входы Р„, ..., Рн кода на единицу младшего разряда в течение каждого из 2 " тактов генератора 1 импульсов. Причем, при задании на входной шине временных интервалов прямыми кодами счетчик 6 выполнен вычитающим, а при задании обратными кодами — суммирующим.

С выходов Q, ..., Q счетчика 6 измененный код поступает на информационные входы D,, ..., ..Ри запоминающего блока 4, куда происходит его запись при условии отсутствия запрещающего нулевого уровня сигнала на его входе запрета записи Ч„.

Блок 7 сравнения кода с постоянным числом вырабатывает этот нулевой уровень сигнала на своем выходе при равенстве уровней сигналов на выходах Q,;..., Q„ счетчика 6 единичному уровню в случае задания временных интервалов прямыми кодами и нулевому— в случае задания обратными кодами. Кроме того, сигнал с выхода блока 7 сравнения кода с постоянным числом поступает на информационные входы триггеров 9, что при задании ненулевой длительности временного интервала по какому-либо каналу позволяет установить триггер 9, соответствующий этому каналу, в единичное состояние при обращении по адресу этого канала в течение первых 2 тактов цикла преобразования.

Для последующих 2 (2 "— 1) тактов уровни сигналов на прямом P и инверсном Р выходах счетчика 2 изменяют свои значения на противоположные. Поэтому, в эти последующие такты на входы Р,, ..., Рн предварительной записи счетчика 6 через элементы

2И-ИЛИ 5 поступают информационные коды с выходов Q,, ..., Q и запоминающего блока 4 и не проходят коды с выходов Q,, ..., Qq задатчика 3 кодов.

С выходов Q,, ..., Я» счетчика 6 повторно измененный код поступает на информационные входы D,, ..., Р запоминающего блока

4, куда он и записывается при условии отсутствия запрещающего сигнала на входе V„

Таким образом, информационный код любого канала преобразования, хранящийся в запоминающем блоке 4, в такты обращения по адресу этого канала изменяется на единицу младшего разряда в каждый такт до тех пор, пока не станет равным коду на вход ных шинах 1Р, ..., NP, соответствующему вре менному интервалу нулевой длительности.

С этого момента и до начала нового цикла преобразования на выходе блока 7 сравнения кодов с постоянным числом в такты обращения по адресу данного канала устанавливается нулевой уровень сигнала, запрещающий изменение информационного кода в запоминающем блоке 4 и позволяющий установить в нулевое состояние триггер 9, соответствующий этому каналу преобразо4 вания. Так продолжается до тех пор, пока не закончатся эти 2 (2" — 1) такты. А затем ровни сигналов на прямом P и инверсном Р выходах счетчика 2 вновь становятся соответственно единичным и нулевым. На выходы элементов 2И-ИЛИ 5 поступают информационные коды с выходов Q,..., Q задатчика 3 кодов, и начинается новый цикл преобразования кодов во временные интервалы. Таким образом, длительность цикла преобразования кода во временной интервал составляет 2 . 2" тактов. Дискрет преобразования составляет 2 тактов. Максимальная длительность временного интервала, которую можно задать, составляет 2 (2" — 1) тактов.

Введение в преобразователь код — временной интервал новых элементов и связей позволяет повысить функциональные возможности устройства, т. е. одновременно преобразовывать несколько различных кодов в соответствующие временные интервалы без увеличения по числу каналов преобразования всех содержащихся в устройстве элементов.

1. Преобразователь код — временной интервал, содержащий генератор импульсов, выход которого подключен к входу первого счетчика, задатчик кодов, информационные входы которого соединены с входными шинами, а выходы подключены к первым входам элементов 2И-ИЛИ, к другим входам которых подключены выходы запоминающего блока, информационные входы которого соединены с выходами второго счетчика, блок сравнения кодов, выход которого подключен к одному из входов триггера, отличающийся тем, что, с целью расширения функциональных возможностей устройства путем увеличения числа одновременно преобразуемых различных кодов в соответствующие временные интервалы, в него дополнительно введены дешифратор и триггеры по числу каналов преобразования, причем прямой выход старшего разряда первого счетчика соединен с вторыми входами элементов 2И-ИЛИ, а инверсный — с третьими, четвертые входы которых соединены с выходами запоминающего блока, а выходы — с информационными входами второго счетчика, счетный вход которого подключен к выходу генератора импульсов, а выходы — к входам блока сравнения кодов, выход которого соединен с входом запрета записи запоминающего блока и информационными входами триггеров, выходы которых соединены с выходными шинами, а счетные входы — с выходами дешифратора, входы которого соединены с адресными входами задатчиков кодов и запоминающего блока и выходами младших разрядов первого счетчика.

1401589

2. Преобразователь по п. 1, отличающийся тем, что второй счетчик выполнен вычитающим, блок сравнения кодов выполнен в виде элемента И-НЕ, а задание временных интервалов осуществлено прямыми кодами.

3. Преобразователь по п. 1, отличающийся тем, что второй счетчик выполнен суммирующим, блок сравнения кодов выполнен в виде элемента ИЛИ, а задание временных интервалов осуществлено обратными кодами.

1401589

I l

° ° а ° сУ сГ Т пнаишаьэ кроют

1401589

Составитель Е. Борзов

Редактор H. Гунько Техред И. Верее Корректор И. Эрдейи

За каз 2540/54 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

С »

М с ъ Ь» с с»:ь

М с»с4 ь % . ь 1 сз ть

Ъ с .д Оа

Ч

9 ей

» с и

%»» с»

Ю» ъ 3 3