Устройство для контроля коммутационной системы

Иллюстрации

Показать всеРеферат

изобретение относится к технике связи и обеспечивает непрерывный контроль коммутационной системы. Устр-во содержит блок сравнения 1, входные мультиплексоры 2, выходные мультиплексоры 3, блоки 4 коммутации, блок 5 памяти, регистр 6 управления , блок 7 тестирования и контролируемую коммутационную систему (ККС) 8 Счетчик времени в ККС 8 вырабатывает тактовые импульсы, синхронизирующие работу всех блоков устр-ва. Непрерывность контроля ККС 8 обеспечивается за счет введения блоков 4-7. Ноясняется работа блоков 1, 4, 5, 7, 8. 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5g 4 Н 04 М 3/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4119573/24-09 (22) 26.06.86 (46) 07.06.88. Бюл. № 21 (72) В. П. Чуркин (53) 621.396.664 (088.8) (56) Авторское свидетельство СССР № 543199, кл. Н 04 М 3/22, 1975.

Авторское свидетельство СССР

¹ 907864, кл. Н 04 М 3/22, 1982.

„„Я0„„1401639 A 1 (54) УСТРОИСТВО ДЛЯ КОНТРОЛ Я

КОММУТАЦИОННОЙ СИСТЕМЫ (57) Изобретение относится к технике связи и обеспечивает непрерывный контроль коммутационной системы. Устр-во содержит блок сравнения 1, входные мультиплексоры 2, выходные мультиплексоры 3, блоки 4 коммутации, блок 5 памяти, регистр 6 управления, блок 7 тестирования и контролируемую коммутационную систему (ККС) 8

Счетчик времени в ККС 8 вырабатывает тактовые импульсы, синхронизирующие работу всех блоков устр-ва. Непрерывность контроля ККС 8 обеспечивается за счет введения блоков 4 — 7. Поясняется работа блоков 1, 4, 5, 7, 8. 6 ил.

1401639

Изобретение относится к технике связи и может использоваться в системах цифровой коммутации.

Цель изобретения — обеспечение непрерывного контроля коммутационной системы.

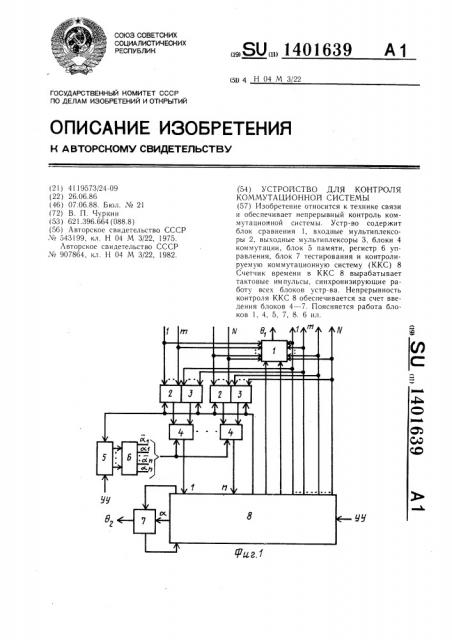

На фиг. 1 приведена структурная электрическая схема устройства контроля коммутационной системы; на фиг. 2 — структурная электрическая схема блока сравнения; на фиг. 3 — структурная электри ческая схем а блока коммутации; на фиг. 4 — структурная электрическая схема блока памяти; на фиг. 5 — структурная электрическая схема блока тестирования; на фиг. 6 — структурная электрическая схема контролируемой коммутационной системы.

Устройство содержит блок 1 сравнения, входные мультиплексоры 2, выходные мультиплексоры 3, блоки 4 коммутации, блок 5 памяти, регистр 6 управления, блок 7 тестирования, подключенный к контролируемой коммутационной системе 8.

Блок 1 сравнения (фиг. 2) содержит первый мультиплексор 1 — 1, блок 1 — 2 памяти, триггер 1 — 3, элемент 1 — 4 сравнения и второй мультиплексор 1 — 5.

Блок 4 коммутации (фиг. 3) содержит элементы И 4 — 1 и 4 — 2 и элемент ИЛИ 4-3.

Блок 5 памяти (фиг. 4) содержит блок

5 в 1 полупроводниковой памяти и элемент

И 5 -2.

Блок 7 тестирования (фиг. 5) содержит элемент 7--1 сравнения и регистр 7 — 2 сдвига.

Контролируемая коммутационная система 8 (фиг. 6) содержит элементы 8 — 1 срав;непия, регистры 8 — 2 сдвига, блоки 8 — 3 фиксации, счетчик 8 — 4 времени, выходные преобразователи 8 — 5 кода, блоки 8 — 6 памяти, блоки 8 — 7 сравнения кодов времени, распределитель 8- — 8 и блок 8 — 9 адресной памяти.

Устройство работает следующим образом.

Коммутация входящих и исходящих линий связи осуществляется с помощью блока 8 — 9 (фиг. 6) адресной памяти контролируемой коммутационной системы 8 (фиг. 1).

Блок 8 — 9 имеет ячейки памяти, закрепленные за входящими линиями связи. Номера ячеек памяти и входящих линий одинаковы.

В ячейки памяти записываются адреса исходяьцих линий, с которыми коммутируются соответствующие входящие линии. При коммутации линий связи в ячейки памяти блока 8 9 записывается также сигнал о = О, свидетельствующий об установлении соединений. При разъединении в каждую ячейку памяти блока 8 — 9 записываются адрес своей исходящей линии связи и сигнал

35 вает выдачу тестовой комбинации, записанной на регистре 7 — 2 сдвига (фиг. 5) блока тестирования, в те временные интервалы группового тракта (ГТ), которые обслуживаются ячейками блока 8 — 9, имеющими сигнал cx, = 1.

Таким образом, в групповой тракт коммутационной системы выдается тест из блока 7 тестирования в сопровождении адреса своей исходящей линии связи из блока 8 — 9 адресной памяти. Этот тест проходит через соответствующие устройства 8 — 8, 8 — 6, 8 — 5 (фиг. 6) коммутационной системы и выдается через соответствующий мультиплексор 3 на вход элемента И 4 — 2 (фиг. 3) блока 4 коммутации.

В это время на другой вход элемента

И 4 — 2 поступает сигнал с,= 1 из регистра 6 управления. Сигнал с ; = 1 пропускает тест через элементы И 4 — 2, ИЛИ 4 — 3, который далее проходит через регистр 8 — 2 сдвига, блок 8 — 3 фиксации времени (фиг. 6) и поступает на вход элемента 7 — 1 сравнения (фиг. 5) блока 7 тестирования. B элементе

7 — 1 производится сравнение кода сигнала теста, поступившего из блока 8 — 3, с кодом из регистра 7 — 2 сдвига ранее выданного теста. Это сравнение производится по сигналу и =1 из блока 8 — 9 адресной памяти.

Если сравнение произойдет, то работа соответствующих электрических цепей устройства для контроля коммутационной системы правильная, а если не произойдет, то блок 7 тестирования вырабатывает сигнал 9 = 1, который вместе с адресом входящей (исходящей) линии связи выдается в узел управления (УУ) коммутационной системы.

При коммутации входящих и исходящих линий связи сигнал х записывается не только в блок 8 — 9 адресной связи, но и в блок 5 памяти. Сигнал ос считывается затем на регистр 6 управления, с выхода которого уже поступают на элементы И 4 — 1 и 4 — 2 (фиг. 3) два сигнала сс, и .; . Если ск, = 1, то сс„= О. При с = 1 будет открыт элемент

И 4 — 2, пропускающий тест, поступающий через выходной мультиплексор 3 на элемент

ИЛИ 4 — 3, а если oc. = 0 (w = 1), то будет открыт элемент И 4 — 1, пропускающий код сигнала, который передается по соответствующей входящей линии и поступает из входного мультиплексора 2 на элемент ИЛИ

4 — 3. Блок 5 памяти имеет п ячеек, каждая из которых обеспечивает хранение сигналов са; (i = 1, 2, ..., п), считываемых и записываемых на регистр 6 управления одновременно, что обеспечивает управление сразу п блоками 4. Емкость устройства N = п- m линий связи.

В процессе коммутации линий связи сигнал <к поступает в блоки 5 и 8 — 9 из узла управления коммутационной системы 8.

При этом на вход блока 5 — 1 (фиг. 4) по1401639

После коммутации входящих и исходящих линий связи обеспечивается передача сигналов из входящих линий через входные мультиплексоры 2 и блоки 4 коммутации на входы регистров 8 — 2 сдига (фиг. 6), которые имеют m + 1 разрядов. Число m + 1 выбрано таким, чтобы была возможность хранить в течение одного цикла работы регистра 8 — 2 сдвига все m кодов коммутируемых сигналов предыдущего цикла и поочередно сравнивать их с помощью элемента

8 в 1 сравнения с последовательно поступающими из входного мультиплексора 2 кодами коммутируемых сигналов нового цикла, которые записываются на первый триггер регистра 8 — 2 сдвига. При этом на первом и (m+

+ 1)-м триггерах регистра 8 — 2 будут находиться соответственно новый и старый коды коммутируемых сигналов одного и того же

55 ступают: адрес А ячейки памяти, информация И, представляющая собой и сигналовя„, и сигналу,, обеспечивающий запись сигналов к; в соответствующую ячейку памяти блока 5 — 1. Сигнал р поступает через эле- 5 мент И 5 — 2 и обеспечивает в такт r записи занесение информации в блок 5 — 1. Такты г, считывания, г записи и адрес А считывания поступают из счетчика 8 — 4 времени коммутационной системы.

При тестировании электрических цепей устройства регистр 7 — 2 сдвига (фиг. 5) обеспечивает поочередную выдачу различных кодов (О, 1) сигналов теста. Тестирование производится непрерывно до тех пор, пока не будет произведена коммутация со- 1 ответствующих входящих и исходящих линий связи.

При установлении соединения в блок 5 памяти производится запись сигнала = О, т. е. одного бита информации для каждой 20 входящей линии связи. При этом ячейки памяти блока 5 закрепляются за m входящими линиями связи, обслуживаемыми каждым блоком 4 коммутации. Число разрядов в каждой ячейке равно числу блоков 4. Номера линий связи и блоков 4 коммутации совпадают соответственно с номерами ячеек памяти и разрядов в ячейках блока 5 памяти. Запись сигнала с = О в соответствующий разряд ячейки памяти блока 5 обеспечивает прохождение коммутируемых сиг- 3ц налов из входящей линии связи через блок 4 коммутации.

Считывание сигналов с из блока 5 памяти и проключение соответствующей входящей линии связи через входной мультиплексор 2 производится с помощью адреса ли- 35 нии 5 из счетчика 8 — 4 времени коммутационной системы 8. С помощью этого же адреса А обеспечивается проключение соответствующих исходящих линий с помощью выходных мультиплексоров 3 при тестировании 4о электрических цепей устройства. входа входного мультиплексора 2, например i-го.

Если полярность коммутируемого сигнала в i-й входящей линии связи изменилась. то коды коммутируемого сигнала i-й входящей линии, записанные на первом и (m +

+ 1)-м триггерах регистра 8 — 2, различны, что будет зафиксировано с помощью элемента 8 — 1 сравнения, который вырабатывает при этом сигнал у = 1. Если полярность сигнала в i-й линии не изменилась, то вырабатывается сигнал = О. С помощью сигнала х = 1 осуществляется запись в блок 8 — -3 фиксации времени нового кода сигнала i-u входящей линии, ранее записанного на первый триггер регистра 8 — 2 сдвига.

Новый код сигнала записывается в блок

8 — 3 фиксации времени вместе с кодом времени, поступающим из счетчика 8 — 4 времени (фиг. 6). Номер ячейки памяти, в которую записывается эта информация, также поступает из счетчика 8 — 4 времени. Этот номер соответствует адресу линии А, поступающему также в выходные и входные муль,типлексоры 2 и 3 и в блок 5 памяти. Число ячеек памяти в блоке 8 — 3 фиксации времени и их номера соответствуют m входящим линиям связи обслуживаемым соответствующим входным мультиплексором 2.

Счетчик 8 — 4 времени обеспечивает выработку тактовых импульсов, которые синхронизируют работу всех блоков устройства.

С помощью тактовых импульсов производится циклическое считывание информации из блоков 8 — 3 фиксации времени и выдача ее в ГТ, по которому она поступает в соответствующие блоки устройства. Через ГТ передается код коммутируемого сигнала, код времени, фиксирующий момент времени поступления сигнала в коммутационную систему, и адрес входящей линии, из которой поступил сигнал. Адрес входящей линии А поступает в блок 8 — 9 адресной памяти и в блок 1 сравнения (фиг. 1, 6), код сигнала— в блок 8 — 9 и в блок 7 тестирования. Код времени проходит через блок 8 — 9 и поступает в распределитель 8 — 8. Аналогично код времени проходит и при тестировании электрических цепей устройства.

Каждая ячейка памяти блоков 8 — 3 фиксации времени считывается в определенном интервале времени работы ГТ (фиг. 6) . В этом же интервале производится трансформация (замена) адреса входящей линии А, на адрес исходящей линии А„, с помощью блока 8 — 9 адресной памяти, т. е. по адресу

А,„производится считывание пз блока 8--9 адреса А„„, который поступает в распределитель 8 — 8. С помощью распределителя. представляющего собой дешифратор, производится распределение коммутируемых сигналов и их кодов времени по блокам 8- -6 памяти. Распределение сигналов осушеcTH .«1401639 ется путем дешифрации старших разрядов адреса A Младшие разряды этого адреса используются для определения номера ячейки памяти блока 8 — 6, в которую записывается информация. Блоки 8 — 6 памяти имеют по m ячеек, номера которых соответствуют номерам исходящих линий, обслуживаемых соответствующими выходными преобразователями 8 — 5 кода. Информация (код времени) из ячеек памяти блоков 8 — 6 считывается циклически с помощью сигналов из счетчика времени 8 — 4 и выдается на входы блоков 8 — -7, а адрес исходящей линии связи, который соответствует номеру считываемой ячейки памяти блока 8 — 6, и код сигнала выдаются в выходные преобразователи 8-5 кода.

Код времени, поступающий из блоков Ь—

6 памяти, сравнивается в блоке 8 — 7 сравнения кодов времени с кодом времени, поступающим из счетчика 8 — 4 времени. При сравнении этих кодов времени в выходные преобразователи 8 — 5 кода поступают сигналы d = 1, которые обеспечивают распределение с помощью преобразователей 8 — 5 кодов коммутируемых сигналов, в исходящие линии связи. Если коды времени в блоках

8 — 7 различны, то вырабатываются сигналы d = О, которые запрещают выдачу сигналов в исходящие линии.

Контроль электрических цепей коммутационной системы после коммутации входящих и исходящих линий связи осуществляется с помощью блока 1 сравнения (фиг. 1 и 2). При этом коммутируемые сигналы из входящих линий поступают на входы первого мультиплексора 1 — 1, который пропускает нх в блок 1 — 2 памяти с помощью адреса входящей линии А из ГТ коммутационной системы. Этот же адрес А „обеспечивает также с помощью тактов считывания г„и записи r вначале считывание предыдущей информации (кода сигнала) из блока 1 — 2 памяти и запись ее на триггер 1 — 3, а затем запись нового кода сигнала в эту же ячейку памяти блока 1 — 2.

Коды сигналов, передаваемых по исходящим линиям, поступают на входы второго мультиплексора 1 — 5 и далее с помощью адреса исходящих линий А», проходят на элемент 1 — 4 сравнения. На другой вход элемента 1 — 4 сравнения поступает код сигнала с триггера 1 3. Адреса А и А, являются адресами скоммутированных между собой линий связи, через которые проходят одни и те же сигналы. Эти сигналы сравниваются с помощью элемента 1 — 4 сравнения.

Коммутируемые сигналы, переда ваем ые

IIo входящим линиям, проходят через коммутационную систему 8 и выдаются затем в исходящие линии с задержкой t . Время задержки t> обеспечивается (реализуется) с помощью блока 1 — 2 памяти, т. е. при появлении сигнала на входящей линии связи он записывается в блок 1 — 2, а ровно через цикл работы ГТ коммутационной системы этот сигнал появится на выходе коммутационной системы 8, и тогда он поступит через второй мультиплексор на вход элемента 1 — 4 сравнения, а на другой вход этого элемента

1 — 4 поступит этот же сигнал, считанный из блока 1 — 2 памяти и записанный на триггер 1 — 3. Если коммутируемые сигналы будут различны, по сигналу сс из блока 8 — 9 адресной памяти коммутационной системы поступит из элемента 1 — 4 сравнения сигнал

9, = 1, который свидетельствует б том, что устройство неисправно.

Формула изобретения

Устройство для контроля коммутационной системы, содержащее блок сравнения, входные мультиплексоры, к информационным входам которых подключены входящие линии, выходные мультиплексоры, информационные входы которых являются выходами для подключения информационных выходов контролируемой коммутационной системы, а управляющие входы входных и выходных мультиплексоров являются входами для подключения первого управляющего выхода контролируемой коммутационной системы, отличаюи(ееся тем, что, с целью обеспечения непрерывного контроля коммутационной системы, введены последовательно соединенные блок памяти и регистр управления, блоки коммутации, первый и второй входы каждого из которых соединены с выходами соответствующих входных и выходных мультиплексоров, а третий и четвертый входы соединены с соответствующими выходами регистра управления, блок тестирования, входы и выходы которого являются входами и выходом для подключения служебных выходов и служебного входа контролируемой коммутационной системы, при этом выходы

45 блоков коммутации являются выходами для подключения информационных входов контролируемой коммутационной системы, управляющие входы входных и выходных мультиплексоров соединены с информационным входом блока памяти, информационные входы входных H выходных мультиплексоров соединены с соответствующими входами блока сравнения, управляющие входы которого являются входами для подключения второго и третьего управляющих выходов контролируемой коммутационной системы.

1401639

Из бпла Из di.3

Из л,4 рз & 7

Составитель А. Сеселкин

Редактор А. Шандор Техред И. Верес Корректор О. Кравцова

Заказ 2541/56 Тираж 660 Подпис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 415

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4