Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Цель изобретения - повьппение точности установки выходной частоты. Синтезатор содержит опорный г-р 1, частотно-фазовый детектор (ЧФД) 2, ,К8-триггер (Т) 3, делитель 4 частоты, зл-т И 5, интегрирующее звено 6, фильтр нижних частот, управляемый Г-р 8. Введены ЧФД 9,.эл-ты И 10 и 11, эл-ты ИЛИ 12 и 13, зл-т 14 задержки , Т 15 со счетным входом RS-T 16, ЧФД 16, ЧФД 2 и 9 включают эл-ты НЕ 17 и 18, эл-ты И 19 и 20. Работа синтезатора разбивается на два этапа: грубая подстройка и точная подстройка . При установке RS-T 16 в единичное состояние наступает второй этап работы, при котором размыкается цепь грубой подстройки частоты (з л-т 5 закрьшается) и замыкается цепь точной подстройки (открьгоается эл-т И 11). Формируемые г-ром 8 сигналы через эл-т 11, Т 15 и эл-т 12 будут поступать на вход делителя. Исключается жесткая синхронизация импульсов на первом и втором входах ЧФД 2, на выходе которого вырабатывается сигнал ошибки, подстраивающий г-р 8 к требуемой частоте fj с точностью до фазы, {{ножитель 2 в этом выражении обусловлен наличием Т 15, которьй согласует грубый и точный режимы по коэф. умножения частоты г-ра i. 1 з.п. ф-лы, 1 ил.

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„Я0„„1403367 A 1 (1) 4 Н 03 L 7/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,,::

Н ABTOPCKOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4164090/24-09 (22) 18.12.86 (46) 15.06.88. Бюл. 9 22 (7l) Новгородский политехнический институт (72) С.Н.Бритин, A.Т.Трофимов и П.А.Трофимов (53) 621.373.42 (088,8) (56) Авторское свидетельство СССР

У 1077057,кл. Н 03 Т 7/18,26.03.81.

Авторское свидетельство СССР

У 1.198739,кл. Н 03 В 19/00,21.11.83. (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике. Цель изобретения — повьппение точности установки выходной частоты.

Синтезатор содержит опорный г-р 1, частотно-фазовый детектор (ЧФД) 2, MRS-триггер (Т) 3, делитель 4 частоты, эл-т И 5, интегрирующее звено 6, фильтр нижних частот, управляемый г-р 8. Введены ЧФД 9,.эл-ты И 10 и

11, эл-.ты ИЛИ 12 и 13, эл-т 14 задержки, Т 15 со счетным входом RS-Т

16, ЧФД 16, ЧФД 2 и 9 включают эл-ты

HF. 17 и 18, эл-ты И 19 и 20. Работа синтезатора разбивается на два этапа: грубая подстройка и точная подстройка. При установке RS-Т 16 в единичное состояние наступает второй этап работы, при котором размыкается цепь грубой подстройки частоты (эл-т

5 закрывается) и замыкаетея цепь .точ" ной подстройки (открывается эл-т И

11). Формируемые r-ром 8 сигналы через эл-т 11 Т 15 и эл-т 12 будут поступать на вход делителя. Исключается жесткая синхронизация импульсов на первом и втором входах ЧФД 2, на выходе которого вырабатывается сигнал ошибки, подстраивающий г-р 8 к требуемой частоте f< = 2КГ „ с точностью до фазы. 11ножитель 2 в этом выражении обусловлен наличием Т 15, кото.— рый согласует грубый и точный режимы по коэф. умножения частоты г-ра 1.

I з.п. ф-лы, 1 ил. !

1403367

Изобретение относится к радиотех нике и может быть использовано í ра:диоприемных и радиопередающих устройствах и в системах обработки информации.

Целью изобретения является повышение точности установки выходной частоты.

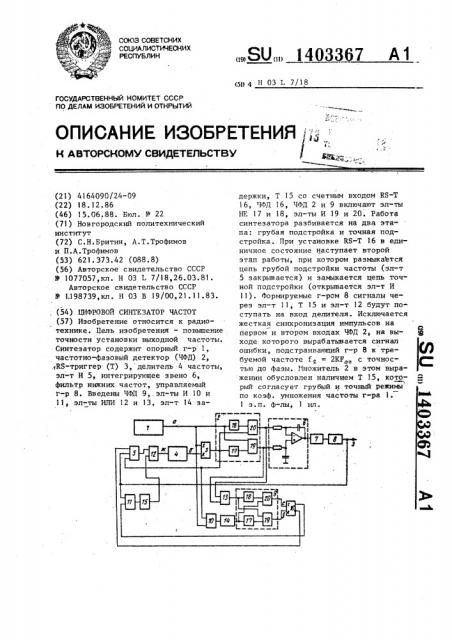

На чертеже представлена электри" ческая структурная схема цифрового, синтезатора частот.

Цифровой синтезатор частот содер-, жит опорный генератор 1, первый час тотно-фазовый детектор (ЧФД) 2, перВый RS-триггер 3, делитель 4 частоты, первый элемент И 5, интегрирующее, звено 6, фильтр 7 нижних частот, уп равляемый генератор 8, второй ЧФД 9, второй элемент И 10, третий элемент 20 ,;И 11, первый элемент ИЛИ 12, второй элемент ИЛИ 13, элемент задержки 14, триггер с счетным входом 15, второй

RS-триггер 16. Лри этом первый и второй ЧФД. 2 и 9 включают первый.эле- 25

10 первый элемент И 5 подан разрешающий потенциал. Требуемое значение выходной частоты с выхода управляемого генератора 8 определяется коэффициентом деления делителя 4 и частотой

Р „ опорного генератора 1, который вырабатывает колебания типа "меандр" со скважностью g = ?. Первый RS-триггер 3 по переднему фронту устанавливается в единичное состояние и открывает первый элемент И 5. Через первый элемент И 5 и первый элемент ИЛИ

12 импульсы управляемого генератора

8 поступают на вход делителя 14, который осуществляет счет К импульсов и переключает первый RS-триггер 3 в нулевое состояние. Длительность сигнала на выходе первого RS-триггера 3 определяется частотой управляемого мент НЕ 17, второй элемент HF. 18, первый элемент И 19, второй элемент

И 20.

Цифровой синтезатор частот работает следующим образом. 30

Работа цифрового синтезатора час:тот условно разбивается на два эта-! па. Н 1 первом этапе осуществляется груба подстройка частоты, а на вто ром — точная.

В режиме грубой подстройки после переключения частоты выходного сиг нала второй RS-триггер устанавливается в нулевое состояние, при котором третий элемент И 11 закрыт, а на генератора 8 и коэффициентом деления

К делителя 4. Если частота управляемого генератора 8 отличается от заданной, задний фронт выходного импульса первого RS-триггера 3 оказывается смещенным относительно середины периода опорного колебания. При этом на выходе первого ЧФД 2 вырабатывается сигнал ошибки соответствующего знака, который интегрируется интегрирующим звеном 6, через фильтр 7 поступает на вход управляемого генератора. 8, изменяя его частоту, таким образом, чтобы скомпенсировать сигнал ошибки. Теоретически этому условию удовлетворяет частота f

=" 2KFonБл1годаря синхронизации между сигналами опорной частоты и сигналами с выхода делителя 4 перестройка управляемого генератора 8 в рассматриваемом режиме осуществляется со скоростью, пропорциональной величине сигнала рассогласования на выходе первого ЧФД 2, что обеспечивает высокое быстродействие цифрового синтезатора частот.

Используемая в этом режиме жесткая синхронизация приводит к ошибкам,максимальное значение f „, которых может достигать одного дискрета формируемой сетки частот 5 f „ Р „ . Первый этап подстройки частоты осуществляется до тех пор, пока частота выходного сигнала отличается от заданной более чем на один дискрет. В этом случае длительность сигнала ошибки 1 превышает пороговое значение с которое рассчитывается исходя из значения минимального значения выходной частоты f< „,„.

Сравнение сигнала ошибки с порогом осуществляется с помощью второго ЧФД

9, на первый вход которого поступает опорный сигнал„сформироваHHbIH с помощью второго элемента И 10 и элемента задержки 14 (с = „) из сигналов опорного генератьра 1 и первого

RS-триггера 3. На второй вход второго ЧФД 9 поступают через второй элемент ИЛИ 13 сигналы с выходов первого ЧФД 2. Пока происходит подстройка частоты Го, ><„, = с, второй ЧФД 9 формирует импульсы на первом выходе, которые поддерживают второй RS-триг! 403367

rep !6 в нулевом состоянии, при котором цепь автоподстройки частоты замкнута. Как только длительность сигнала ошибки становится меньше пороговой оы с о„, второй ЧФД 9 начинает формировать импульсы на втором

-вьгходе, которые устанавливают второй

RS-триггер 16 в.единичное состояние.

Второй ЧФД 9, работающий па описанному алгоритму, может быть реализован как первый ЧФД в виде двух цепей из последовательно. включенных первого элемента НЕ 17, первого элемента И !9,последовательно включенных второго элемента HF. 18 и второго элемента И 20 со связями, указанными на фиг.l.

При установке второго RS-триггера

16 в единичное состояние наступает второй этап цифрового синтезатора частот, при котором размыкается цепь грубой подстройки частоты (первый элемент И 5 закрывается) и замыкается цепь точной — фазовой автоподстройки частоты (открывается третий элемент И 11). Формируемые управляемым генератором 8 сигналы через третий элемент И ll, триггер со счетным входом 15 и первый элемент ИЛИ 12 непрерывно поступают на вход делителя 4. При этом исключается жесткая синхронизация импульсов на первом и втором входах фазового детектора 2, на выходе которого вырабатывается сигнал ошибки, вынуждающий подстраиваться управляемый генератор 8 и ,,требуемой частоте(fz = 2КГ и с точностью до фазы. Множитель 2 в этом выражении обусловлен наличием триггера с счетным входом 15, который позволяет согласовать грубый и точный режимы по коэффициенту умножения частоты опорного генератора. При переключении цифрового синтезатора частот на другую частоту этапы настройки повторяются.

Таким образом, введение указанных элементов значительно улучшает точность установки частоты при сохранении высокого быстродействия.

Формула изобретения

1. Цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор, первый частотноЙазо ый детектор, интегрирукщее зве- . но, фильтр ш <них частот, управляемьп» генератор и первый элемент И, а также последовательно соединенные де5 литель частоты и первый RS-триггер, при этом второй вход первого частотно-фазового детектора объединен с вторым входом первого элемента И и подключен к выходу первого RS-тригге-!

0 ра, à S-вход первого RS-триггера соединен с выходом опорного генератора и второй выход первого частотно-фазового детектора подключен. к второму входу интегрирующего звена, о т л и-!

5 ч а ю шийся тем, что, с целью повышения точности установки выходной частоты, между выходом опорного генератора и входом делителя частоты введены последовательно соединенные второй элемент И, элемент задержки, второй частотно-фазовый детектор, второй RS-триггер, третий элемент И,. триггер со счетным входом и первый элемент ИЛИ, а также введен второй

25 элемент ИЛИ, первый и второй входы и выход которого подключены соответственно к первому и второму выходам первого частотно-фазового детектора и второму входу второго частотно-фа" д0 эового детектора, второй выход которого соединен с S-входом второго

RS-триггера, инверсный выход второго

RS-триггера подключен ..к третьему вхо- . ду первого элемента И, второй вход

35 второго элемента И соединен с выходом первого RS-триггера, второй вход третьего элемента И подсоединен к выходу управляемого генератора, а второй вход первого элемента ИПИ подключен

40 к выходу первого элемента И

2. Синтезатор по п. 1, о т л и— ч а ю шийся тем, что первый и второй частотно-фазовый детектор выполнены идентично и каждый из них со45 держит последовательно соединенные первый элемент НЕ, первый элемент И, последовательно соединенные второй элемент НЕ и второй элемент И, второй вход второго элемента И объединен с входом первого элемента НЕ и явля50 — ° ется первым входом частотно-фазового детектора, второй вход первого элемента И объединен с входом второго элемента НЕ и является вторым входом частотно-фазового детектора, при

55 этом выход первого элемента И и выход второго элемента И являются соотв етс тв енно первым и вторым выходами часто тно-фаз ово ro детектора.