Преобразователь перемещения в код

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и предназначено для использования в преобразователях перемещений в код. Для повышения функциональной надежности в преобразователь, содержащий кодирующий элемент, считывающие элементы , расположенные по методу двойной щетки, блок усилителей-формирователей , четыре группы элементов И, элемент ИЛИ, пять элементов И, четыре инвертора, введены триггер, элемент ИЛИ. Если снимаемый с выхода младшего разряда блока усилителей-формирователей сигнал равен нулю, то на выход преобразователя проходят сигналы с опережающих считывающих элементов , если же он равен единице, то сигналы проходят с запаздывающих элементов. Перекоммутация сигналов осуществляется триггером, двумя группами элементов И, .одним инвертором и одной группой элементов ИЛИ. Состояние других выходов преобразователя определяется состояниями считывающих элементов нечетного основания. При единичном сигнале элемента младшего разряда сигнал на выходе преобразователя снимается с опережающих элементов , а при нулевом - с отстаю- . ил. «б (Л щих

СОЮЭ СОВЕТСНИХ

СОЭалистичесних

РЕСПУБЛИК (}9) (И) А1 (5}) 4 H 03 М 1/24

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ }ц, ЖИ цц-„, К ABTOPCHOIVIY СВИДЕТЕЛЬСТВУ. (21) 4073580/24-24 (22) 02.06.86 (46) 15.06.88. Бюл. В 22 (72) О.П.Малофей, Ю.И.Николаев, Н.И.Червяков, Н.И.Швецов и А.П.Болтков (53) 681.325 (088.8) (56) Авторское свидетельство СССР

}} 312289, кл. Н 03 M 1/26, 1968.

Авторское свидетельство СССР

Ф 384118, кл. Н 03 М 1/26, 1970. (54) ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ

В КОД (57) Изобретение относится к области автоматики и вычислительной техники и предназначено для использования в преобразователях перемещений в код.

Для повышения функциональной надежности в преобразователь, содержащий кодирующий элемент, считывающие элементы, расположенные по методу двойной щетки, блок усилителей-формирователей, четыре группы элементов И, элемент ИЛИ, пять элементов И, четыре инвертора, введены триггер, элемент

ИЛИ. Если снимаемый с выхода младшего разряда блока усилителей-формирователей сигнал равен нулю, то на выход преобразователя проходят сигналы с "опережающих" считывающих элементов, если же он равен единице, то сигналы проходят с "запаздывающих" элементов ° Перекоммутация сигналов осуществляется триггером, двумя группами элементов И, одним инвертором и одной группой элементов ИЛИ. Состояние других выходов преобразователя определяется состояниями считывающих элементов нечетного основания. При единичном сигнале элемента младшего разряда сигнал на выходе преобразователя снимается с "опережающих" элементов, а при нулевом — с "отстающих". 2 ил.

1403371 рожки.

В таблице приведен пример для оснований Р, =4, Р =3, P =5a

Рисунок дорожек преобразователя с кодом в СОК младших оснований наносится для значений двух соседних нулевых разрядов (как показано на фиг.2) — для четного P основания и нечетных, например, для Р =3.

В исходном состоянии, соответствующем нулевому положению кодирующего элемента 9, триггер 25 установлен в

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в преобразователях перемещений в цифровой код.

Целью изобретения является повышение функциональной надежности преобразователя.

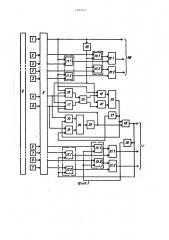

На фиг,1 представлена структурная схема преобразователя; на фиг.2 временные диаграммы, поясняющие работу преобразователя.

Преобразователь содержит считывающие элементы 1-7, блок 8 усилителей формирователей, кодирующий элемент 9, «5 группы 10-13 элементов И, элементы И

14 — 20, элементы ИЛИ 21-24, триггер

25, инверторы 26-29, выходные шины

30 и 31, на фиг.2 представлены сигналы 32 четного основания, 33 — нечетного при Р=Э (Р— основание), 34— нечетного при P=5 32-45 — условное расположение элемента 1 относительно дорожки четного основания.

Преобразователь работает следующим 25 образом.

Периодичность повторения единицы на выходе считывающего элемента 1 не нарушается во всем диапазоне кодовой шкалы, поэтому соответствующая этому элементу 1 дорожка младшего разряда четного основания, представляющая последовательность нулей и единиц, может быть использована в качестве синхронизирующей; Считывающие элементы 4 и 5 младших разрядов нечетного

35 основания, имеющих последовательность нулей и единиц, на границах периода, равного величине основания, формируют два рядом стоящих нуля для значения

40 остатка, равного основанию и нулю.

На каждом нечетном периоде повторение значения младшего разряда нечетного основания совпадает со значениями синхронизирующей дорожки, а на четных периодах является инверсным относительно той же синхронизирующей до- . нулевое состояние. Если сигнал, снимаемый с выхода блока 8, соответствующего элементу 1, равен О, то сигналы снимаются с элементов 2, если он равен 1, то с элементов 3. Перекоммутация элементов 2 и 3 осуществляется с помощью элементов И 10,1, 10.2, 11. 1, 11.2, элементов ИЛИ 22. 1, 22.2 и инвертора 28, при этом, если сигнал на выходе инвертора 28 равен логической единице, то сигналы снимаются по шинам 30 с элементов 2, если логическому нулю, то с элементов 3.

Пока элементы 4 и 5 находятся в области отсутствия рисунка на дорожке младшего разряда нечетного основания, сигнал с элемента 1 через элемент И

19,. .20, элемент ИЛИ 23 и открытый элемент И .18 проходит на выход и повторяет значение младшего разряда четного основания. При этом элемент И

19 открыт единичным потенциалом с инверсного выхода триггера 25, а элемент И 18 — единицей с выхода инвертора 29..

Когда элемент 1 окажется в точке

34 (фиг.2, ситуация 1), то на выходе инвертора 29 появляется запрещающий сигнал, который присутствует, пока элемент 1 не окажется в точке 39 (ситуация 1). В этот же момент времени на выходе элемента И 17 появляется сигнал "1", кбторый устанавливает триггер 25 в единичное состояние. В этот момент времени на выходе инвертора 29 появляется инвертированное значение сигнала, снимаемого с элемента 1, которое через открытый элемент И 18 подается на выход преобразователя. Когда элемент 1 окажется в точке 45 (ситуация 2), сигнал единицы появляется на выходе элемента И 16, который вернет триггер 25 в нулевое состояние и с шины 31, соответствующей младшему разряду нечетного основания, снимается прямое значение младшего разряда четного основания.

Если значение младшего разряда не- четного основания единица, то снимается результат с опережающих элементов 6, если нуль, то с "отстающих" элементов 7, результат преобразования снимается по шинам 30 и 31.

Преобразователь обладает высокой разрешающей способностью, выражающейся в исключении неразрешенных ситуаций в

3371

И, выход первого элемента ИЛИ соединен с входом первого инвертора, выход которого соединен с вторыми входами первого и шестого элементов И, выход пятого элемента И через четвертый ин-. вертор соединен с вторыми входами второй группы элементов И нечетного основания, первая группа выходов нечетного основания блока усилителей40

45 формирователей соединена с третьими входами первого и шестого элементов

И соответственно.

9101112131415

1 О 0 1 0 1

Р 0 1 0 0 0 0 1 0

0 1 0 0 1 0 0

0 0 1 0 1 0 0 з 140

Упрощение рисунка дорожки младшего разряда нечетного основания позволяет снизить требования на допуск при установке опережающих и "запаздывающих элементов данного разряда, что позволяет снизить и в ряде случаев вообще устранить погрешность отсчетов при переходе от одной, комбинации к другой за счет установки элементов 2-7, что ведет к повышению функциональной надежности преобразователя.

Формула изобретения

Преобразователь перемещения в код, содержащий кодирующий элемент, выполненный в системе остаточных классов, против дорожек которого расположены считывающие элементы по методу двойной щетки, выходы которых соединены с входами блока усилителей-формирователей, выход четного основания которого является выходом преобразователя и соединен с первыми входами первой группы элементов И четного основания, с первыми входами первого и второго элементов И, первая группа выходов четного основания блока усилителейформирователей соединена с вторыми входами первой группы элементов И четного основания, а вторая группа выходов соединена с первыми входами второй группы элементов И четного основания, вторые входы которых объединены выходы элементов И четного ос) нования первой и второй групп соединены с входами соответствующих элементов ИЛИ четного основания, выходы которых являются выходами преобразователя, первая группа выходов нечетного основания блока усилителей-формирователей соединена с первыми входами третьего и четвертого элементов И соответственно, выходы которых соединены с входами первого элемента ИЛИ, вторая группа выходов нечетного основания соединена с первыми входами; первой группы элементов И нечетного основания, а третья группа выходов

0 1 2 3 4 5 6 7 8

Р, 0 1 0 1 0 1 0 1 0

P 0 1 0 1 0 0 1. 0 1 нечетного основания соединена с первыми входами второй группы элементов

И нечетного основания, выходы элементов И нечетного основания первой и второй групп соединены с входами соответствующих элементов ИЛИ нечетного основания, выходы которых являются выходами преобразователя, выход пятого элемента И соединен с вторыми входами второй группы элементов И нечетного основания, а первый вход подключен к выходу первого инвертора, шестой и седьмой элементы И, второй и третий и четвертый инверторы, о т— л и ч а ю шийся тем, что, с целью повышения функциональной надежности преобразователя, в него введены второй элемент . ИЛИ, триггер, вход второго инвертора подключен к выходу четного основания блока усилителейформирователей, а выход соединен с вторым входом второй группы элементов

И четного основания, с первым входом седьмого элемента И и первым входом шестого элемента И, выход которого соединен с первым входом триггера, второй вход которого подключен к выходу первого элемента И, первый выход триггера соединен с вторым входом второго элемента И, а второй выход соединен с вторым входом седьмого элемента И, выходы второго и седьмого элементов И соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, с вторым входом третьего элемента И и через третий инвертор— с вторым входом четвертого элемента

i озз

1403371

Составитель М.Сидорова

Техред М. Ходанич

Корректор Л. Пилипенко

Редактор Н.Горват

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3005/56

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4