Генератор сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к устройствам , предназначенным для управления испытаниями объектов.Цель изобретения - повьшение точности генерирования сигналов. Генератор сигналов содержит регистр 1, счетчики 2-5, генератор 6 тактовых импульсов, генератор 7 белого шума, триггер 8, блоки 9, 10 памяти, коммутаторы 11, 12,цифроаналоговый преобразователь 13,элемент ИЛИ 14, элеме: ты И 15- 17. Поставленная цель достигается за счет введения элемента ИЛИ 14, элементов И 15-17. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (512 4 G 06 F 1/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

H ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4102017/24-24 (22) 31.07.86 (46) 23.06.88. Бюл. ¹ 23 (72) Е.А.Вейсов, В.Б.Дрыжак, В.И.Иванов, Н.В.Матюха, В.К.Меркулов и А.В.Парунов (53) 621. 325 (088. 8) (56) Авторское свидетельство СССР

¹ 756466, кл. G 06 F 1/02, 1976.

Авторское свидетельство СССР

¹- 1118990, кл. G 06 F 1/02, 1983. (54) ГЕНЕРАТОР СИГНАЛОВ (57) Изобретение относится к вычис„„Я0„„1405040 А 1 лительной технике, а именно к устройствам. предназначенным для управления испытаниями объектов. Цель изобретения — повышение точности генерирования сигналов. Генератор сигналов содержит регистр 1, счетчики 2-5, генератор 6 тактовых импульсов, генератор 7 белого шума, триггер 8, блоки 9, 10 памяти, коммутаторы 11, 12, цифроаналоговый преобразователь

13, элемент ИЛИ 14, элементы И 1517. Поставленная цель достигается за счет введения элемента ИЛИ 14, элементов И 15-17. 1 ил.

1 405040

Изобр»танце отн;. сит»я к вычислительной техник», я им»l!«!(к устрс йствам, предназначенным для управче— ния испытаниями объектов.

Цель изобретения — повышение точ— ности ген»рированця сигналов.

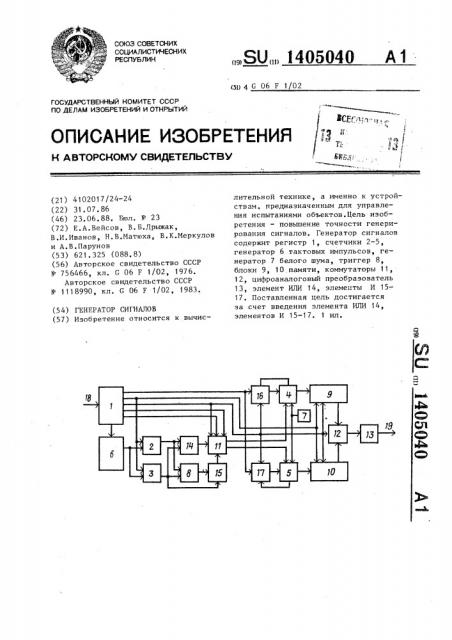

На чертеж» представлена структур ная схема генератора сигналог,.

Генератор сигналов содержит ре- 10 гистр 1, счетчики 2-5, генератор 6 тактовых импульсов, генератор 7 белого шума, триггер 8, блоки 9 и 10 памяти, коммутаторы 11 и 12, цифроаналоговый преобразователь 13, эле- !5 мент ИЛИ 14, элементы И 15-17, вход

18 управления генератором и выход

19 генератора.

Генератор работает следующим образом. 20

Работа генератора сигналов основана на формировании цифровых кодов для цифроаналогового преобразователя

13, которые поступают из блоков 9 и 10 памяти через коммутатор 12. При этом возможны два режима работы генератора: "случайный", что соответствует появлению логической "1" на выходе регистра 1, и "детерминированный, что соответствует появлению 30 ( логического "0 « на шестом выходе регистра 1. Подготовка генератора к работе осуществляется занесением цифровых кодов сигнала в блок 9 или

10 памяти занесением коэффициента пересчета в счетчики 2 и 3. Занесе(ц ние кодов может осуцествляться, например, из ЭВМ.

При появлении логической "1" на четвертом выходе регистра 1 разрешается работа генератора сигналов, при этом запускается генератор 6 тактовых импульсов, что приводит к появлению сигналов на выходах переполнения счетчиков 2 и 3, периоц которых опрецеля- 45 ется коэффициентом пересчета счетчиков. Так как один счетчик работает по переднему фронту сигнала, а другой по заднему фронту сигнала, импульсы на выходе счетчиков 2 и 3 не будут совпадать во времени, поэтому на выходе элемента И IH 14 формируется сумма двух частот, а на выхода элемента И 15-разность двух частот. Разностьдвух частот формируется следующим

55 образом: при появлении сигнала на выходе счетчика " триггер 8 сбрасывается по переднему фри нту в "0", по заднему фронту сигнала ня вых I/I» счетчикя 3 устянян.«ивяется в "1". При 3ТоМ сигнал со счетчика 3 HB выход элемента И 15 не проходит, тяк кяк триггер

8 установлен в логический "0", таким образом на каждый импульс сигнала со счетчика 2 происходит исключение импульса из сигнала со счетчика 3.

Под управлением сигнала ««а первом выходе регистра 1 коммутатор 11 переключает ня вь«ход счетчика 4 или 5 сигнал с выхода элем»нтя ИЛИ 14 или элемента И 15. Причем, если на пятом выходе регистра 1 находится логичесlI ll к ая 1, то с и г ««ял с эл»ме нт о в И 1 5 или ИЛИ 1 4 проходит и я сче тн ыи вход счетчика 4, я н а с ч е т ный вход счетчик а 5 прох оди т сигнал с второго выхода р е гис т р а 1, под управлением которого осу ще ствля е т ся запись новых кодов в блок 1 0 памяти . Счетчик 4 о суще с т вля ет и е ре б ор адресов блока

9 памяти и н а выходе блока 9 памяти формируется сигнал в цифровой форме .

Коммутатор 1 2 подключает вход цифроан яло го в ог о преобразователя к выходу блока 9 и амя 1 и . В э то время можно производить запись новых кодов в блок 1 0 памяти . При логическом "0 " н а пятом вых оде ре гис г ра 1 в блок 9 памяти произ в одит с я з апи с ь новых к одо в, а из блока памяти 1 0 — с -.и тыв ание . В режиме "Детерминированный " элементы И 1 6 и 1 7 з апр ещаю т прохождение сигнала с выхода переполнения с ч е т чик ов 4 и 5 н я вход з ан е с е ния сче т чик ов 4 и 5 . Таким о бр аз ом, о суще с твл яет ся полнь«й перебор адресов для блоков 9 и 1 0 пям я ти . В режиме

"Случайный" при н алич ии логической

" 1 " н а пятом вых оде регистра 1 н а вход з ан е сения счетчика 4 разрешается прохождение сигнала переполнения ,счетчика 4, а н я вход занесения счетчика 5 запрещается прохождение сиг н ал а переполнения, прич ем блок 9 памяти находится в режиме считывания, а блок

1 0 памяти — в режиме записи .

При в о з ник но ве н ии пе р » полн ен ия в сче тчик е 4 пр ои сходи т занесение к ода с генератора 7 белого шума в счетчик 4 . Таким образом, перебор кодов в блоке 9 памяти осуществляется со случайного н а чаль н ог о адреса, что эквивалентно заданию случ ай н ой н ач аль ной фазы си г н яла и случайной длины выборки . П ри возникновении " 0 " и а пятом выходе регистра 1 B блок

9 памяти прои сходит з я пи с ь и н фо рм я1405040 нин, а иэ блока IO памяти ванне случайного сигнала.

ИЛИ и три элемента И, при «м вход занесения второго счетчика подключен к информационному входу первого блока памяти и выходу выдачи информации регистра, выход выбора блока памяти подключен к входу управления счетом первого коммутатора, первым входом первого и второго элементов И, входам управления первого и второго блоков памяти и входу управления второго коммутатора, выход выбора режима регистра подключен к вторым входам первого и второго элементов И, третьи считыФормула из обречения

Составитель С.Курош

Техред М.Дидык Корректор В.Бутяга

Редактор В.Бугренкова

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3106/53

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Генератор сигналов, содержащий регистр, четыре счетчика, генератор тактовых испульсов, генератор белого шума, триггер, два блока памяти, два 10 коммутатора, причем вход регистра подключен к входу управления генератора, выход выбора направления которого подключен к входу управления пер. вого коммутатора, второй вход управ- 1 ления которого подключен к выходу строба регистра, вход занесения первого счетчика подключен к выходу выдачи информации регистра, выход разрешения запуска которого подкчючен к вхоцу пуска генератора тактовых импульсов, выход которого подключен к счетным входам первого и второ о счетчиков, информационный вход первого блока памяти подключен к инфор- 25 мационному входу второго блока памяти, выходы третьего и четвертого счетчиков подключены к адресным входам первого и второго блока памяти, выходы которых подключены к первому Зд и второму информационным входам второго коммутатора, выход которого подключен к выходу генератора, о тл и ч а ю шийся тем, что, с целью повышения точносги генерирова35 ния сигналов, в него введены элемент входы которых подключены соответственно к выходам переполнения третье,го и четвертого счетчиков, счетные входы которых подключены к первому и второму выходам первого коммутатора соответственно, выход генератора белого шума подключен к входам занесения третьего и четвертого счетчиков, управляющие входы которых подключены к выходам первого и второ—

ro элементов И, выход переполнения первого счетчика подключен к первому входу элемента ИЛИ и входу сброса триггера, вход установки которого, второй вход элемента ИЛИ и первый вход третьего элемента И подключены к выходу переполнения второго счетчика, выход триггера подключен к второму входу третьего элемента И, выход которого и выход элемента ИЛИ подключены к первому и второму информационным входам первого коммутатора.