Устройство отображения информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, к автоматизированным рабочим местам на основе микропроцессорных систем. Цель изобретения - повьшение производительности процессора за счет освобождения его от периодического опроса измерительных приборов . Процессор 1 в соответствии с программой, хранящейся в блоке 2 системной памяти, записьшает адреса источников отображаемых символов для каждого знакоместа в блок 8 памяти адресов. Синхронизатор 5 изображения задает номер текущего знакоместа , содержимое которого поступает с одного из блоков 4 ввода или из блока 7 памяти изображения через . ключ 9 на вход знакогенератора 6. При этом адрес источника отображаемого символа для текущего знакоместа поступает из блока 8 и распознается одним из блоков ввода либо дешифратором 10 знакоместа. Измерительные приборы подключаются к входам блоков ввода. Индикатор подключается к выходу знакогенератора 6. 4 ил. с Ё О 01 о | ел ф

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51)4 G 06 F 3/14

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ц::

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ (2 1) 40837 19/24-24 (22) 26.05.86 (46) 23.06.88. Бюл..№ 23 (71) Ленинградский институт авиационного приборостроения (72) В.Н.Соловьев, А.А.Лахманов, В.Н.Капичула, А.Г.Родионов, С.А.Шестопалов, К.С.Ярош, И.Е.Соловейчик и С.M.Ìîèñååâ (53) 681.325 (088.8) (56) Конов К.И. Электронно-цифровые генераторы сигналов телевизионных изображений. — М.: Связь, 1979, с. 41-56.

Кофрон Д. Технические средства микропроцессорных систем. — M.: Мир, 1983, с. 23-144.

Эстридж Ф.Д. и др. ЭВМ PCJZ фирмы

ИБМ, — ТИИЭР, 1984, ¹ 3, с. 103-114. (54) УСТРОЙСТВО ОТОБРАЖЕНИЯ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике, к автоматизированным

„„SU„„1405045 А1 рабочим местам на основе микропроцессорных систем. Цель изобретения — по- вышение производительности процессора за счет освобождения его от периодического опроса измерительных приборов. Процессор 1 в соответствии с программой, хранящейся в блоке 2 системной памяти, записывает адреса источников отображаемых символов для каждого знакоместа в блок 8 памяти адресов. Синхронизатор 5 изображения задает номер текущего знакоместа, содержимое которого поступает с одного из блоков 4 ввода или из блока 7 памяти изображения через. ключ 9 на вход знакогенератора 6.

При этом адрес источника отображаемого символа для текущего знакоместа поступает из блока 8 и распознается одним из блоков ввода либо дешифратором 10 знакоместа. Измерительные приборы подключаются к входам блоков ввода. Индикатор подключается к выходу знакогенератора 6. 4 ип.

1405045

Изобретение относится к вычислительной технике и может быть использовано при разработке автоматизированных рабочих мест отладки микрог роцессорной техники.

Цель изобретения — повышение про зводительности устройства за счет

< свобождения процессора от периоди° еского опроса измерительных прибо10 ов.

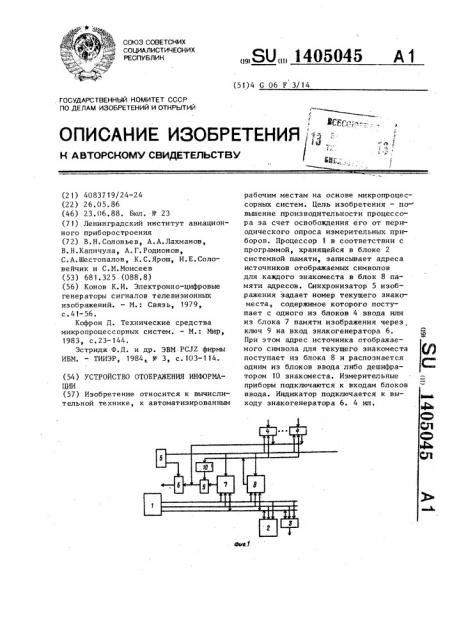

На фиг.1 показана структурная хема устройства; на фиг.2 — струкурная схема синхронизатора изобраения; на фиг.3 — структурная схема лока памяти изображения; на фиг.4— ариант формата иэображения.

Устройство содержит процессор 1, лок 2 системной памяти, блок 3 ввоа-вывода, блоки 4 ввода, синхрониатор 5 изображения, знакогенератор блок 7 памяти изображения, блок 8 амяти адресов, ключ 9, дешифратор

10 знакоместа.

Блок 2 системной памяти предназачен для хранения программ для проессора 1 и промежуточных данных, ырабатываемых и используемых процессором 1.

Синхронизатор 5 изображения предназначен для выработки синхроимпульсов и адресных сигналов, позволяющих периодически регенерировать информацию на экране устройства отображения.

Знакогенератор 6 преобразует код символа в последовательность бит, позво- 35 ляющих создать изображение символа на экране устройства отображения.

Блок 7 памяти изображения предназначен для хранения кодов символов, регенерируемых на экране устройства

40 отображения, блок 8 памяти — для хранения адресов устройств — источников кодов отображаемых символов.

Блоки 4 ввода предназначены для

45 передачи от измерительных приборов в микропроцессорную систему информации, которая должна быть отображена на экране устройства отображения.

Ключ 9 пропускает информацию с выхода блока 7 памяти изображения на вторую шину данных только в определенные моменты времени, Дешифратор 10 знакоместа определяет наличие на выходе блока 8 адреса блока 7 памяти изображения. 55

Синхронизатор 5 изображения содержит генератор 11 тактовых импульсов, счетчик 12 точе.к, счет шк 13 знакомест, счетчик 14 линий сж вола, счетчик 15 строк символов. Выходы 16- 19 синхронизатора 5 являются вторым выходом синхронизатора 5. Выход 18 соединен со старшим разрядом выхода счетчика 12. Выходы 18, 20 и 21 синхронизатора 5 являются первым выходом синхронизатора 5.

Блок 7 (8) памяти изображения содержит коммутатор ?2 адреса, элемент И 23, дешифратор 24, регистр 25, схему 26 памяти, элемент НЕ 27, регистр 28, шинный формирователь 29, вход †вых 30 являющийся информацион3 1, R B JISBO Ig HH ся управляющим входом, входы 32 и 33, являющиеся первым и вторым адресными входами, выход 34 °

Блок 7 памяти изображения одну половину времени обслуживает шину отображения (второй адресный вход), а другую половину времени — общую шину. Это определяется сигналом на линии старшего разряда входа 33, который в первой половине временного интервала отображения линии символа имеет значение "0", что обуславливает прохожцение информации с первого входа коммутатора 22 на его выход, блокировку элемента И 23 и регистра

28, запись информации с выхода схемы

26 памяти в регистр 25. Во второй половине временного интервала отображения линии символа сигнал на линии старшего разряда номера точки имеет значение "1", что обуславливает прохождение информации с второго входа коммутатора 22 на его выход, блокировку регистра 25, разрешение работы элемента И 23, запись информации с выхода схемы 26 памяти в регистр 28.

При обслуживании шины отображения блок 7 памяти изображения может выполнять только операцию чтения. При этом с входа блока 7 памяти изобра.жения через коммутатор 22 на вход схемы 26 памяти поступает адрес ячейки памяти, на выходе схемы 26 памяти появляется хранящийся в этой ячейке код символа, который загружается в регистр 25 и поступает на выход блока 7 памяти изображения.

При обслуживании общей шины адрес ячейки памяти с первого входа блока

7 через коммутатор 22 поступает на первый вход схемы 26 памяти. При появлении на линиях 32 выбора кода вибора блока 7 памяти изображения на

1405045 выходе дешифратора 24 появляется сигнал, разрешающий работу элемента И 23 и шинного формирователя 29. Сигнал записи с входа 31 при этом проходит через элемент И 23 на второй вход схемы 26 памяти. Сигнал чтения с входа 31 определяет направление прохождения информации через шинный формирователь 29. При выполнении операции чтения сигнал на входе элемента

И 23 имеет значение логического "0", а на линии чтения — логической " 1".

При этом информация с выхода схемы

26 памяти записывается в регистр 28 и с его выхода через шинный формирователь 29 поступает на информационный вход-выход блока ? памяти изображения. При выполнении операции записи с информационного входа-выхода блока 7 памяти изображения информация через шинный формирователь 29 поступает на третий вход схемы 26 памяти и записывается в выбранную ячейку этой схемы.

Блок 8 памяти работает аналогичным образом.

Все поле 35 экрана устройства отображения делится на строки 36 символов, каждая из которых состоит из знакомест 37. Используется несколько стандартных форматов поля 35 экрана, например 24 строки символов по 80 знакомест в каждой, 32 строки символов по 64 знакоместа в каждой и др. Каждое знакоместо состоит из линий 38 символа, каждая из которых состоит из точек 39. Используется несколько стандартных форматов разложения символа, например 8 линий символа по 8 точек в каждой, 9 линий .символа по 7 точек в каждой и др.

Изображение одной точки кодируется одним битом, который имеет значение " 1", если точка яркая, и "0", если точка темная. .Описание изображения точка за точкой передается на блок отображения с выхода знакогенератора 6. Процесс передачи изображения периодически повторяется.

Устройство работает следующим образом.

Процесс отображения информации на экране индикатора состоит из двух фаз: формирования изображения, выпол-. няемого под управлением процессора 1, и регенерации изображения, выполняе5

55 мой под управлением синхронизатора

5 из обр ажения.

Фаза формирования изображения заключается в заполнении ячеек блока 7 памяти изображения и блока 8 памяти адресов, что необходимо для создания изображения на экране индикатора. В этой фазе процессор 1, выполняя программу, хранящуюся в блоке 2 системной, памяти, заполняет все ячейки блока 8 памяти адресов и необходимые ячейки блока 7 памяти изображения. Б.блоке 7 памяти иэображения необходимо заполнить -только те ячейки, информация из которых будет отображаться на экране индикатора, т.е. те ячейки, которым соответствуют ячейки блока 8 памяти, хранящие адрес блока 7 памяти изображения.

Фаза формирования изображения состоит из чередующихся операций чтения и записи, выполняемых по общей шине.

Операции чтения используются для считывания программ из блока 2 системой памяти, операции записи — для заполнения блока 7 памяти изображения и блока 8 памяти. Выполнение операций чтения и записи одинаково для всех блоков, подключенных к общей шине.

Фаза регенерации изображения заключается в периодически повторяющейся передаче сформированного изображения " на индикатор. Синхронизатор 5 изображения в цикле последовательно перебирает все адреса строк символов, номера линий символа, адреса знакомест и номера точек. Номера линий символов и номера точек с первого выхода синхронизатора 5 изображения поступают на вход знакогенератора 6.

Адреса строк символов и адреса знакомест с второго выхода синхронизатора

5 изображения поступают на вторые адресные входьt блока 7 памяти изображения и блока 8 памяти адресов и на первые адресные входы каждого из

P блоков 4 ввода. Получив очередные адрес строки символов и адрес знакоместа, блок 8 памяти адресов выставляет на свой выход хранящийся в соответствующей ячейке адрес блока 4 ввода — источника кода символа, а блок 7 памяти изображения выставляет на свой выход код символа, хранящийся в соответствующей ячейке.

I I

Адрес с выхода блока 8 памяти поступает на второй адресный вход каждого из P блоков 4 ввода и на вход

1405045 дешифратора 10 знакоместа. Если адрес на выходе блока 8 соответствует адресу блока 7 памяти изображения, на выходе дешифратора 10 знакоместа появляется сигнал, открывающий ключ (9, и код символа с выхода блока 7 через ключ 9 поступает на вход знакогенератора 6. Если адрес на выходе блока 8 соответствует одному из P блоков 4 ввода, сигнал на выходе дешифратора 10 не появляется и ключ 9 остается закрытьи. В то же время на вход знакогенератора 6 поступает код символа с выбранного блока ввода, т.е. с того блока 4 ввода, адрес которого совпадает с адресом на выходе блока 8. Знакогенератор .6 преобразует код на входе, изображение символа точка за точкой выдается на выход знакогенератора 6.

20

Формула из обретения

Устройство отображения информации, 25 содержащее процессор, синхронизатор изображения, знакогенератор, блок системной памяти, блок ввода-вывода, P блоков ввода, блок памяти изображения, адресный выход процессора соеди- З0 нен с адресными входами блока системной памяти, блока ввода-вывода и первым адресным входом блока памяти изображения, информационный вход-выход процессора соединен с информационными входами-выходами блока системной памяти, блока ввода-вывода и блока памяти изображения, а управляющий выход соединен с управляющими входами блока системнои памяти, блока ввода-вывода и блока памяти изображения, первый выход синхронизатора иэображения соединен с вторым адресным входом блока памяти изображения, второй выход синхронизатора изображения соединен с входом синхронизации знакогенератора, о т л и ч а ющ е е с я тем, что, с целью повышения производительности процессора за счет освобождения его от периодического опроса измерительных приборов, в него введены ключ, блок памяти адресов, дешифратор знакоместа, причем адресный выход процессора соединен с первым адресным входом блока памяти адресов, информационный входвыход процессора соединен с информационным входом-выходом блока памяти адресов, управляющий вход которого соединен с управляющим выходом, первый выход синхронизатора изображения соединен с первыми адресными входами с первого по P-й блоков ввода и вторым адресным входом блока памяти адресов, выход которого соединен с вторыми адресными входами с первого по

P-й блоков ввода и адресным входом дешифратора знакоместа, выход которого соединен с управляющим входом ключа, выход которого соединен с выходами с первого по P-й блоков ввода и информационным входом знакогенератора, выход блока памяти изображения соединен с информационным входом ключа, выход знакогенератора является выходом видеосИгнала устройства, информационные входы с первого по P-й блоков ввода являются информационными входами устройства.

1405045

Составитель В.Бородин

Редактор В.Петраш

Корректор M. Мак симишинец

Техред M.Дидык

Тираж 704 Подписное

ВПИИПИ Гасударственного комитета СССР по делам изобретений и открытий!!3035, Москва, Ж-35, Раушская наб., д, 4/5

Заказ 3106/53

Производств ..ш -полиграфическое предприятие, г. Ужгород, ул. Проектная,